ルネサスエレクトロニクス株式会社により出願された特許

201 - 210 / 8,021

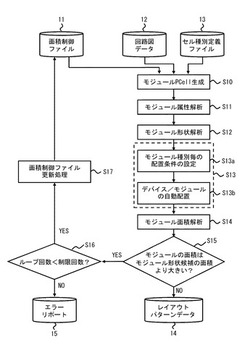

半導体装置の自動配置配線プログラム、自動配置配線装置及び自動配置配線方法

【課題】従来の方法では、アナログ・デジタル混載LSIのレイアウトの処理時間及び面積効率が悪化する問題があった。

【解決手段】本発明の自動配置配線プログラムは、回路設計情報からモジュールを抽出する第1処理(S10)と、モジュールに含まれる回路の属性を示すモジュール属性を設定する第2処理(S11)と、面積値を一定として縦横の寸法が異なる複数のモジュール形状候補を生成する第3処理(S12)と、上位モジュールの形状に適合するモジュール形状候補に対して回路素子を配置してレイアウトパターンを生成する第4処理(S13)と、を有し、第3処理(S13)では、第1回路属性のモジュールに対しては、行の高さ又は列の幅を縦横の寸法の変化単位とする複数のモジュール形状候補を生成し、第2回路属性のモジュールに対しては、縦横の寸法が連続的に変化する複数のモジュール形状候補を生成する。

(もっと読む)

半導体集積回路、動画像再生装置及び動画像データの逆方向再生方法

【課題】GOP境界付近での再生速度のばらつき抑制して滑らかな再生を実現すること。

【解決手段】時系列沿って再生される画像間の相関に応じて予測符号化された符号化画像データである複数のピクチャを時系列と逆方向に再生する場合に、当該複数のピクチャの圧縮及び伸張を行う処理単位であるピクチャ集合内の参照ピクチャのうち時系列で先頭の第1参照ピクチャと、当該第1参照ピクチャの次の参照ピクチャである第2参照ピクチャとを直接参照することにより復号可能な非参照ピクチャを復号する代わりに、逆方向で当該ピクチャ集合の次に再生されるピクチャ集合に属する参照ピクチャを復号するように制御する復号処理制御部を備える半導体集積回路。

(もっと読む)

半導体装置の不良解析方法ならびに不良解析装置および不良解析プログラム

【課題】半導体装置の不良解析技術において、解析成功率の向上や解析時間の短縮を図ることができる技術を提供する。

【解決手段】ショートしていると推測される一方の特定配線を特定(S103)し、その相手と推測される隣接配線の抽出(S104)をおこない、両配線間において電圧状態(論理状態)が異なる異電圧時間帯の算出(S107)をし、その異電圧時間帯で発生する発光現象の頻度を調査することにより、上記一方の特定配線に対して、どの隣接する配線がショートしているのかを短時間で確実に推定する。

(もっと読む)

半導体装置の製造方法

【課題】目視による外観検査を不要としながら、高精度に効率よく半導体ウエハの外観異常を検出する。

【解決手段】検査装置により、欠陥の検出感度を標準感度にして半導体ウエハの欠陥箇所を検出する。これにより、欠陥箇所F1,F2が検出される。続いて、検出感度を標準感度よりも検出感度が高い高感度に設定して、半導体ウエハの欠陥箇所を検出する。これにより、欠陥箇所F3〜F6(図中、点線で示す)が得られる。そして、標準感度にて検出された欠陥箇所と高感度にて検出された欠陥箇所とが重複している欠陥箇所において、高感度にて検出された欠陥箇所(欠陥箇所F6,F3)を欠陥箇所エリアと決定し、該欠陥箇所エリアに該当する半導体チップを不良チップとする処理を行う。

(もっと読む)

アナログ・デジタル変換装置

【課題】予測変換を行なう逐次変換方式のAD変換装置において、従来よりも予測精度を向上させる。

【解決手段】アナログ・デジタル変換装置1において、変化量算出部22は、変換部11によって入力信号のAD変換が実行される度に、新たに得られたAD変換結果と1つ前に得られたAD変換結果との変化量を算出する。変化量記憶部23は、前回までのAD変換結果に基づいて算出された所定数の変化量を記憶する。最大変化量抽出部24は、変化量記憶部23に記憶されている所定数の変化量のうちで最大変化量を抽出する。変換値予測部30は、抽出された最大変化量に基づいて、AD変換によって求める全ビットのうちの1または複数ビットの予測値を決定する。変換部11は、変換値予測部30によって予測値が決定された1または複数ビットを除く残余のビットの値を逐次比較方式によって決定する。

(もっと読む)

半導体装置の製造方法

【課題】半導体ウエハに対するウエハ工程がほぼ終了した段階で、ウエハの表面に表面保護テープを貼り付けた状態で、ウエハの裏面に対して、バックグラインディング処理を施し、その後、ウエハの裏面を真空吸着した状態で、表面保護テープ上に剥離用補助テープを貼り付けて、当該剥離用補助テープに張力を付与することにより、ウエハから表面保護テープを剥離することが広く行われている。

【解決手段】本願発明は、ウエハの裏面を真空吸着した状態で、表面保護テープ上に剥離用補助テープを貼り付けて、当該剥離用補助テープに張力を付与することにより、前記ウエハから前記表面保護テープを剥離する工程を含む半導体装置の製造方法に於いて、前記真空吸着に関する真空吸引系を前記ウエハの周辺部を担当する周辺吸引系と、前記ウエハの内部領域を担当する内部吸引系とを含むようにしたものである。

(もっと読む)

半導体装置

【課題】小面積化、低コスト化を図ることが可能な半導体装置を提供すること。

【解決手段】制御回路50は、I/O方向レジスタ5から出力される値を信号50aとして出力し、信号50aに応じて、プルアップ許可レジスタ4から出力される値とI/Oレジスタ6から出力される値とのいずれかを選択して信号50bとして出力する。AND回路13は、電源制御部20から出力される信号21と制御回路50から出力される信号50aとの論理和を演算して出力する。AND回路14は、電源制御部20から出力される信号21と制御回路50から出力される信号50bとの論理和を演算して出力する。トライステートバッファ16は、AND回路13および14から出力される値に応じて、電極19に接続される外部のデバイスを駆動する。したがって、レベル変換(AND)回路の数を削減することができ、半導体装置の小面積化、低コスト化を図ることが可能となる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビア層絶縁膜にビア用の孔を形成する工程において、シールリングのうちビア層絶縁膜に位置する部分に、導体を埋め込むための溝を形成しないで済むようにする。

【解決手段】ビア層絶縁膜40及び第2配線層絶縁膜50にはシール溝121が形成されている。また、エッチングストッパー層30には複数の孔31が形成されている。第2シール導体パターン120は、複数の孔31及びシール溝121に埋め込まれている。そして、エッチングストッパー層30は、シール溝121の底面に位置する部分が薄膜部32となっており、シール溝121が形成されていない部分と比較して薄くなっている。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】高速動作に対応可能とし、消費電力を抑制可能とし面積も抑制可能とする出力回路の提供。

【解決手段】出力回路は、差動入力段10と出力増幅段20と増幅加速回路70を備え、増幅加速回路70は、入力対が入力端子1と出力端子2に夫々接続された差動対171、172と、第5の電源端子E5と前記差動対の出力対間にそれぞれ接続された負荷素子対174、175を備え、差動対171、172の入力電位差によって、差動入力段10の第2のカレントミラー40の入力が接続する第4のノードN4への電流供給を制御する第1の電流源回路176と、差動入力段10の第1のカレントミラー30の出力が接続する第1のノードN1への電流供給を制御する第2の電流源回路178を含む。

(もっと読む)

エミュレーション装置、エミュレーション方法、エミュレーションシステム

【課題】必要なトレースデータを確実に転送することができるエミュレーション装置、エミュレーション方法、及びエミュレーションシステムを提供すること

【解決手段】CPUシミュレーション部110は、CPUの処理をシミュレーションする。フィルタ部140は、CPUシミュレーション部110が出力するトレースデータをフィルタリング条件に基づいてフィルタリングする。転送部152は、フィルタリング結果を転送する。フィルタ部152は、フィルタリング結果の転送量と、転送部152の最大転送容量から定まる比較基準と、の比較を行う。フィルタ部140は、転送部152の比較に応じて前記フィルタリング条件を変更する。

(もっと読む)

201 - 210 / 8,021

[ Back to top ]