ルネサスエレクトロニクス株式会社により出願された特許

161 - 170 / 8,021

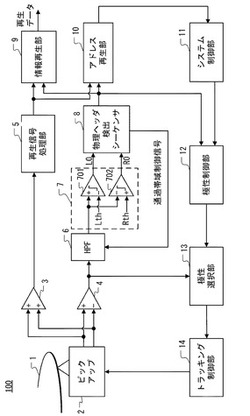

ヘッダ領域判定回路、光ディスク装置、及びヘッダ領域判定方法

【課題】光ディスクの物理ヘッダの領域を判定する処理の誤りを抑制するヘッダ領域判定回路を提供する。

【解決手段】ヘッダ領域判定回路は、光ディスク1から受光した受光量の差に比例する差信号を検出する差信号検出部4、通過帯域制御信号に応じて複数の遮断周波数を切り替え、差信号から低周波数成分を除去した差信号HPF出力を生成する高域通過フィルタ6、差信号HPF出力をパルス化した整形信号を生成する波形整形部7、及び、整形信号が示すパルスの持続時間を計測して、物理ヘッダ領域を検出し、物理ヘッダ領域の検出結果に基づいて、物理ヘッダ領域が溝部と溝間部とのいずれかであるかを判定したグルーブ検出信号と、物理ヘッダ領域の少なくとも一部分に対応する差信号に対して、高域通過フィルタ6の遮断周波数を引き下げるように制御する通過帯域制御信号とを生成する物理ヘッダ検出シーケンサ8を備える。

(もっと読む)

無線通信システム、無線通信方法、および無線機器

【課題】無線ネットワーク環境にRFID技術を利用したシステムを導入する際のコストを低減することが可能な無線通信システムを提供することである。

【解決手段】本発明にかかる無線通信システムは、データAを互いに送受信可能な第1の無線機器10および第2の無線機器20と、第1の無線機器10から出力された第2のデータBを受信可能な第3の無線機器30と、を備える。第1の無線機器10は、データAに応じて所定の変調方式で変調された第1の電波42、43を用いてデータAを第2の無線機器20に送信すると共に、データBに応じて第1の電波42、43を強度変調することでデータBを第3の無線機器30に送信する。

(もっと読む)

半導体記憶装置

【課題】読出速度が速い半導体記憶装置を提供する。

【解決手段】フラッシュメモリ3は、選択ビット線BLをプリチャージするプリチャージ回路45と、定電流源50と、電流検知型のセンスアンプ23と、選択ビット線BLがメモリアレイMA2に属する場合は、選択ビット線BLおよび定電流源50をそれぞれセンスアンプ23の入力ノードLBT,LBBに接続し、選択ビット線BLがメモリアレイMA3に属する場合は、選択ビット線BLおよび定電流源50を入力ノードLBB,LBTに接続する切換回路SWT2,SWB2,SWとを含む。したがって、ビット線BLのプリチャージとデータ読出を並列に実行できる。

(もっと読む)

リドライバIC、半導体装置、及びその製造方法

【課題】低損失で差動信号を伝送することができるリドライバIC、半導体装置、及びその製造方法を提供する。

【解決手段】本実施の形態に係る半導体装置は、差動信号が伝送される差動配線が形成された配線基板10と、配線基板10に搭載され、外部機器に対して差動信号を送受信するコネクタ11と、配線基板10に搭載され、コネクタ11から受信した差動信号を中継する受信系のリドライバIC21と、受信系のリドライバIC21と離間した位置において配線基板10に搭載され、コネクタ11に送信する差動信号を中継する送信系のリドライバIC20と、を備えるものである。

(もっと読む)

半導体装置および半導体装置の制御方法並びに半導体装置の設計支援方法

【課題】本発明の課題は、組み込みシステムのアーキテクチャに左右されることなく、DVFSの実行に必要なサイクル数を容易に取得することである。

【解決手段】ファームウェア(21)は、サイクル数概算ルーチン(213)と、動作電圧・周波数算出ルーチン(213)とを有する。サイクル数概算ルーチンは、サイクル数概算関数を備える。サイクル数概算関数は、ユーザ回路(6)の処理内容を決定づける属性パラメータの入力でタスクのサイクル数を概算する。動作電圧・周波数算出ルーチンは、サイクル数概算ルーチンの実行によって得られたサイクル数に基づいて、ユーザ回路(6)の目標動作電圧・周波数を算出する。

(もっと読む)

基準電圧変換回路及び半導体装置

【課題】回路規模を削減することが可能な基準電圧変換回路を提供する。

【解決手段】基準電圧変換回路100は、VDDとGNDとの間に接続され、伝送路を介して入力される差動入力信号RXP/RXNの基準電圧を変換した差動出力信号OUTP/OUTNを出力する変換部101と、VDDまたはGNDと変換部101との間に接続され、差動入力信号RXP/RXNの伝送路により減衰した周波数成分を補正するイコライザ部102と、を備えるものである。

(もっと読む)

ウィンドウ制御プログラム

【課題】マウスの傾斜に基づいてウィンドウを制御することが可能なウィンドウ制御プログラムを提供する。

【解決手段】本発明の一形態に係るウィンドウ制御プログラムは、コンピュータに、マウス21に設けられた傾斜検出部21aの出力に基づいて、マウス21の傾斜角度を算出する処理と、マウス21に設けられた傾斜検出部21aの出力に基づいて、マウス21が傾斜している時間を算出する処理と、マウス21の傾斜角度及びマウス21が傾斜している時間に基づいて、画面に表示するウィンドウを制御する処理と、を実行させる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子上の配線層の設計自由度に優れた半導体装置を提供する。

【解決手段】半導体装置は、基板、層間絶縁層、第1トランジスタ、多層配線層、容量素子、金属配線、及び第1コンタクトを備える。基板1上には、層間絶縁層4、5が設けられている。第1トランジスタ3aは、半導体基板1に設けられており、層間絶縁層内に埋め込されている。第1トランジスタは、少なくともゲート電極32及び拡散層を有する。層間絶縁層上には、多層配線層が設けられている。容量素子19は、多層配線層内に設けられている。金属配線(ゲート裏打ち配線)30は、ゲート電極32の上面と接しており、層間絶縁層4内に埋設されている。第1コンタクト10aは、第1トランジスタ3aの拡散層に接続しており、層間絶縁層4内に埋設される。金属配線(ゲート裏打ち配線)30は、第1コンタクト10aと同じ材料で構成されている。

(もっと読む)

DCDCコンバータ及びその制御方法

【課題】入力電圧を昇圧した出力電圧を精度良く生成することが可能なDCDCコンバータを提供すること。

【解決手段】本発明にかかるDCDCコンバータ100は、入力電圧Vinを昇圧した出力電圧Voutを生成するDCDCコンバータであって、発振信号Vosc1を出力する発振回路1と、発振信号Vosc1よりも高い発振周波数の発振信号Vosc2を出力する発振回路2と、出力電圧Voutの電圧レベルに基づいて、発振信号Vosc1,Vosc2のうち何れかを選択し出力する選択回路3と、選択回路3によって選択された発振信号のデューティ比に応じた電圧レベルまで入力電圧Vinを昇圧し、出力電圧Voutとして生成する電圧変換部と、を備える。

(もっと読む)

遅延ライブラリの生成方法及び遅延ライブラリ生成装置

【課題】静的タイミング解析ツールの処理結果に対する後処理時間を短くすること。

【解決手段】本発明にかかる遅延ライブラリの生成方法は、入力クロック信号を内部で分周するマクロの遅延ライブラリの生成方法であって、マクロの設計情報に基づいて、入力クロック信号を内部で分周する分周回路を抽出するステップと、抽出された分周回路が静的タイミング解析においてクロックラインの一部とみなされるように設計情報を修正する修正ステップと、修正された設計情報を用いて遅延ライブラリを生成する生成ステップと、を有する。

(もっと読む)

161 - 170 / 8,021

[ Back to top ]