ルネサスエレクトロニクス株式会社により出願された特許

151 - 160 / 8,021

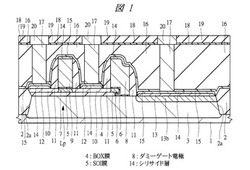

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

電源用半導体装置

【課題】低コストでマルチフェーズ電源を実現可能な電源装置を提供する。

【解決手段】例えば、複数の半導体デバイスDEV[1]〜DEV[n]のそれぞれが、トリガ入力端子TRG_IN、トリガ出力端子TRG_OUT、およびTRG_INから入力されたパルス信号を遅延させてTRG_OUTに出力するタイマ回路TMを備える。DEV[1]〜DEV[n]は、自身のTRG_INが自身以外の1個の半導体デバイスのTRG_OUTに接続されることで、互いにリング状に接続される。DEV[1]〜DEV[n]のそれぞれは、TRG_INからのパルス信号を起点としてスイッチング動作を行い、自身に対応するインダクタLに電流を流す。また、DEV[1]は、スタートトリガ端子STが例えば接地電圧GNDに設定されることで、起動時に一度だけ前述したパルス信号の生成を行う。

(もっと読む)

バス接続回路、半導体装置及びバス接続回路の動作方法

【課題】直接転送をする場合と直接転送をしない場合とが混在しても、MEMC設定等の追加の動作を行うことなく、1サイクル転送することを可能とする。

【解決手段】バス接続回路は、バスマスタ10と複数のバススレーブ12、15とを接続する。バス接続回路は、ミラー領域アクセス検出回路13と、処理回路21、22、14とを具備する。ミラー領域アクセス検出回路13は、バスマスタ10が複数のバススレーブ12、15のうちの第1バススレーブ12のミラー領域へアクセスすることを検出して、検出信号35を出力する。処理回路21、22、14は、検出結果35に基づいて、当該検出結果35に対応して予め設定されている処理を、アクセスの対象としての領域又はデータに対して実行する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】第1導電型の第1ドリフト領域140は、平面視でソース領域110から離間して設けられている。第1導電型の第2ドリフト領域150は、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。チャネル領域130上には、ゲート絶縁層200およびゲート電極400が設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接している。

(もっと読む)

入力回路

【課題】高電位信号を低電位信号に変換する入力回路であって、適切なターゲット反転電位で動作可能な入力回路を提供する。

【解決手段】入力回路は、高電源電位が入力される入力端子とグランド端子との間に接続された抵抗と、抵抗中の第1ノードに接続された第2ノードと、第2ノードと第3ノードとの間に接続されたインバータと、抵抗を通した入力端子とグランド端子との間の電気的接続をON/OFF制御するスイッチと、を備える。ターゲット反転電位は、インバータの反転電位よりも高い。入力端子の電位がターゲット反転電位の場合、第2ノードの電位がその反転電位となる。第2ノードの電位が反転電位より低い場合、インバータは低電源電位を第3ノードに出力し、且つ、スイッチは上記の電気的接続をONする。一方、第2ノードの電位が反転電位より高い場合、インバータはグランド電位を第3ノードに出力し、且つ、スイッチは上記の電気的接続をOFFする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

半導体装置

【課題】配線基板上にメモリチップとコントローラチップとを積層したパッケージ構造を備えた半導体装置において、メモリチップとコントローラチップを接続する配線の自由度を向上させる。

【解決手段】メモリカード1Aは、配線基板2とその主面上に積層された4枚のメモリチップM1〜M4と最上層のメモリチップM4の表面上に実装されたコントローラチップ3およびインターポーザ4とを備えている。メモリチップM1〜M4のそれぞれは、その長辺を配線基板2の長辺と同じ方向に向けた状態で配線基板2の表面上に積層されている。最下層のメモリチップM1は、配線基板2のパッド9と重ならないよう、メモリカード1Aの先端部方向に所定距離ずらした状態で配線基板2上に実装されている。メモリチップM1上に積層された3枚のメモリチップM2〜M4は、パッド6が形成されている側の短辺がメモリカード1Aの先端部に位置するように配置されている。

(もっと読む)

ヘッダ領域判定回路、光ディスク装置、及びヘッダ領域判定方法

【課題】光ディスクの物理ヘッダの領域を判定する処理の誤りを抑制するヘッダ領域判定回路を提供する。

【解決手段】ヘッダ領域判定回路は、光ディスク1から受光した受光量の差に比例する差信号を検出する差信号検出部4、通過帯域制御信号に応じて複数の遮断周波数を切り替え、差信号から低周波数成分を除去した差信号HPF出力を生成する高域通過フィルタ6、差信号HPF出力をパルス化した整形信号を生成する波形整形部7、及び、整形信号が示すパルスの持続時間を計測して、物理ヘッダ領域を検出し、物理ヘッダ領域の検出結果に基づいて、物理ヘッダ領域が溝部と溝間部とのいずれかであるかを判定したグルーブ検出信号と、物理ヘッダ領域の少なくとも一部分に対応する差信号に対して、高域通過フィルタ6の遮断周波数を引き下げるように制御する通過帯域制御信号とを生成する物理ヘッダ検出シーケンサ8を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置(不揮発性メモリを有する半導体装置)の特性を向上させる。

【解決手段】本発明の半導体装置は、制御ゲート電極CGと半導体基板との間に形成された絶縁膜3と、メモリゲート電極MGと半導体基板との間および制御ゲート電極CGとメモリゲート電極MGとの間に形成された絶縁膜5であって、その内部に電荷蓄積部を有する絶縁膜5と、を有する。この絶縁膜5は、第1膜5Aと、第1膜5A上に配置された電荷蓄積部となる第2膜5Nと、第2膜5N上に配置された第3膜5Bと、を有し、第3膜5Bは、制御ゲート電極CGとメモリゲート電極MGとの間に位置するサイドウォール膜5sと、メモリゲート電極MGと半導体基板との間に位置するデポ膜5dとを有する。かかる構成によれば、絶縁膜5の角部における距離D1を大きくすることができ、電界集中を緩和できる。

(もっと読む)

データ処理装置、そのデータ処理装置を備えた外部記憶装置及びデータ消去方法

【課題】外部記憶装置のデータ消去時間を短縮することができるデータ処理装置、そのデータ処理装置を備えた外部記憶装置及びデータ消去方法を提供すること

【解決手段】本発明にかかるUSB−SATAブリッジコントローラ10は、パソコン16からのデータをハードディスク17に書き込むデータ処理装置である。USB−SATAブリッジコントローラ10は、CPU12と、パソコン16とハードディスク17との間で伝送されるデータを一時保管するメモリ13と、CPU12の制御に基づいてハードディスク17のデータ消去用のデータを生成する擬似乱数生成器18と、前記データ消去用のデータをバッファし、メモリ13よりも小さな記憶容量を有するディスク消去用データ記憶部19と、ハードディスク17に、バッファされた前記データ消去用のデータをハードディスク17のデータ消去完了まで順次書き込むSATAホストコントローラ15を備える。

(もっと読む)

151 - 160 / 8,021

[ Back to top ]