株式会社ルネサステクノロジにより出願された特許

4,771 - 4,780 / 4,790

半導体集積回路装置の製造方法

規格外れの不良ウェハをリアルタイムに検出することができる半導体集積回路装置の製造方法を提供することにある。

異常検知サーバ5は半導体ウェハを処理する半導体製造装置から出力された装置ログデータを装置ログデータ記憶部10に記憶する。その後、ロットエンド信号受信部12において、半導体製造装置から出力されるロットエンド信号を受信すると、異常データ検知部15は、第1検知条件記憶部13に記憶されている異常検知条件設定ファイル13aを参照した後、参照した内容に基づいて装置ログデータ記憶部10に記憶されている装置ログデータの中に異常データがあるか否かを判定する。そして、異常を検知するとエンジニアPCや作業者端末装置に検知結果を出力する。

(もっと読む)

半導体集積回路装置

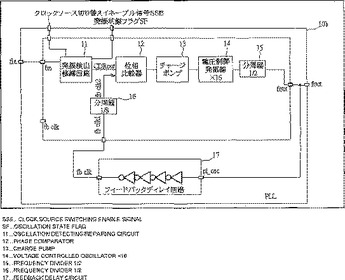

半導体集積回路装置におけるクロック発生器には、発振検出修繕回路11が設けられている。この発振検出修繕回路11は、外部接続されたクロック発振器が生成したクロック信号finの正常/異常を検出する。クロック信号finが正常の際には、該クロック信号finを選択して出力する。また、クロック信号finが異常の場合には、発振検出修繕回路11が生成したクロック信号を選択して出力する。クロック発生器は、発振検出修繕回路11が選択して出力するクロック信号に基づいてシステムクロックを生成する。また、クロック信号finが異常の場合、CPUは、各モジュールを停止させた後、該CPUを停止させる異常終了処理を実行する。  (もっと読む)

(もっと読む)

信号伝送システム及び信号伝送線路

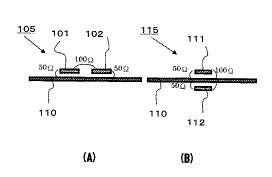

【課題】 グランドを参照する差動線路とグランドを参照しない差動線路を接続して、数十GHz帯のデジタル高速信号を差動線路を介して伝送する。

【解決手段】信号伝送線路を介して回路ブロック間でデジタル信号の伝送を行う信号伝送システムにおいて、各回路ブロックはそれぞれ機能回路と分離された構成の受送信回路を備え、受信端と送信端の間がインピーダンス整合した伝送線路115であることを基本構成とし、差動出力ドライバから導出されたグランド参照差動線路105を上記回路ブロック内でグランド110を中心にして差動信号の線路を対称に配置した構成とし、上記信号伝送線路115内ではグランド110を参照しない差動ペア線路111,112のみが前記グランド110を中心とする対称構造の線路から直接延長された構造とする。

(もっと読む)

半導体装置

【課題】半導体装置の全体的な放熱性を向上させる。

【解決手段】増幅用のnチャネルLDMOSが形成された半導体チップ11a,11c,11bの裏面のソース電極を配線基板10の主面の配線パターン10bに接合し、これを配線基板10の主面から裏面に延びるビアホール10c2を通じて配線基板10の裏面の基準電位供給用の配線パターン10bに電気的および熱的に接続する。一方、上記nチャネルLDMOSに電源電圧を供給するトレンチゲート構造のpMOSが形成された半導体チップ11bの裏面のドレイン電極を配線基板10の主面の配線パターン10bに接合し、これを配線基板10の主面から配線基板10の厚さ途中の位置まで延びるビアホール10c3と電気的および熱的に接続する。さらにそのビアホール10c3の下方に絶縁体板10a1を挟んでビアホール10c4を設ける。

(もっと読む)

マイクロプロセッサ及び携帯通信端末

【課題】動画処理と音声処理とが互いに異なるプロセッサで行われる場合の動画と音声の同期をとる。

【解決手段】ベースバンド処理を行うベースバンドプロセッサ(14)と対で使用されるマイクロプロセッサ(18)において、演算処理のための中央処理装置(183)と、上記中央処理装置での演算処理における時間計測を可能とするカウンタ(184)と、上記ベースバンドプロセッサから上記カウンタのリードを可能とするためのインタフェース回路(187)とを設け、上記ベースバンドプロセッサは上記カウンタをリードすることにより、上記ベースバンドプロセッサでの処理を上記マイクロプロセッサにおける中央処理装置での処理に同期させる。

(もっと読む)

マイクロコントローラ、マイクロプロセッサおよび不揮発性半導体メモリ装置

【課題】AND/NAND型フラッシュメモリにおけるデータのランダムアクセスを可能とし、データの転送効率を大幅に向上する。

【解決手段】フラッシュメモリ10へデータを書き込む際、フラッシュメモリコントローラ1は、メインバス側からのデータの読み出し要求の際、その読み出し要求にかかるデータが第1バッファ7に格納されているか否かに応じて、第1バッファ7にデータが格納されている場合は、その格納されているデータをメインバス側に出力し、該第1バッファ7にデータが格納されていない場合は、フラッシュメモリ10に対してデータ読み出しを行い、メインバス側に出力する。

(もっと読む)

カメラモジュール

【課題】レンズ一体型のカメラモジュールにおいても、シェーディング補正の技術を積極的に採用して、電子回路による演算処理で周辺減光を補正することができるカメラモジュールを提供する。

【解決手段】レンズ、画像センサ、画像処理回路を内蔵したレンズ一体型のカメラモジュールであって、画像処理回路は、レンズを含む光学系の中心軸からの距離を2乗した値を補正値に用いて、画像センサの画素位置に対応した光強度の補正を行う補正手段を有し、この補正手段を構成する乗算器9は水平中心からの距離Xを入力としてX2を計算し、乗算器10は垂直中心からの距離Yを入力としてY2を計算し、この計算されたX2とY2を加算器11に入力して光軸からの距離の2乗値R2を計算し、そして乗算器12にてR2に対して係数A1を乗じて補正係数B1を得て、この補正係数B1によって周辺減光を補正する。

(もっと読む)

半導体素子

【課題】縦型パワーMOSFETのオン抵抗及び漏れ電流の低減

【解決手段】単位MOSFET(セル)を縦横に半導体基板主面に配置した縦型高耐圧MOSFETにおいて、セル形状を四角形とし、各セルにおいては、四角形のソースコンタクト孔内に内端部分が露出するソース領域を、前記四角形の各辺ごとに分離して配置する。各ソース領域は台形となり、台形の下辺はゲート電極(ゲート絶縁膜)の下に位置し、台形の上辺部分はソースコンタクト孔内に露出する。4個のソース領域は四角形の対角線に沿う領域で相互に分離されている。

(もっと読む)

半導体集積回路装置、無線LANシステム、および自動ゲイン制御システム

【課題】ベースバンド処理部に負担をかけることなく、オートゲインコントロール処理を短時間で、かつ高精度に行う。

【解決手段】無線LANシステム1が受信状態になると、ゲイン制御回路19は受信アンテナ2,3を交互に切り換える。ある受信感度を超える信号を受信すると、ゲイン制御回路19は、第1測定回路18が測定した受信レベルに応じてゲイン設定値時分割データTDを設定し、LNA9のゲイン設定値、およびLPF/PGA16,17の前段に設けられた2つのプログラマブルゲインアンプのゲイン粗制御を行う。そして、DCオフセットをキャンセルし、第2測定回路26が信号レベルを測定し、その信号レベルに応じてゲイン設定値時分割データTDを設定してLPF/PGA16,17の後段に設けられたプログラマブルゲインアンプのゲインを高精度に設定し、オートゲインコントロール処理を終了する。

(もっと読む)

パケット通信装置

【課題】パケットの転送又は送受信に伴うパケット変換を高速に行うパケット通信装置を提供することにある。

【解決手段】複数の通信手段の受信による受信パケットまたは複数の通信手段が送信する送信パケットに対してパケット変換を行うパケット変換手段と、通信手段の受信による受信パケットが転送用パケットであると判定した時には受信パケットを転送用バッファ手段に出力するとともに、パケット生成処理手段が生成した送信パケットの宛先の通信対象に対応した通信手段および転送用バッファ手段に保持された転送用パケットの宛先の通信対象に対応した通信手段に出力する転送制御手段とを備える。

(もっと読む)

4,771 - 4,780 / 4,790

[ Back to top ]