サンディスク スリーディー,エルエルシーにより出願された特許

21 - 30 / 86

ダミー抵抗、抵抗スイッチング素子及びダイオードを有するマルチビット抵抗スイッチング・メモリセルへの書き込み

不揮発性記憶装置は、Y線の組と、X線の組と、X線の組及びY線の組と通信する複数のメモリセルを有している。複数のメモリセルのうちの各メモリセルは、固定抵抗状態にある抵抗素子と、2個以上の可逆抵抗スイッチング素子と、複数のダイオードを有している。固定抵抗状態にある抵抗素子と2個以上の可逆抵抗スイッチング素子は、Y線の組のうちの対応するY線及び対応するダイオードに接続されており、ダイオードは、X線の組のうちの共通X線に接続されている。1ビット又は複数ビットのデータは、複数のメモリセルのうちの特定のメモリセルに接続されているY線の間に電流を流すことによってこの特定のメモリセルにプログラミングされる。  (もっと読む)

(もっと読む)

柱状構造のためのレジストフィーチャおよび除去可能スペーサピッチを倍増するパターニング法

半導体装置を製作する方法が、基板上に少なくとも1つの層を形成することと、少なくとも1つの層の上に画像形成性材料よりなる少なくとも2つの離間されたフィーチャを形成することと、少なくとも2つのフィーチャ上に側壁スペーサを形成することと、第1のフィーチャ上の第1の側壁スペーサと第2のフィーチャ上の第2の側壁スペーサとの間の空間をフィラーフィーチャで充填することと、を含む。この方法はまた、第1のフィーチャ、フィラーフィーチャおよび第2のフィーチャを互いに離間した状態で残すように、側壁スペーサを選択的に除去することと、第1のフィーチャ、フィラーフィーチャおよび第2のフィーチャをマスクとして使用して少なくとも1つの層をエッチングすることと、を含む。  (もっと読む)

(もっと読む)

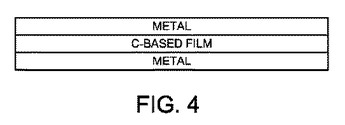

低減された層間剥離特性を示す炭素系メモリ素子およびその形成方法

可逆的に抵抗を切り換える金属−絶縁物−金属(MIM)スタックを形成する方法が提供される。この方法は、縮退ドープされた半導体材料を含む第1の導電層を形成することと、第1の導電層上に炭素系可逆抵抗スイッチング材料を形成することと、を含む。また、他の態様も提供される。  (もっと読む)

(もっと読む)

データをメモリ装置に再入力することなくページをプログラムするためのページバッファプログラムコマンド及び方法

外部ホスト装置と通信するメモリ装置における書き込み動作失敗を効率的に取り扱う技術は、データのページがメモリバッファからメモリアレイに再書き込みされることを可能にする。ホストは、ユーザデータ、第1の書き込みアドレス、及び、書き込みコマンドをメモリ装置に供給する。書き込み試行が失敗である場合、ホストは、ユーザデータをメモリ装置に再送信することなく、新アドレスと共に再書き込みコマンドを供給する。ページバッファからの再書き込みの進行中に、付加データがメモリ装置のデータキャッシュで受信される。再書き込みデータは、データがホストへ読み出され、変更され、メモリ装置にライトバックされるコピー動作の中で取得されることがある。付加データは、コピー動作の中でメモリ装置に入力できる。ページバッファ・データは所定の位置でさらに変更できる。  (もっと読む)

(もっと読む)

可逆的抵抗スイッチングメモリ材料用のセット及びリセット検出回路

メモリデバイスの可逆的抵抗スイッチングメモリ素子のセットまたはリセットプロセスを実行する回路。ランプ電圧がメモリセルに印加され、その状態が常に監視されることで、セットまたはリセットプロセスが完了すると直ちに電圧が放電されてメモリセルへの撹乱の可能性が回避される。あるセット回路は、オペアンプループを用いてピーク電流を検出しながら、電流源を用いて電圧をランプする。あるリセット回路は、出力信号を安定に保つためにピーク電流の電流を取り込み続けることによってピーク電流を検出しながら、オペアンプループを用いて電圧をランプする。別のセット回路は、オペアンプループ及びソースフォロア構成を用いて電圧をランプする。別のリセット回路は、オペアンプループと、消費電力を抑制するためのレベルシフトを有するソースフォロア構成とを用いて電圧をランプする。より高速な検出及び遮断と安定な動作とが実現される。  (もっと読む)

(もっと読む)

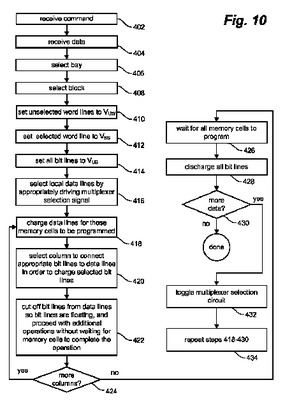

不揮発性メモリの連続的なプログラミング

不揮発性記憶素子は、信号ドライバを第1の不揮発性記憶素子に接続された第1の制御線に接続し、信号ドライバが第1の制御線に接続されている間に信号ドライバを用いて第1の制御線を充電し、第1の制御線が信号ドライバから充電された状態を維持している間に信号ドライバを第1の制御線から切断し、信号ドライバを第2の不揮発性記憶素子に接続された第2の制御線に接続し、信号ドライバが第2の制御線に接続されている間に信号ドライバを用いて第2の制御線を充電し、信号ドライバを第2の制御線から切断する。制御線を充電するステップは、不揮発性記憶素子の各々に、プログラム処理を起こさせる。信号ドライバを第1の制御線から切断するステップ、信号ドライバを第1の制御線に接続するステップ、および第2の制御線を充電するステップは、第1の不揮発性記憶素子のプログラム処理の完了を待たずに行われる。  (もっと読む)

(もっと読む)

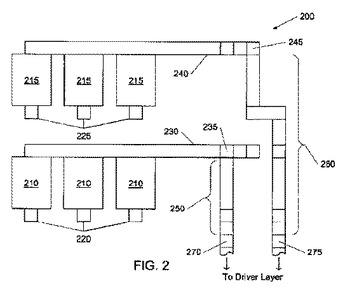

3Dメモリアレイの製造のためのX線用の共用マスクとY線用の共用マスク

デバイス層の数より少ない数のビット線マスクを用いて3次元メモリを製造する構造および方法を開示する。第1のビット線層を第1のデバイスレベルに形成するために第1のビット線マスクが使用される。第1のビット線層は複数の第1のビット線を含む。第1のビット線マスクは、第2のビット線層を第2のデバイスレベルに形成するためにも使用される。第2のビット線層は複数の第2のビット線を含む。第1のビット線および第2のビット線は、同じマスクパターンを使用するにもかかわらず、ビット線接続レベルへの異なる電気的接続を有する。  (もっと読む)

(もっと読む)

区分データ線を有するメモリシステム

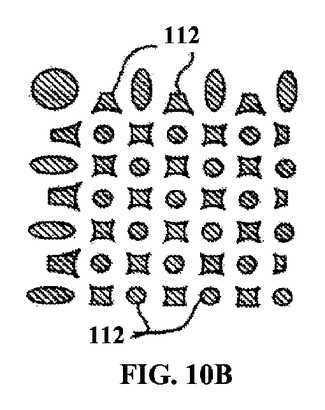

記憶システムは、複数のブロックにグループ分けされた複数層の不揮発性記憶素子群を有する3次元メモリアレイを備える。ブロックは複数のベイにグループ分けされている。

記憶システムは、記憶素子と通信する第1タイプのアレイ線と、記憶素子と通信する第2タイプのアレイ線と、センスアンプを含む。各ブロックは、2個のセンスアンプと地理的に関連付けられており、特定ベイの全ブロックは、その特定ベイのブロックに関連付けられたセンスアンプのグループを共有する。システムは、3次元メモリアレイの下方に位置する1以上のルーティング金属層内のローカルデータ線の複数セットと、3次元メモリアレイの上方に位置する1以上の最上位金属層内のグローバルデータ線の複数セットを含む。1以上のブロックの各セットは、ローカルデータ線の一セットを含む。各ベイは、夫々のベイのブロックに関連付けられたセンスアンプのグループに接続するグローバルデータ線の一セットを含む。各ブロックは、第1タイプのアレイ線のサブセットを夫々のローカルデータ線と選択的にカップリングするための第1選択回路のサブセットを含む。各ブロックは、夫々のローカルデータ線のサブセットを夫々のベイに関連付けられたグローバルデータ線と選択的にカップリングするための第2選択回路のサブセットを含む。  (もっと読む)

(もっと読む)

不揮発性メモリデバイスを製作する方法

半導体デバイスを製作する方法は、絶縁層(108)に取り囲まれた柱形半導体デバイスを形成するステップであって、絶縁層内のコンタクトホール(111)が半導体デバイスの上面を露出させるステップを含む。この方法はまた、絶縁層(108)上にシャドウマスク層(302)を形成するステップであって、シャドウマスク層(302)の一部分がコンタクトホール(111)の一部分に突出するステップと、導電層を形成するステップであって、導電層の第1の部分(304)がコンタクトホール内に露出する半導体デバイスの上面に位置し、導電層の第2の部分(306)がシャドウマスク層(302)上に位置するステップと、シャドウマスク層(302)と導電層の第2の部分(306)とを除去するステップと、を含む。  (もっと読む)

(もっと読む)

炭素系抵抗率スイッチング材料およびその形成方法

炭素系抵抗率スイッチング可能な材料を含むメモリデバイス、およびこのようなメモリデバイスを形成する方法が提供される。この方法は、炭化水素化合物およびキャリアガスを含むプロセスガスをプロセスチャンバに導入するステップと、プロセスチャンバ内でプロセスガスのプラズマを発生させて基板の上に炭素系抵抗率スイッチング可能な材料の層を堆積させるステップと、を含む。多くのさらなる態様が提供される。  (もっと読む)

(もっと読む)

21 - 30 / 86

[ Back to top ]