モサイド・テクノロジーズ・インコーポレーテッドにより出願された特許

61 - 70 / 106

複数セル基板を有するNANDフラッシュメモリ

NANDフラッシュメモリバンクは、ページバッファに接続されたメモリアレイの複数のビット線を有し、同じビット線に接続されたNANDセルストリングは、少なくとも2つのウェルセクタ中に形成される。非選択ウェルセクタへの消去電圧の印加を禁止するように、ウェルセクタは消去動作中に消去電圧に選択的に結合される。ウェルセクタの面積が減少するとき、各ウェルセクタの容量に対応した減少がもたらされる。したがって、チャージポンプ回路の駆動能力が変化しないとき、単一ウェルメモリバンクと比較してNANDフラッシュメモリセルの高速消去が達成される。あるいは単一ウェルメモリバンクに対応する一定の消去速度は、減少させた駆動能力のチャージポンプと特定の面積を有するウェルセグメントとをマッチングさせて得られる。減少させた駆動能力のチャージポンプはより小さな半導体チップ面積を占有し、コストを削減する。  (もっと読む)

(もっと読む)

直列接続された集積回路を積層する方法およびその方法で作られたマルチチップデバイス

デバイスを製作するために複数の実質的に同一のチップを積層する、マルチチップデバイスおよび方法が、提供される。マルチチップデバイス、または回路は、少なくとも2つのチップからの信号パッド間に並列接続をもたらす、少なくとも1つのスルーチップバイアと、少なくとも2つのチップからの信号パッド間に直列接続またはデイジーチェーン接続をもたらす、少なくとも1つのスルーチップバイアとを含む。コモン接続信号パッドは、複製コモン信号パッドに対してチップの中心線周りに対称に配列される。入力信号パッドは、対応する出力信号パッドに対して、チップの中心線周りに対称に配置される。積層体の中のチップは、この配列をもたらすために、実質的に同一のチップが交互に裏返されたバージョンである。2個以上のチップが積層されるとき、少なくとも1つの直列接続が積層され裏返されたチップの信号パッド間にもたらされる。  (もっと読む)

(もっと読む)

二重機能対応の不揮発性メモリ素子

非同期動作と同期直列動作とを両立できる二重機能メモリ素子アーキテクチャ。この二重機能メモリ素子アーキテクチャは、2つの異なる機能割当を有する1組の物理ポートを含む。このメモリ素子の物理ポートとコア回路との間に結合されるのが、非同期および同期入出力信号経路または回路である。この信号経路は、ポートに結合される共用バッファまたは専用バッファ、非同期コマンドデコーダおよび同期コマンドデコーダ、スイッチ回路網、ならびにモード検出器を含む。モード検出器は、ポートからこの二重機能メモリ素子の動作モードを判定し、適切なスイッチ選択信号を提供する。スイッチ回路網は、そのスイッチ選択信号に応じて、入力信号または出力信号を非同期回路もしくは同期回路を介して送る。適切なコマンドデコーダは、入力信号を解釈し、対応する動作を開始するための所要の信号を共用制御ロジックに提供する。  (もっと読む)

(もっと読む)

NANDフラッシュメモリにおける階層的な共通ソース線構造

一般的NANDフラッシュセルブロックにおける各メモリセルストリングは、共通ソース線(CLS)に接続されている。CSLに印加する値は、集中的に生成されるとともに、各NANDフラッシュセルブロックに対応するローカルスイッチ論理ユニットに分散される。ソース線ページプログラムにおいて、分散線をグローバル共通ソース線(GCSL)と呼ぶことができる。NANDフラッシュセルブロックのアレイにおいて、一つのNANDフラッシュセルブロックのみがプログラムにおける一時に選択される。消費電力を抑えるために、選択されたNANDフラッシュセルブロックのみが、GCSL上の値を示すCSL上の値を受信する。さらに、非選択NANDフラッシュセルブロックのCSLは、グランドへのアクティブ接続を介してデセイブルされる。  (もっと読む)

(もっと読む)

複数のデバイスおよび柔軟なデータ整列を用いるメモリコントローラを有するシステムにおけるクロック再生およびタイミング方法

システムは、メモリコントローラおよび直列接続されている複数の半導体デバイスを備える。各デバイスはデータを格納する。コントローラは、デバイスの動作を同期させるクロックを供給する。各デバイスは、イネーブル信号によって選択的にイネーブルまたはディセーブルされるPLLを備える。選択デバイスのPLLはイネーブル信号によってイネーブルされ、他のデバイスはディセーブルされる。イネーブルされたPLLは、90°の倍数の位相シフトで複数の再生クロックを供給する。データ転送は、再生クロックのうちの1つのクロックと同期する。ディセーブルされたPLLのデバイス内で、データ転送は入力クロックと同期する。イネーブルおよびディセーブルされたPLLにより、各デバイスはソース同期クロッキングおよび共通同期クロッキングを行う。最後のデバイスのデバイス識別子の最下位ビットがクロック整列を決定する。  (もっと読む)

(もっと読む)

読取列選択信号と読取データバス事前充電制御信号のインタロック

DRAMメモリ用の列選択およびデータバス事前充電信号インタロック方式を提供する。信号インタロックシステムは、データを共通読取データバスに結合するための列選択信号と、読取データバス事前充電デバイスを使用不能にするための読取データバス事前充電ディセーブル信号とを生成するための、DRAMメモリの各バンクに関連する列読取イネーブル回路を含む。各列読取イネーブル回路は、読取り動作中に少なくとも1つの列選択信号パルスと読取データバス事前充電ディセーブルパルスとを生成するための、調整可能コンポーネントを有するパルス生成器回路を含む。パルス生成器回路は、列選択パルスが読取データバス事前充電ディセーブルパルスに対して常にネストされることを保証する。したがって、アクティブな列選択デバイスとアクティブな読取データバス事前充電デバイスの間にオーバラップは存在しない。  (もっと読む)

(もっと読む)

複数のチャージポンプ回路を用いて昇圧された電圧を生成する装置および方法

本発明は、複数のチャージポンプ回路、チャージポンプ制御信号、およびアクティブなチャージポンプのアクティブな容量性エレメントを用いて、昇圧された電圧を生成するための装置および方法に関するものである。さらに、本発明は、活性化されたチャージポンプの容量性エレメントが、チャージポンプへの入力電圧およびチャージポンプ信号に応じて充電される、装置および方法、ならびにダイナミックランダムアクセスメモリを提供するものである。  (もっと読む)

(もっと読む)

デイジーチェーンメモリの構成および使用

デイジーチェーンメモリ構成および使用について開示する。メモリシステムは、デイジーチェーン方式で結合されたコントローラ、および多数の連続メモリデバイスからなる対応するストリングを含む。コントローラは、直列制御リンクを介してコマンドを伝達して、第1のメモリデバイスを、チェーン中の第2のメモリデバイスにデータブロックを書き込むように構成する。たとえば、コントローラは、デイジーチェーン制御リンクを介して通信して、多数のメモリデバイスのうち第1のメモリデバイスを、データを出力するソースとなるように構成し、デイジーチェーン制御リンクを介して通信して、第2のメモリデバイスを、データを受信する移動先となるように構成し、デイジーチェーン制御リンクを介して通信して、第1のメモリデバイスから第2のメモリデバイスへのデータの転送を開始することによって、データブロックのコピーを開始する。  (もっと読む)

(もっと読む)

デュアル機能を有するマルチレベルセルアクセスバッファ

2段階MLC(マルチレベルセル)オペレーションを使用する、フラッシュなどの不揮発性メモリに書き込むための、ページバッファなどのアクセスバッファが提供される。アクセスバッファは、書き込むべきデータを一時的に格納する第1ラッチを有する。2段階書込みオペレーションの一部としてメモリからデータを読み取るために第2ラッチが設けられる。第2ラッチは、メモリから読み取るときにラッチ機能に関与するインバータを有する。同じインバータが、第1ラッチに書き込まれている入力信号の補数を生成するのに使用され、その結果、第1ラッチに書き込むのに両端入力が使用される。  (もっと読む)

(もっと読む)

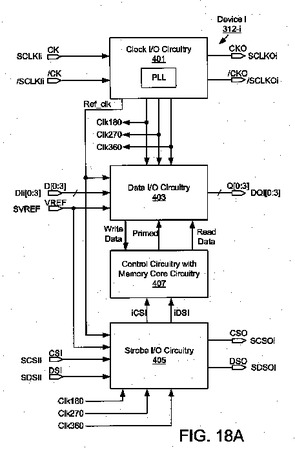

直列接続された半導体デバイスの構成内のクロック信号同期の方法および装置

システム制御装置と、直列接続された半導体デバイスを含む。前記デバイスは、前のデバイスから発信されたクロック信号を受信し、後続のデバイス宛の同期クロック信号を供給する。このデバイスは、受信したクロック信号及び同期クロック信号の以前のバージョンを処理して、同期クロック信号を生成するクロック同期装置をさらに含む。このデバイスは、同期クロック信号の以前のバージョンを処理する際にクロック同期装置に使用されるパラメータを調整するデバイス制御装置をさらに含む。システム制御装置は、第1デバイスへ第1クロック信号を供給する出力と、第2デバイスから第2クロック信号を受信する入力とを有する。第2クロック信号は、クロック同期装置による処理を受けたバージョンの第1クロック信号に一致する。システム制御装置は、第1および第2クロック信号間の位相差に基づいて、クロック同期装置に調整を指令する。  (もっと読む)

(もっと読む)

61 - 70 / 106

[ Back to top ]