モサイド・テクノロジーズ・インコーポレーテッドにより出願された特許

41 - 50 / 106

遅延ロックループのための初期化回路

【課題】遅延ロックループのための起動回路を提供する。

【解決手段】遅延ロックループにおける初期化回路は、電源投入または他のリセットの後、クロック端縁が適切な動作のために適切な順序で位相検出器によって受取られることを確実にし、遅延ロックループのリセット後、初期化回路は、遅延線における遅延を増加(または減少)させるように位相検出器をイネーブルするより先に基準クロックの少なくとも1つの端縁が受取られることを確実にし、フィードバッククロックの少なくとも1つの端縁が受取られた後、初期化回路は位相検出器をイネーブルして、遅延線における遅延を減少(または増加)させる。

(もっと読む)

マスタデバイスを含む積み重ね半導体デバイス

本発明は、スタックを備えるシステムを開示する。このスタックは、第1の不揮発性メモリチップと、少なくともいくつかの非コア回路が欠如している第2の不揮発性メモリチップと、第1の不揮発性メモリチップと第2の不揮発性メモリチップの間に延びる複数の電気経路とを含み、これらの電気経路により、第1の不揮発性メモリチップが第2の不揮発性メモリチップに、デバイス動作のために必要な信号および電圧を供給することが容易になる。  (もっと読む)

(もっと読む)

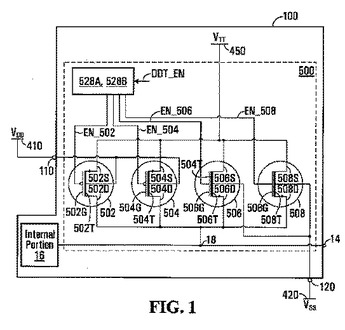

オンダイ終端のための終端回路

内部部分に接続されている端子を有する半導体デバイスにおいて、そのデバイスの端子用のオンダイ終端を提供するための終端回路。この終端回路は、端子と電源の間に接続された、少なくとも1つのNMOSトランジスタおよび少なくとも1つのPMOSトランジスタを含む複数のトランジスタと、NMOSトランジスタのそれぞれのゲートを対応するNMOSゲート電圧でドライブし、PMOSトランジスタのそれぞれのゲートを対応するPMOSゲート電圧でドライブするための制御回路であって、オンダイ終端が有効である場合にトランジスタを動作のオーム領域におくようにNMOSゲート電圧およびPMOSゲート電圧を制御するように構成されている、制御回路とを含む。電源は、上記NMOSゲート電圧のそれぞれより小さく、上記PMOSゲート電圧のそれぞれより大きい電圧を供給する。  (もっと読む)

(もっと読む)

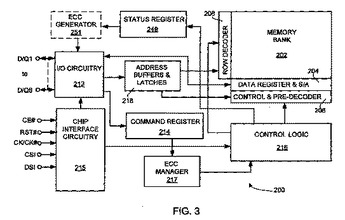

エラー検出方法および1つまたは複数のメモリデバイスを含むシステム

1つまたは複数のメモリデバイスを含むシステムと、エラーの検出および訂正の方法とが開示される。システムのメモリデバイスが、パケットを受信するための入力を含む。パケットの第1の部分は、少なくとも1つのコマンドバイトを含むことが可能であり、パケットの第2の部分は、コマンドエラー検出を容易にするパリティビットを含むことが可能である。メモリデバイスは、パリティビットに基づいて、エラーが少なくとも1つのコマンドバイト内に存在するかどうかを検出するように構成されているエラーマネージャと、パケットをエラーマネージャに供給するように構成されている回路とを含むことが可能である。  (もっと読む)

(もっと読む)

プリセットオペレーションを必要とするメインメモリユニットおよび補助メモリユニットを備える半導体デバイス

入力データを不揮発性記憶装置デバイスに転送する半導体デバイス。半導体デバイスは、複数のデータ要素を入れた仮想ページバッファと、対応する複数のデータ要素を入れたマスクバッファと、(i)トリガーを受け取った後、マスクバッファの各データ要素を第1の論理状態に設定し、(ii)選択された仮想ページバッファのデータ要素に入力データが書き込まれるようにし、(iii)選択された仮想ページバッファのデータ要素に対応するマスクバッファのデータ要素が、異なる論理状態に設定されるようにする制御論理回路と、仮想ページバッファの各データ要素について、そこから読み出されたデータを対応するマスクバッファのデータ要素の論理状態と組み合わせてまとめることによってマスクされた出力データを生成するマスク論理回路と、マスクされた出力データを不揮発性メモリデバイスに放出する出力インターフェイスとを備える。  (もっと読む)

(もっと読む)

封止された複数の半導体チップを備えたソリッドステートドライブまたは他の記憶装置

ソリッドステートドライブが開示される。ソリッドステートドライブは、互いの反対側にある第1の表面および第2の表面を有する回路基板を含む。ソリッドステートドライブの回路基板のうち第1の表面には複数の半導体チップが取り付けられており、ソリッドステートドライブの複数の半導体チップは、樹脂の中に少なくとも実質的に封止されている少なくとも1つのメモリチップを含む。また、インラインメモリモジュールタイプのフォームファクタの回路基板が開示される。インラインメモリモジュールタイプのフォームファクタの回路基板は、互いの反対側にある第1の表面および第2の表面を有する。インラインメモリモジュールタイプのフォームファクタの回路基板のうち第1の表面には複数の半導体チップが取り付けられており、これらの半導体チップは、樹脂の中に少なくとも実質的に封止されている少なくとも1つのメモリチップを含む。  (もっと読む)

(もっと読む)

構成可能な仮想ページサイズを有するブリッジデバイス

ディスクリートメモリデバイスと、該デバイスを制御するブリッジデバイスとを備える複合メモリデバイス。ブリッジデバイスは、いくつかのバンクとして編成されたメモリを有し、各バンクは、ページバッファの最大物理的サイズより小さい仮想ページサイズを有する。ページバッファに格納される仮想ページサイズに対応するデータのセグメントのみがバンクに転送される。バンクの仮想ページサイズは、順序付けられた構造を有する仮想ページサイズ(VPS)コンフィギュレーションコマンドで供給され、コマンド内にVPSコンフィギュレーションコードを含むVPSデータフィールドの部分は、最下位バンクから最上位バンクへと順序付けられている異なる複数のバンクに対応する。VPSコンフィギュレーションコマンドは可変サイズであり、最高位のバンク及びそれより低い下位バンクに対するVPSコンフィギュレーションコードのみを含む。  (もっと読む)

(もっと読む)

電話線上のローカルエリアネットワーク用の電話出口とシステム

【課題】アナログ電話通信サービスとローカルエリアデータネットワークとの両者を提供するために電話線配線システムをアップグレードする方法と装置を提供する。

【解決手段】ローカルエリアネットワーク(70,80,90、110,112)において、電話コネクター(14a、14b、14c)と、該ネットワークへのデータ端末装置の接続を可能にするデータコネクター(113a、113d)と、を有するネットワーク出口(31a、31b、31c、31d)を用いて、電話通信信号と同時に住宅又は他の建物内の電話配線を使用する。該ネットワーク出口は該媒体を横切って高い周波数のバンドにアクセスするために高域フィルタ(22a、22b、22c)を使用するが、該標準電話サービスは該同じ媒体を横切って低い周波数の音声/アナログ電話通信バンドにアクセスするために低域フィルタを使用する。

(もっと読む)

単一電話ライン上の電話通信システム

【課題】交換器の特徴をサポートし、多数の外部ライン用への容易な拡張を可能にする、住宅又は他の建物内の単一の電話ライン上の、改良された電話システム(10)を開示する。

【解決手段】多数の音声チャンネルを搬送する、ローカルデータ通信ネットワーク用媒体として現在の電話配線が使用される。各出口(88a、105a)では、1つ以上の音声チャンネルが標準電話ラインインターフエースに変換される。該データ通信ネットワークから分離された該スペクトラムのより低いバンドを使用することによりライフライン機能が実現され、そして該出口内の専用コネクター(91)がこのバンドへのアクセスを提供する。外部電話フイーダー(86a、86b)は該家庭内データ通信ネットワークへインターフエースするためにデジタル形式に変換される。

(もっと読む)

ディスクリートメモリデバイスをシステムに接続するためのブリッジデバイスを有する複合メモリ

ディスクリートメモリデバイスと、それらのメモリデバイスと互換性のないフォーマット又はプロトコルを有するグローバルメモリ制御信号に応答してディスクリートメモリデバイスを制御するためのブリッジデバイスとを含む複合メモリデバイス。ディスクリートメモリデバイスは、ネイティブの又はローカルのメモリ制御信号に応答する、市販のメモリデバイス若しくはカスタムメモリデバイスとし得る。グローバルメモリ制御信号及びローカルメモリ制御信号は、コマンドと、それぞれが別々のフォーマットを有するコマンド信号とを含む。複合メモリデバイスは、ディスクリートメモリデバイスとブリッジデバイスとからなる半導体ダイを含むSIPを備えるか、またはパッケージ化されたディスクリートメモリデバイスを有するプリント基板と、そのプリント基板に実装されたパッケージ化されたブリッジデバイスとを備えることができる。  (もっと読む)

(もっと読む)

41 - 50 / 106

[ Back to top ]