サムソン エレクトロ−メカニックス カンパニーリミテッド.により出願された特許

221 - 230 / 1,585

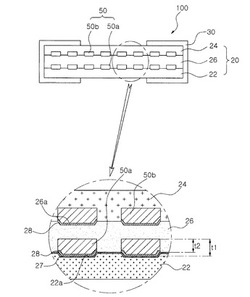

コイル部品及びその製造方法

【課題】コイルと基板との結合力を確保できるコイル部品及びその製造方法を提供する。

【解決手段】コイル部品は、第1の基板層22と、当該第1の基板層22の上に積層される絶縁層26と、当該絶縁層26の上に積層される第2の基板層24と、を含む基板部20と、上記第1の基板層22と上記絶縁層26との間及び上記絶縁層26と上記第2の基板層24との間にそれぞれ介在されるコイル層50と、を含む。

(もっと読む)

出力駆動回路及びトランジスタ出力回路

【課題】本発明は、出力駆動回路及びトランジスタ出力回路を提供する。

【解決手段】第1のスイッチ113のオン動作によって駆動され、出力トランジスタのゲートに高電圧電源を供給する第1のトランジスタ111を含む第1の駆動回路部110と、第1のスイッチ113と相補的に動作する第2のスイッチ133のオン動作によって生成されたワンショットパルスによって駆動され、出力トランジスタのゲート−ソースのキャパシタンスを放電させる第2のトランジスタ131を含む第2の駆動回路部130と、第1の駆動回路部110と並列されるように高電圧電源端と出力トランジスタのゲートとの間に配置され、第2のスイッチ133のオン動作によって放電した出力トランジスタのゲート電位を保持させる出力駆動電圧クランピング部150とを含む。

(もっと読む)

電気化学キャパシタ用電極及びこれを含む電気化学キャパシタ

【課題】低抵抗、高出力の電気化学キャパシタを実現するための電気化学キャパシタの電極及びこれを含む電気化学キャパシタを提供する。

【解決手段】本発明によると、ドープされた炭素材料を活物質として使用し、相対的に粒子サイズが大きい活物質の間に粒径サイズが相違した2種の導電材を添加することにより、単位体積当たりの活物質の量を増加させ、高密度の電極を製造することができ、伝導性に優れた導電材の充填密度を高めて低抵抗、高出力の電気化学キャパシタに効果的に使用されることができる。

(もっと読む)

積層セラミックコンデンサ及びその製造方法

【課題】本発明は、誘電層内に形成された内部金属電極層を含み、前記内部金属電極層の間に導電層を含む積層セラミックコンデンサとその製造方法に関する。

【解決手段】本発明によると、10nm以下の非常に薄い導電層を内部金属電極層の間に形成することで、MLCC内部金属層の間の接触を防止してショート発生による製作損失を減らし、熱安定性を向上させることができる。従って、高機能で小型軽量の高容量積層セラミックコンデンサ(MLCC)を要求する市場の需要に対して優れた信頼性を有する。

(もっと読む)

金属粉末、その製造方法、及びその金属粉末からなる内部電極を含む積層セラミックキャパシタ

【課題】本発明は、積層セラミックキャパシタの内部電極に用いられる材料と、誘電層に用いられる材料との収縮率差による様々な問題を解決する。

【解決手段】表面にグラフェン131が不規則に形成された金属粉末121を、積層セラミックキャパシタの内部電極の材料として用いて、グラフェン131が形成されていない金属粉末の表面でのみネッキングが起こるようにし、金属粉末のネッキングを遅延させ、内部電極の収縮を制御することにより、内部電極の厚さを減らし、短絡及びクラックなどを減少させる。

(もっと読む)

薄膜電極セラミック基板及びその製造方法

【課題】本発明は、薄膜電極セラミック基板及びその製造方法に関する。

【解決手段】薄膜電極セラミック基板は、セラミック基板と、セラミック基板の表面に形成されたエッチング防止金属層と、エッチング防止金属層上に形成された薄膜電極パターンと、薄膜電極パターン上に形成されたメッキ層と、を含み、薄膜電極パターンの各エッジ部は前記エッチング防止金属層と接することを特徴とする。薄膜電極セラミック基板は、セラミック基板の表面に陰刻形状のエッチング防止金属層を形成することにより、セラミック基板の表面と薄膜電極パターンとの間、及び薄膜電極パターンの間でエッチング液によって発生するアンダーカットを防止できる。また、薄膜電極パターンのエッジ部のセラミック基板表面の金属層に対する接着力が向上されることができ、薄膜電極パターン全体の固着力を向上させることができるため、薄膜電極パターンの耐久性及び信頼性を確保できる。

(もっと読む)

多層セラミック基板及びその製造方法

【課題】セラミックシート上の第1の導電パターンと第2の導電パターンとの間に絶縁パターンを介在して複数のセラミックシートを積層する時、層間短絡が発生する問題点を防止することができる多層セラミック基板及びその製造方法を提供する。

【解決手段】複数のセラミックシート100a〜100dが積層されたセラミック積層体で構成された多層セラミック基板100は、セラミックシート100a〜100dに形成された第1の導電パターン120a〜120dと、第1の導電パターン120a〜120dを取り囲む第2の導電パターン140a〜140dと、第1の導電パターン120a〜120dと第2の導電パターン140a〜140dとの間に介在する絶縁パターン160a〜160dとを含む。

(もっと読む)

半導体パッケージ基板

【課題】放熱効果及び層間熱膨張係数の差から発生する反り現象を防止できるとともに、層間熱膨張係数の差による内部変形率の差から発生する内部クラックを防止できる半導体パッケージ基板を提供する。

【解決手段】ベース基板110と、ベース基板110の上部に実装される実装材120と、ベース基板110と実装材120との間に形成される接着層140と、を含み、接着層140は、熱伝導性接着剤141と、熱伝導性接着剤141の外周に形成される軟性接着剤143と、を含むものである。

(もっと読む)

半導体回路

【課題】本発明は、ハイレベルの入力信号に混入されたローレベルのノイズ及びローレベルの入力信号に混入されたハイレベルのノイズをより効果よく取り除くことができる半導体回路を提供する。

【解決手段】 入力信号を所定時間遅延して出力する遅延部120、220、320と、該入力信号のレベルによって電圧を充放電させる電圧調整部140、240、340と、該入力信号のレベル及び遅延部120、220、320から出力される信号のレベルを用いて生成された信号によって、電圧調整部140、240、340の充放電動作を制御する組合せ部160、260、360とを含む。

(もっと読む)

薄膜電極セラミック基板及びその製造方法

【課題】本発明は、薄膜電極セラミック基板及びその製造方法に関する。

【解決手段】本発明による薄膜電極セラミック基板は、セラミック基板と、前記セラミック基板に形成された薄膜電極パターンと、前記薄膜電極パターンに形成されたメッキ層と、を含み、前記メッキ層は、前記薄膜電極パターンの上部及び両側面に形成されることを特徴とする。本発明による薄膜電極セラミック基板は、薄膜電極パターンの上部及び両側面にメッキ層を形成したり、またはセラミック基板の表面に陰刻形状のエッチング防止金属層を形成することにより、セラミック基板の表面と薄膜電極パターンとの間、及び薄膜電極パターンの間でエッチング液によって発生するアンダーカットを防止することができる。

(もっと読む)

221 - 230 / 1,585

[ Back to top ]