Fターム[2G132AA02]の内容

Fターム[2G132AA02]に分類される特許

1 - 20 / 59

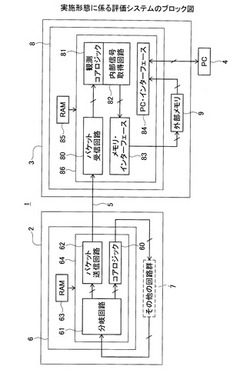

評価システム

【課題】製品ボードに搭載される製品FPGAの端子数に制限されず、内部信号の観測を可能とし、製品FPGAを製品ボードに搭載された実使用状態で論理検証することが可能な評価システムを提供することを課題とする。

【解決手段】評価システム1は、製品ボード2、評価ボード3、およびそれらを接続するシリアル・インターフェース5を備える。製品ボード2に搭載される製品FPGA6はコアロジック60に入力される外部入力信号を分岐する分岐回路61を備える。評価ボード3は観測FPGA8を備える。観測FPGA8はコアロジック60と論理的に等価な観測コアロジック81および観測コアロジック81の内部信号を取得する内部信号取得回路82を備える。コアロジック60の実動作に供される外部入力信号が評価ボード3に送られ観測コアロジック81がコアロジック60の実動作と等価に動作する。その時の内部信号を取り出し論理検証を行う。

(もっと読む)

マルチステージ・テスト応答コンパクタ

【課題】より高い圧縮比を提供し得る圧縮スキームを提供する。

【解決手段】いわゆる「Xプレス」テスト応答コンパクタ110、152は、オーバードライブ・セクションとスキャンチェーン選択ロジックとを含む。実施形態は約1000倍の圧縮比を提供する。例示的な実施形態は、従来のスキャンベースのテストシナリオとほぼ同じカバレッジおよびほぼ同じ診断分解能を維持できる。スキャンチェーン選択スキームのいくつかの実施形態は、テスト応答で発生してコンパクタに入る未知状態を有意に減らすことができ、または完全に排除できる。また、オンチップ・コンパクタ回路の実施形態および選択回路をマスクする制御回路網を生成する方法も開示する。

(もっと読む)

プログラム可能論理デバイス及びその試験方法

【課題】内蔵の記憶装置の試験回路を自動的に作成し、その試験回路を用いて記憶装置の試験を自動的に行うことで、記憶装置の試験にかかる時間を短縮することが可能なプログラム可能論理デバイスを提供する。

【解決手段】データを記憶する記憶部1を備える。論理回路記憶部2は、記憶部1への書き込み及び読み出しを伴うデータ処理を行う論理回路である内部回路を格納する。部品回路記憶部5は、記憶部1の試験のための部品回路を予め記憶しておく。ピン情報記憶部3は、記憶部1のピン情報を取得する。試験部4は、ピン情報及び部品回路を基にメモリ試験回路を生成し論理回路記憶部2に格納させ、メモリ試験回路を用いて記憶部1の試験を行う。

(もっと読む)

システムインパッケージ

【課題】サイズやコストを増大させることなく、テスト容易なシステムインパッケージを実現する。

【解決手段】テスト容易化回路内装SIP1bは、少なくともその1つに集積回路チップ2が搭載された複数のコア基板3,4b,5を、絶縁樹脂層7を介して貼り合わせて構成するとともに、コア基板3,5に形成された配線層31,51を、スルーホール6を介して接続して構成される。このうち、コア基板4bには、半導体層が形成されており、コア基板4bには、その半導体層を用いたトランジスタ素子が形成され、さらに、そのトランジスタ素子がコア基板4bに含まれる配線層の配線で接続されることによって、集積回路チップ2のテストを容易化するためのテスト容易化回路が形成されている。

(もっと読む)

基板

【課題】他の基板とシリアルケーブルを介して通信を行う際の不具合に対処できる基板を提供することを目的とする。

【解決手段】WDT_IC21は、FPGA20によって所定時間毎にクリアされない場合、モノステーブルマルチバイブレータ_IC22にアクティブ信号を出力する。モノステーブルマルチバイブレータ_IC22は、アクティブ信号を取得するとパルス信号を出力する。パルス信号によりFPGA20が再コンフィギュレーションしIO基板200が再起動する。また、パルス信号によりカウンタ_IC24のカウント値がインクリメントされる。FPGA20が再コンフィギュレーションしてもWDT_IC21をクリアできない場合、カウンタ_IC24のカウント値がインクリメントされ続ける。カウント値が所定の閾値に達したときにエラー表示部25が起動し異常を報知する。

(もっと読む)

フーリエ変換回路、逆フーリエ変換回路及びフーリエ変換回路検証方法

【課題】フーリエ変換回路の検証工数を削減すること。

【解決手段】回転因子記憶部2が、フーリエ変換処理に用いられる回転因子を記憶し、符号反転部3が、回転因子記憶部2に記憶された回転因子のQ成分の符号を反転させる。そして、フーリエ変換処理部4が、所定の入力部を介して入力されたデータに対して、回転因子記憶部2に記憶された回転因子を用いてフーリエ変換処理を実行する。さらに、フーリエ変換処理部4が、フーリエ変換処理の結果に対して、回転因子記憶部2に記憶された回転因子のI成分と符号反転部3によって符号が反転された回転因子のQ成分とを用いて逆フーリエ変換処理を実行する。そして、判定部5が、フーリエ変換処理部4による逆フーリエ変換処理の結果と図示しない入力部を介して入力されたデータとが一致するか否かを判定する。

(もっと読む)

FPGAの異常診断方法及び装置

【課題】充分に高い診断精度を確保することが可能なFPGAの異常診断方法及び装置を提供すること。

【解決手段】FPGA1を構成する全ての回路ブロックCIRa〜CIRdにはそれぞれカウンタCOUa〜COUdが設けられており、これらはカウンタCOUa,COUb,COUd,COUcの順に順次直列接続されてカウンタ直列接続体を形成している。発振器2からの発振信号は、I/OブロックIOaの入力ピンを介してカウンタCOUaに入力され、また、カウンタCOUcからは、I/OブロックIOcの出力ピンを介して、順次分周された発振信号がカウンタクリア信号としてウォッチドッグタイマ3に出力される。ウォッチドッグタイマ3の動作に基づき正常と診断した場合には、全ての回路ブロックが必ず正常であることが保証される。

(もっと読む)

半導体装置およびその製造方法

【課題】中間配線層までの配線が行われているマスターウェーハを使用しても、最終製品の歩留りを高い精度で予測することができる半導体装置およびその製造方法を提供する。

【解決手段】多層配線構造の中間配線層までを使用して機能動作を行うように設計された機能ブロック(SRAMマクロ11、ロジックブロック12、ロジックブロック13、IPブロック14)を搭載したマスターウェーハを使用するマスタースライス方式の半導体装置は、この中間配線層に試験用パッドTPを備え、この試験用パッドTPが、各機能ブロックに接続される。

(もっと読む)

半導体装置とテスト方法

【課題】競合評価に要する時間を短縮し、タイミング競合評価を実現する半導体装置の提供。

【解決手段】 上位装置であるCPU(200)から評価対象マクロ(120)に対するアクセスを受け、前記アクセスが予め定められた競合評価開始アクセスであることを検出すると、前記アクセスに対して、所定のタイミングで、競合評価用の命令を前記評価対象マクロに投入するテストマスタ(110)を備える。テストマスタは、前記アクセスに対する評価対象マクロの動作の開始時点から終了直前までの時間範囲の一部又は全部にわたって、前記評価対象マクロに対する前記競合評価用の命令の投入のタイミングを可変させる。

(もっと読む)

演算回路の検証システム及び検証方法

【課題】演算回路の検証を容易にし、且つ所要時間の短縮を図る。

【解決手段】検証対象の演算回路31を表す回路記述から、配線を表す“wire”等の記述を、内部信号を表す記述として抽出し(ステップS11)、これに基づき演算回路31の内部信号の配線と選択回路32の入力端子とを接続して、選択回路32が接続された演算回路31を表す回路記述を生成する(ステップS12)。生成した回路記述をもとに、選択回路32が接続された演算回路31を半導体集積回路7aに構築する(ステップS14)。また、選択回路32の入力端子とこれに接続された内部信号の配線との対応を表すマッピングデータを生成し表示する(ステップS13)。設計者が、マッピングデータを参照し、所望の内部信号に対応するアドレスを選択回路32に対して指定することで、指定した内部信号が選択され半導体集積回路7aの出力端子から出力される。

(もっと読む)

積層ダイ構造の試験のための装置および方法

集積回路装置は、積層ダイ(102)とベースダイ(101)とを含み、ベースダイは、集積回路装置の試験のためのスキャンチェーンを実現するために、ベースダイのテストロジック(305,104)に直接的に結合するプローブパッド(306,111−116)を有する。ベースダイは、さらに、ベースダイの背面に配置されるコンタクト(107)と、コンタクトに結合されるとともにベースダイのプログラマブルロジック(550,314,105)に結合されるダイ貫通ビア(310,121−128)を含む。ベースダイは、また、テスト入力に結合されるように構成された第1のプローブパッド(111)と、テスト出力に結合するように構成された第2のプローブパッド(112)と、制御信号に結合するように構成された第3のプローブパッド(113)とを含む。ベースダイのテストロジック(305)は、スキャンチェーンを実現するために、積層ダイのさらなるテストロジック(405)に結合するように構成されて。スキャンチェーンを実現するために、プログラマブルロジック(550,314,105)の構成を必要としないように、プローブパッド(306,111−116)は直接的にテストロジック(305,104)に結合される。  (もっと読む)

(もっと読む)

LSI評価ボード装置

【課題】 本発明の課題は、プログラムされたユーザー論理を用いたLSIのプロトタイピングにおいて、評価精度を向上させることを目的とする。

【解決手段】 上記課題は、2つのデバイスで構成されるプロトタイピング環境を実装するLSI評価ボード装置は、有効なバストランザクションの検出に応じて、前記2つのデバイスの動作に係る回路構成のクロック停止を指示する第一指示回路と、前記クロック停止の指示に応じて、前記デバイス間を接続する外部バスに係る回路構成を除く前記2つのデバイスの動作に係る回路構成のクロックの停止を制御するクロック制御回路とを有するLSI評価ボード装置により達成される。

(もっと読む)

テストパターン作成方法およびプログラム

【課題】プログラマブルなLSIのテストを行う場合にテストパターンが長大化する。

【解決手段】テストパターンを使って内部論理回路の故障を検出させるということは、故障があった時と無かった時で出力結果が変わる入力の組合せが入れられれば良いことであり、個々の故障モードを検証するのに全ての入力信号が必要な訳ではなく、その一部しか使用していないことが多く、故障検出を行うのに冗長な入力信号が存在している可能性があることに着眼した。そこで、故障検出率を下げることなく論理回路の故障を検出させるために必要な入力信号の入力条件の中から共有できる入力端子の組合せ(論理回路2ではin1,in2,in4,in7およびin3,in5,in6)を見つけ、それらの入力信号を結線させた。

(もっと読む)

ステートマシン

【課題】ステートマシンのテストにおいて何らかの異常が発生した際には、高度な解析手法ではなく、どの遷移状態(ステート)で異常が発生したかを知ることができるステートマシンを提供する。

【解決手段】ステートマシン35は、あらかじめ決められた複数の状態を決められた条件に従って決められた順番で遷移してゆくステートマシンであり、ステートマシン35の遷移状態を示す信号60を出力する信号出力部37と、信号出力部37から外部へ出力する遷移状態を示す信号60を保持する信号保持部38と、を備える。

(もっと読む)

評価方法および評価装置

【課題】被評価回路の信号を計測する回路の規模や、計測結果を転送する回路の規模を小さくすること。

【解決手段】カウント区間では、被評価回路2の被評価信号8,9を計測回路6,7で計測し、その計測結果をRAM10に格納する。カウント区間よりも長い評価区間では、RAM10から前回のカウント区間での計測結果を読み出す。加算器13により、RAM10から読み出された、前回のカウント区間での計測結果に、計測回路6,7から転送されてきた今回のカウント区間での計測結果を加算する。その加算結果をRAM10の元の場所に書き戻すことによって、RAM10に、評価区間における被評価信号8,9の計測結果の累積加算値を格納する。

(もっと読む)

セグメントドライバの検査方法及びその検査システム

【課題】セグメントドライバを効率良く検査できるようにしたセグメントドライバの検査方法及びその検査システムを提供する。

【解決手段】セグメントドライバ2に接続された表示メモリ3にテストパターンを書き込んで、セグメントドライバ2が有する複数のセグメント端子2a〜2h…から信号を出力させる工程、を含み、テストパターンは、数のセグメント端子2a〜2h…から出力される信号が当該端子間で全て同じ電圧レベルとなるように生成されている。このような方法であれば、例えば、出力信号の電圧レベルとして「1」と「0」とを同時に測定することができないような、通常のテスタを用いて検査を行う場合でも、各セグメント端子2a〜2h…を同時に測定することができる。

(もっと読む)

リコンフィギャラブルアレイに埋め込まれた特定用途向け機能ブロックのテスト装置及びテスト方法

【課題】ユーザプログラマブルファブリック内に埋め込まれた特定用途向け機能ブロックをテストする方法及び装置を提供する。

【解決手段】ユーザプログラマブルファブリックのコンフィギュレーションデータ制御手段の出力を特定用途向け機能ブロックの入力にルーティングする工程と、特定用途向け機能ブロックを構成するためのコンフィギュレーションデータをユーザプログラマブルファブリックのコンフィギュレーション制御手段に送る工程と、コンフィギュレーションデータを特定用途向け機能ブロックのコンフィギュレーションメモリ手段に転送する工程と、特定用途向け機能ブロックをテストするためのテストデータを、ユーザプログラマブルファブリックのコンフィギュレーション制御手段に送る工程と、ユーザプログラマブルファブリックのコンフィギュレーションデータ制御手段の出力を、特定用途向け機能ブロックの入力にルーティングする工程とを備えている。

(もっと読む)

集積回路及びそのモニタ信号出力方法

【課題】集積回路及びそのモニタ信号出力方法に関し、複数の内部信号を選択してより少ない外部端子数でモニタ信号を出力し、また、モニタ対象の内部信号を容易に選択可能にする。

【解決手段】集積回路10内部の各機能回路部11から出力される内部信号を外部装置20に出力してモニタする際、モニタ選択部12によりモニタ対象の内部信号を選択し、パラレル信号からシリアル信号に変換してモニタ信号を出力する。該モニタ信号と共に、パラレル信号からシリアル信号への変換のフォーマットを示す識別子情報TAGを集積回路10の外部端子から出力する。外部装置20は集積回路10の外部端子から出力される識別子情報TAGを基に、シリアルパラレル変換数判定部21によりパラレル信号からシリアル信号への変換のフォーマットを判定し、該フォーマットに応じてモニタ展開部22によりモニタ信号をシリアル信号からパラレル信号変換して出力する。

(もっと読む)

半導体装置

【課題】Loopbackテストの際に電圧振幅マージン不足の半導体装置が次工程へと流出するのを防止する。

【解決手段】シリアライザ17は、テストモード期間にクロック信号CLK1に応じてパタン発生器20が出力するパラレルのテストパタン信号をシリアル信号に変換して出力バッファ16よりテスト治具側の外部ループバックパスへ出力する。CPU21は、遅延制御信号DLC1,DLC2によって一方の可変遅延素子VDL1,VDL2の遅延時間を制御する。入力バッファ10の出力であるテストパタン信号VRxとLSIテスタ等より印加される外部基準電圧Vrefとの差動信号VRx1がCDR12に印加され、クロック信号CLK2が生成される。両信号VRx,CLK2の一方の位相が変更されて、外部基準電圧Vrefの値毎にタイミングマージンがチェックされる。

(もっと読む)

結線チェック方法、プログラマブルデバイスおよび回路構造ファイル生成プログラム

【課題】バックボード上のスロットを介して互いに接続される複数のFPGA間の結線を容易にチェックすることができる結線チェック方法、プログラマブルデバイスおよび回路構造ファイル生成プログラムを提供すること。

【解決手段】各々のFPGAが、自身が有する出力端子から、かかる出力端子であることを識別できる端子データを出力し、入力端子に端子データが入力された場合に、受信した端子データと、端子データを受信した入力端子に対応する比較データとが同一であるか否かを判定し、判定結果を所定の結果表示部に表示する。

(もっと読む)

1 - 20 / 59

[ Back to top ]