Fターム[2G132AC14]の内容

Fターム[2G132AC14]の下位に属するFターム

バウンダリスキャン(境界走査試験) (123)

パーシャルスキャン (1)

Fターム[2G132AC14]に分類される特許

1 - 20 / 508

出力制御スキャンフリップフロップ、それを備えた半導体集積回路及び半導体集積回路の設計方法

スキャン・チェーン用動的クロック領域バイパス

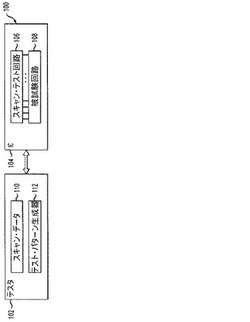

【課題】スキャン・テスト回路およびスキャン・テスト回路を使用して試験を受けるさらなる回路を備える集積回路を提供すること。

【解決手段】スキャン・テスト回路は、それぞれ別個のクロック領域に関連した複数のサブチェーンを有する少なくとも1つのスキャン・チェーン、および1つまたは複数のサブチェーンを選択的にバイパスするように構成されたクロック領域バイパス回路を備える。スキャン・チェーンは、スキャン・シフト・モードの動作において、サブチェーンを全部よりは少なく含む直列シフト・レジスタを形成するように構成可能であり、サブチェーンの少なくとも残りの1つが、スキャン・シフト・モードにおいて直列シフト・レジスタの部分でないように、クロック領域バイパス回路によりバイパスされる。特定のクロック領域に関連するスキャン・チェーンの部分を選択的にバイパスすることにより、クロック領域バイパス回路は、スキャン・テスト期間の試験時間と電力消費を減らす役割を果たす。

(もっと読む)

半導体集積回路設計装置、半導体集積回路設計方法、および、プログラム

【課題】半導体集積回路において、スキャンテスト時における消費電力を削減する。

【解決手段】半導体集積回路設計装置は、第1のスキャンFFのデータ入力端子に接続された第1のロジックコーンの入力端子数である第1の入力端子数と、第1のロジックコーンにデータを設定する第2のスキャンFFのデータ入力端子に接続された第2のロジックコーンの入力端子数である第2の入力端子数とを比較するデザイン解析部と、複数のスキャンFFのそれぞれのデータ入力端子に接続されたロジックコーンの入力端子数、および、複数のスキャンFFのそれぞれを第1のスキャンFFとした場合の前記比較結果に応じて、複数のスキャンFFを複数のグループに分類し、複数のグループのそれぞれに含まれるスキャンFFを相互に接続したスキャンチェーンを複数のグループのそれぞれについて生成するスキャンチェーン構築部と、を備える。

(もっと読む)

半導体テスト回路

【課題】スキャンチェーンを構成する回路でバーンイン試験を行う際に、シフトモードとキャプチャモードを切り替えるスキャンモードコントロール信号が接続された回路に対してもストレス印加を可能にする半導体テスト回路を提供する。

【解決手段】半導体テスト回路は、シフトモードとキャプチャモードを交互に切り替える内部スキャンモードコントロール信号と、スキャンチェーンのスキャンフリップフロップ回路に供給する内部クロック信号を生成するスキャンチェーン制御信号生成部を備える。スキャンチェーン制御信号生成部は、スキャンフリップフロップ回路の出力を遷移させる内部クロック信号のエッジのタイミングにおいて、内部スキャンモードコントロール信号がシフトモードになるように、内部スキャンモードコントロール信号と内部クロック信号の相互のタイミングを制御する。

(もっと読む)

半導体設計方法及び半導体設計装置

【課題】フリップフロップ追加による利益と、スキャンFFの段数増加による不利益と、を考慮に入れ、スキャンテスト回路の設計を行う半導体設計方法が、望まれる。

【解決手段】複数のスキャンFFから構成されるスキャンテスト回路の設計方法は、複数のスキャンFF間の遅延値を抽出することで、スキャンテスト回路の動作レート候補値を複数算出する第1の工程と、中継用フリップフロップの追加を仮定し、複数の動作レート候補値をそれぞれ使用して、スキャンテストの実施に必要な時間をスキャンシフト時間として算出し、スキャンシフト時間に基づき、中継用フリップフロップを追加することの効果が最も高い動作レート候補値を、中継用フリップフロップの追加後のスキャンテスト回路に適用する動作レートとして選択する第2の工程と、動作レートを満たすように、複数のスキャンFF間に中継用フリップフロップを追加する第3の工程と、を含んでいる。

(もっと読む)

フリップフロップ回路

【課題】セレクタ付フリップフロップ回路の入力信号がラッチ回路へと伝播するまでに、選択信号により制御されるスイッチ回路とクロック信号により制御されるスイッチ回路とを介するため、入力信号がラッチへと伝播するまでの時間が長い。

【解決手段】セレクタ付フリップフロップ回路100は、選択信号SA、クロック信号CKおよび複数の入力データが入力され、複数の入力データのうち1つを出力するフリップフロップ回路であって、選択信号SAおよびクロック信号CKに基づいて、第1の制御信号CAを生成する第1の論理回路102と、第1の制御信号CAにより制御される第1のスイッチ回路101と、第1のスイッチ回路101を介して、複数の入力データから選択された一の入力データを保持する第1のラッチ回路103とを有する。

(もっと読む)

出力制御スキャンフリップフロップ、それを備えた半導体集積回路及び半導体集積回路の設計方法

【課題】制御信号を必要とせずにスキャンテスト時のピーク消費電力を低減することが可能な出力制御スキャンフリップフロップを提供すること。

【解決手段】本発明にかかる出力制御スキャンフリップフロップは、通常動作時に第1データを、シフト動作時にテストデータを、クロック信号に同期して取り込んで出力するスキャンフリップフロップ203と、シフト動作時にスキャンフリップフロップ203から出力されたデータを、クロック信号に同期して取り込んで出力するスキャンフリップフロップ204と、通常動作時にスキャンフリップフロップ203から出力されたデータを出力データとして生成し、シフト動作時にスキャンフリップフロップ203,204からそれぞれ出力されたデータに基づいて論理値変化率の低い出力データを生成するゲーティング回路と、を備える。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において消費電力を低減するとともに、ノイズの発生を低減する。

【解決手段】半導体集積回路は、複数のDFFを有し、その少なくとも1つが冗長回路とされる。半導体集積回路が通常動作モードである際に、ANDゲート1によって冗長回路であるDFF3−3に印加されるクロック信号を停止する。冗長回路へのクロック信号が停止されると、当該冗長回路においてクロック信号が停止された状態における冗長回路のドレイン−グランド間容量よりもその容量を増加させる。

(もっと読む)

半導体回路及びテスト方法

【課題】スキャンチェーンから出力される複数の被試験回路の試験結果情報に基づいて、不良の被試験回路を効率的に特定する半導体回路及びテスト方法を提供する。

【解決手段】複数の被試験回路と、試験回路に対応して設けられた複数の第1のラッチ回路と、第2のラッチ回路と、パターンアドレスに対応して入力信号が規定されたテストパターンのパターンアドレス順に入力される入力信号に基づいて、被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、複数の良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を第2のラッチ回路に出力する総合判定回路と、複数の第1のラッチ回路と第2のラッチ回路とを、第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、スキャンチェーンは、入力信号がスキャン出力モードを示す時に、第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する。

(もっと読む)

スキャンパタン作成手法、プログラム、スキャンパタン作成装置、テスタ、及びテスト方法

【課題】スキャンテストに要する時間を削減するテストパタン作成方法を提供する。

【解決手段】テストパタン作成方法は、組み合わせ論理回路と少なくとも一つのスキャンチェーンとに関する情報を、記録媒体から読み出し、少なくとも一つのスキャンチェーンの入力側に近いフリップフロップから順番に抽出し(ステップS21)、抽出したフリップフロップがスキャンキャプチャ動作によって組み合わせ論理回路から取り込むキャプチャデータと照合する期待値の必要性を判定し(ステップS22〜S25)、期待値が不要と判定されたフリップフロップが入力側から連続して存在するフリップフロップの数を取得し(ステップS27)、スキャンチェーンに含まれるフリップフロップの総数と、取得したフリップフロップの数との差分を、スキャンキャプチャ動作後のスキャンシフト回数として決定する(ステップS28)。

(もっと読む)

遅延スキャンテスト方法、半導体装置及び半導体装置の設計方法

【課題】従来のスキャンテスト方法では、電源電圧変動を抑制しながら動作クロックの周波数の高い半導体装置をテストできない問題があった。

【解決手段】本発明のスキャンテスト方法は、クロック信号SCLKをスキャンフリップフロップ21〜2nに入力して第1のテストパターンをスキャンフリップフロップ21〜2nに設定し、クロック信号SCLKよりも周波数の高いクロック信号RCLKをスキャンフリップフロップ21〜2nに入力すると共に、スキャンフリップフロップ21〜2nをクロック信号RCLKによらず保持する値を維持するホールドモードに制御し、ホールドモードを解除すると共にスキャンフリップフロップ21〜2nをテスト対象回路の出力に応じて保持する値を更新するテスト結果取得モードに制御し、テスト結果取得モードにおいてクロック信号RCLKを2パルス用いてスキャンフリップフロップ21〜2nに保持されている値を更新する。

(もっと読む)

半導体集積回路装置の試験方法及び半導体集積回路装置

【課題】 半導体集積回路装置の試験方法及び半導体集積回路装置に関し、所定の回路動作を行った状態のまま半導体集積回路装置側の操作で所望の温度に制御する。

【解決手段】 スクリーニング試験前の工程にて測定された半導体集積回路装置の回路毎の電源電流値或いは電流ランクのいずれかにより、前記半導体集積回路装置全体毎または個別の回路動作毎に、適切な周波数に周波数設定し、所望の発熱量になるよう発熱量の制御を行い、スクリーニング試験時に、所定の回路動作を行った状態のまま所望の温度に制御する。

(もっと読む)

半導体集積回路、スキャンフリップフロップ及び半導体集積回路のテスト方法

【課題】稼働中の故障診断の際に内部状態の退避及び復帰を図ることができるとともに、回路規模の増大を防ぐことが可能にする。

【解決手段】本発明に係る半導体集積回路10は、スキャンフリップフロップ210,310と、スキャン制御部100とを備え、スキャンフリップフロップ210は、スキャン制御部100の制御に基づいて、内部状態として保持しているバックアップデータを出力し、のスキャンフリップフロップ310は、スキャン制御部100の制御に基づいて、スキャンフリップフロップ210から出力されたバックアップデータを、スキャンフリップフロップ310内に保持するものである。

(もっと読む)

半導体集積回路

【課題】テスト時の消費電力を低減することができる半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路100は、フリップフロップFF、制御回路10及び排他的論理和ブロックを有する。フリップフロップFFは、テスト入力Tにテストデータ信号TINが入力する。排他的論理和ブロック20は、一方の入力がフリップフロップFFのテスト入力Tと接続され、他方の入力がフリップフロップFFの出力Qと接続される。制御回路10は、排他的論理和ブロック20の出力XORとクロック信号CLKとが入力し、排他的論理和ブロックの出力XORの値に応じてフリップフロップFFへのクロック信号CLKの出力を制御する。

(もっと読む)

故障箇所推定装置と方法並びにプログラム

【課題】スキャンテスト設計が施された機能ブロックと付加回路とを含む論理回路全体を故障診断を可能とし、診断処理時間を大幅に短縮可能とする装置、方法の提供。

【解決手段】論理回路内のスキャンフリップフロップで構成されるスキャンチェーンの構成情報、論理回路の設計情報を入力データ1として入力し、論理回路においてパラレル領域以外の回路部をシリアル領域として抽出することで、前記論理回路を前記パラレル領域とシリアル領域に分割する回路分割手段2と、正常回路における論理値を期待値として求める期待値計算手段3と、テストパタンに対する論理回路のテスト出力を入力データ1として入力し、テスト出力および、シリアル領域とパラレル領域の期待値を用いて、パラレル領域およびシリアル領域を故障診断し、出力部に出力する故障診断手段4とを備える。

(もっと読む)

半導体集積回路

【課題】遷移スキャンテストにおいて遷移故障を短時間で精度良く検出できる半導体集積回路を提供する。

【解決手段】半導体集積回路1において、高速クロック動作ブロック(高速クロックグループ)及び低速クロック動作ブロック(低速クロックグループ)という、動作周波数の異なるブロック間にスキャンチェーンを配し、半導体集積回路1の遷移スキャンテストのキャプチャ動作時において、遷移スキャン用クロック制御回路7によって低速クロックグループのスキャンFFに供給されるクロックを止めるよう構成する。これにより、低速クロックグループのスキャンFFにおける信号マスクを不要にする。

(もっと読む)

半導体集積回路および半導体集積回路の設計方法

【課題】半導体集積回路の面積を増大させることなく、配線性のよいテスト専用回路の電源遮断を実現する半導体集積回路を提供する。

【解決手段】テスト実行時のみ動作するテスト専用回路を有する半導体集積回路1であって、当該半導体集積回路1の内部回路領域(内部制御回路部100)に電源を供給する通常電源(通常動作用電源)104と、当該内部回路領域の全面にメッシュ状に配線され、テスト専用回路に電源供給するテスト用電源103と、テスト用電源103と通常電源104とを接続及び遮断して、通常電源104からテスト用電源103への電源供給を制御する電源遮断スイッチ109と、を備える。

(もっと読む)

半導体集積回路及びその制御方法

【課題】精度の高いディレイテストを行うことが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路1は、クロック信号CLKに同期して動作する複数のレジスタを有する内部回路11と、クロック信号CLKに同期して動作し第1ノードから第2ノードまでの信号伝搬時間を測定する遅延測定回路12と、遅延測定モードの場合に、遅延測定回路12に対してのみクロック信号CLKを供給し、電圧検出モードの場合に、内部回路11及び遅延測定回路12に対してクロック信号CLKを供給するクロック供給回路13と、を備える。

(もっと読む)

状態保持回路における状態保全性の検証

【課題】 本発明は、データ処理動作を行うよう構成されたデータ処理回路を備えたデータ処理装置を提供する。

【解決手段】 複数の状態保持回路がデータ処理回路の一部を形成し、これらの回路は、低電力モードに入ったデータ処理回路のそれぞれのノードにてそれぞれの状態値を保持するよう構成される。1以上のスキャンパスは、状態値がそれぞれのノードにスキャンインまたはアウトされてもよいよう、複数の状態保持回路を直列に接続する。複数のパリティ情報生成要素はスキャンパスに結合され、状態保持回路によってそれらそれぞれのノードにて保持されたそれぞれの状態値を示すパリティ情報を生成するよう構成される。複数のパリティ情報生成要素は、それぞれの状態値の一つが変化した場合にパリティパスの出力にて生成された出力パリティ値を反転するよう、1以上のパリティパスを提供し、状態保持回路によって保持された状態値の保全性の外部指示を提供するよう配置される。

(もっと読む)

試験可能な不揮発論理ゲート

【課題】既存の設計ツールを適用してテストを行うことができる不揮発論理ゲートを提供する。

【解決手段】本不揮発論理ゲートは、抵抗値が記憶される不揮発性抵抗素子を有する不揮発メモリ回路と、テストデータ入力信号を受け取るテストデータ入力端子、テストイネーブル信号を受け取るテストイネーブル信号端子、トランジスタからなるネットワーク回路、及び抵抗値に基づいてネットワーク回路に流れる電流差に応じた結果を出力するセンス回路、を有する演算回路と、を備え、テストイネーブル信号により選択されるテストモードにおいて、テストデータ入力端子はセンス回路の入力端子と電気的に接続し、テストデータ入力信号をセンス回路に供給できること、を特徴とする。

(もっと読む)

1 - 20 / 508

[ Back to top ]