Fターム[2G132AL04]の内容

Fターム[2G132AL04]に分類される特許

1 - 20 / 109

電子回路検査装置、電子回路検査方法、回路基板検査装置および回路基板検査方法

電子部品、測定方法および監視装置

【課題】接合部の損傷を事前に検知する。

【解決手段】電子部品は、第1部材と、第2部材と、接合部と、測定部とを備える。第1電極は、第1部材上に形成される。第2電極は、第1部材上の、第1電極が形成された領域の周囲の領域に形成される。第3電極は、第2部材に形成される。第2電極が第2部材に形成され、第3電極が第2部材の第2電極が形成された領域の周囲の領域に形成されてもよい。接合部は、第1電極と第2電極と第3電極と接合する。測定部は、第1電極および第2電極のうち少なくとも一方を含む接続経路の電気特性を測定する。

(もっと読む)

半導体装置

【課題】 多様な方式でスキャンテスト経路を形成することができる半導体装置を提供する。

【解決手段】第1チップおよび第2チップを電気的に連結する第1貫通ビアおよび第2貫通ビアと、前記第1チップに配置され、テストデータを受信するとともに前記第1貫通ビアと接続される第1回路部と、前記第1チップに配置され、前記第2貫通ビアおよび前記第1回路部と接続される第2回路部と、前記第2チップに配置され、前記第1貫通ビアと接続される第3回路部と、を含み、前記第1回路部は第1制御信号に応答して前記第1貫通ビアおよび前記第2回路部のうちいずれか一つに前記第1回路の出力信号を出力する。

(もっと読む)

半導体チップ、半導体装置、及びその測定方法

【課題】多数の信号用TSVを有する半導体チップを積層した半導体装置では、個々の信号用TSVを導通試験するのに、膨大な工数がかかっていた。

【解決手段】信号用TSVを直接導通試験するのではなく、信号用TSVに隣接した位置にダミーバンプを配列すると共に、複数の半導体チップ間のダミーバンプを一筆書きで描けるような導通経路で、各半導体チップのダミーバンプを接続する。

導通経路の導通試験により、積層された2つの半導体チップの接合面における接合不良を測定、検出できる。

(もっと読む)

配線板、配線板の検査方法

【課題】絶縁板の主面または内部に実装された電子部品の接続検査を簡明化すること。

【解決手段】第1の電子部品が有する第1の電源端子に接続がされるための第1のランドパターンと、第2の電子部品が有する第2の電源端子に接続がされるための第2のランドパターンと、第1の電源端子を除くいずれかの端子に接続がされるための第3のランドパターンを含み、かつ第2の電源端子を除くいずれかの端子に接続がされるための第4のランドパターンを含み、かつ第3のランドパターンと第4のランドパターンとを電気的に接続するように絶縁板に設けられた配線部と、第1のランドパターンに電気的に接続して設けられた、少なくとも一部が主面上に存在する第1の電源リード部と、第2のランドパターンに電気的に接続して設けられた、少なくとも一部が前記主面上に存在し、かつ、第1の電源リード部とは電気的に分離して存在する第2の電源リード部とを具備する。

(もっと読む)

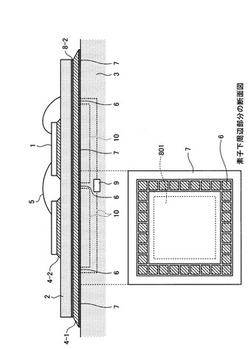

高周波モジュールおよび高周波モジュールの検査方法

【課題】高周波回路チップ上の回路と、モジュールを構成する配線基板上の回路についてその相対位置を検出することによって、容易に実装状態が測定できる高周波モジュールおよび高周波モジュールの測定方法を提供する。

【解決手段】入出力端子6を備えた高周波回路チップ1と、高周波回路チップ1の入出力端子6を、バンプ5を介してフリップチップ接続する接続用パッド7を含む配線部を備えた配線基板2とを備えた高周波モジュールであって、入出力端子の2端子間に接続された、スパイラルインダクタ3sと、スパイラルインダクタ3sに対向する位置に配設され、接地電位に接続された検出用導体4dとを備え、接続用パッド間のインダクタンスを測定することによって、スパイラルインダクタ3sと検出用導体4dとの距離の変化に起因する入出力端子6と接続用パッド7間の距離の変化を測定可能に構成される。

(もっと読む)

集積回路および集積回路の接続不良検出方法

【課題】製品組立後の経年劣化による接続不良を含め、簡単な構成で被実装基板との接続不良を検出する。

【解決手段】集積回路に、同一の電位が与えられる2以上の比較電圧用パッドと、比較電圧用パッドにかかる電圧を比較して、その比較結果に基づいて被実装基板との接続不良の有無を示す信号を出力する比較判別回路とを設け、比較判別回路において、少なくとも2つの比較電圧用パッドにかかる電圧の電位差が所定の値を超えた場合に、接続不良を示す信号を出力させる。

(もっと読む)

半導体試験装置、電気長測定方法

【課題】測定経路端を接地して電気長を測定する場合に、経路に断線があっても測定結果を得られるようにする。

【解決手段】測定経路端を接地して電気長を測定する半導体試験装置であって、測定経路に測定信号を出力する信号発生手段と、測定経路から分岐して入力される入力信号と、任意の閾値電圧とを比較する比較手段と、信号発生手段に測定信号を出力させ、比較手段の入力信号が第1閾値電圧以上となってから第2閾値電圧以下となるまでの時間を計測し、所定時間内に計測された場合には、計測された時間に基づいて測定経路の電気長を算出し、所定時間内に計測されなかった場合には、比較手段の入力信号が第1閾値電圧以上となってから、第1閾値電圧よりも高い第3閾値電圧以上となるまでの時間を計測して、測定経路の異常箇所までの電気長を算出する電気長測定制御手段とを備える。

(もっと読む)

回路基板検査装置および回路基板検査方法

【課題】コンタクトチェックに要する時間を短縮する。

【解決手段】処理部10は、検査対象体21〜25の電極21a,・・,25aとこれに接触させられている端子対31,・・,39との間の接触状態を検査する際に、電圧検出用ライン4a,4bを電圧検出部6から切り離す共に電流供給用ライン3a,3bに電圧検出部6を接続し、電圧検出用ライン4a,4bおよび中継ライン7を介して端子対31,・・,39を直列接続し、端子対31,・・,39の一端に配置されている電流供給端子Hcを電流供給用ライン3aに、他端に配置されている電圧検出端子Hpを電流供給用ライン3bに接続させ、直列接続された各端子対31,・・,39に検査電流Iを供給したときの電流供給用ライン3a,3b間の測定電圧と検査電流Iとに基づいて、直列接続された端子対31,・・,39と対応する電極21a,・・,25aとの間の接触状態を検査する。

(もっと読む)

半導体集積回路のテスト回路及び方法

【課題】ウェハ上の単一チップに形成された貫通ビアの不良の可否をテストすることができ、またパッケージングされた半導体集積回路に形成された貫通ビアの不良の可否をテストすることができる半導体集積回路のテスト回路及び方法を提供する。

【解決手段】半導体集積回路のテスト回路1は貫通ビア100、電圧駆動部200及び判定部300を含む。前記貫通ビア100は入力電圧V1を受信する。前記電圧駆動部200は前記貫通ビア100と連結されて前記入力電圧V1を受信し、テスト制御信号EN_P,EN_Nに応答して前記入力電圧V1のレベルを変化させてテスト電圧VTを生成する。前記判定部300は前記入力電圧V1及び前記テスト電圧VTを比較して結果信号を出力する。

(もっと読む)

ICチップ、半導体部品、検査用プローブ、ハンディマルチテスター、及び通信装置

【課題】TDR検査を安価な構成で実現できるICチップを得ること。

【解決手段】ICチップは、TDR(Time Domain Reflectometry)検査のためのICチップであって、クロック信号を生成するクロック生成部と、前記クロック信号をトリガとしてパルスを発生して検査対象へ出力するパルス発生部と、前記クロック信号を逓倍して逓倍クロック信号を生成する逓倍部と、前記逓倍クロック信号に同期して、前記検査対象からの反射信号をA/D変換して反射データとしてサンプリングするA/Dコンバータと、前記サンプリングされた反射データを記憶するメモリと、外部から読み出しコマンドを受け、前記読み出しコマンドに応じて前記メモリに記憶された反射データを外部に出力する通信制御部とを備えている。

(もっと読む)

半導体装置及びその試験方法

【課題】論理値の反転処理を行う回路をコアチップ側に設けることなく、TSVを含む電流パスラインのショート不良を検出する。

【解決手段】半導体装置10は、第1及び第2の電流パスSa,Sbと、これらとそれぞれ電気的に接続する第1及び第2のラッチ回路100a,100bと、第1のラッチ回路100aに第1のデータD1を供給するとともに、第2のラッチ回路100bに第1のデータとは逆の論理値を有する第2のデータD2を供給するドライバ回路101と、第1のデータD1が第1のラッチ回路100aに供給され、かつ第2のデータD2が第2のラッチ回路100bに供給されない第1の期間と、第2のデータD2が第2のラッチ回路100bに供給され、かつ第1のデータD1が第1のラッチ回路100aに供給されない第2の期間と、が交互に繰り返されるよう、ドライバ回路101を制御する制御回路104と、モニタ回路120とを備える。

(もっと読む)

CMOS論理ICパッケージおよび検査方法

【課題】検査用電極を備えるCMOS論理ICパッケージおよびその検査方法の提供。

【解決手段】パッケージ内の各接続用電極パッドに近接する位置に設けられた検査用電極とバッファゲートを備えるCMOS論理ICパッケージを提供し、プリント配線基板に実装されたCMOS論理ICパッケージの検査用電極に低電圧の検査信号を印加したときの電源電流を測定することによりパッケージ内の接続用電極パッドとプリント配線基板の電極ランド間の開放故障(断線故障および半断線故障を含む)を検査するCMOS論理ICパッケージの検査方法およびそのCMOS論理ICパッケージ。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】一つのTEGで複数方向の位置ずれを検出できるようにする。

【解決手段】この半導体装置は、TEG300を有している。TEG300は、プラグ及び配線のいずれか一方である第1要素と、プラグ及び配線の他方である第2要素を有している。第2要素は、互いに異なる方向から第1要素に面しており、第1要素から離間している。本実施形態において、第1要素はプラグ320であり、第2要素は配線330である。プラグ320は、コンタクトであってもよいし、ビアであってもよい。またプラグ320は、配線330の上に位置していてもよいし、下に位置していてもよい。

(もっと読む)

半導体装置

【課題】自己と他の半導体装置とを接続するための配線の断線を容易に検出することが可能な半導体装置を提供する。

【解決手段】半導体チップ1は、電源ノード5と、接地ノードG1と、ワイヤ13を接続するためのパッド11と、ワイヤ13による半導体チップ51と半導体チップ52との間の電気的接続の不良を検出するための検出回路14とを備える。検出回路14は、電源ノード5とパッド11との間に設けられた電圧発生回路14aと、電源ノード5と接地ノードG1との間に設けられ、パッド11に所定の電圧が印加されることでオンするスイッチ回路SWとを含む。電圧発生回路14aは、ワイヤ13によって半導体チップ51と半導体チップ52との間の電気的接続が不良である場合に、スイッチ回路SWをオンするための電圧をパッド11に印加する。

(もっと読む)

半導体装置

【課題】パッケージ内部の半導体チップが、BGA基板に接触しているか否かを、簡単に把握することが可能技術を提供する。

【解決手段】半導体チップ(2)は、回路接続用電極(4)と、回路から独立に設けられた第1検査用電極(11)と、第1検査用電極(11)に短絡された第2検査用電極(12)とを備える。基板(3)は、回路接続用電極(4)に対応する位置に配置される回路接続用基板側電極(5)と、第1検査用電極(11)に対応する位置に配置される第1検査用基板側電極(21)と、第2検査用電極(12)に対応する位置に配置される第2検査用基板側電極(22)とを備える。第2検査用電極(12)は、半導体チップ(2)と基板(3)とが正常に接続されるとき、第2検査用基板側電極(22)と電気的に絶縁する位置に配置される。

(もっと読む)

検査プローブ接触検知機構および回路基板検査装置

【課題】検査プローブを被測定パターンに確実に接触させて正確に検査できる検査プローブ接触検知機構および回路基板検査装置の提供。

【解決手段】検査プローブ接触検知機構11は、検査プローブ12を保持するプローブ移動手段22と、プローブ移動手段22の導電部29を介して相互の電気的な導通を自在に離間配置された一対の電極部38,39と、該電極部38,39に接続されて電流を検出する計測回路とを備え、電極部38,39相互間に流される電流は、検査プローブ12を被測定パターンに接触させた際に受ける接触圧によるその流れの遮断により検査プローブ12の前被測定パターンへの接触の検知を可能に形成した。回路基板装置は、中央処理手段と、検査プローブ接触検知機構11が検出した電気的信号に基づいてプロービング動作を制御するプロービング制御手段とで構成した。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において、入力端子のオープン異常を、素子の追加量を抑えつつ且つ入力特性に影響を与えずに、検出可能にする。

【解決手段】マイコン21は、センサ信号を入力するための入力端子23が、プリント基板11の信号配線16に接続される。また、マイコン21において、電源電圧(5V)のラインとグランドラインとの各々と、入力端子23との間には、寄生ダイオードD1,D2がサージ電圧保護用のクランプダイオードとして機能するトランジスタ(MOSFET)T1,T2が接続されている。そして、マイコン21は、例えばトランジスタT2の方をハーフオン状態に駆動する駆動回路29を有しており、トランジスタT2をオフさせているときの入力端子23の電圧と、トランジスタT2をハーフオン状態に駆動したときの入力端子23の電圧とに基づいて、入力端子23が信号配線16と非接続になった異常(オープン異常)の有無を判定する。

(もっと読む)

情報処理装置及びその作動方法

【課題】モジュールと本体側コネクタ間の接続不良に起因してモジュールが動作不良と判断されてしまうおそれがある。

【解決手段】サーバー100は、複数の接点を介してメモリ装置10が接続され、複数の接点を介してメモリ装置10から複数ビットのデータが入力するコネクタ20と、コネクタ20を介して入力する複数ビットのデータに含まれるビットにエラーが生じているか否かを判断するビットエラー検出部41と、ビットエラー検出部41によりエラーが検出されたビットに対応する接点を含む第1配線と、ビットエラー検出部41によりエラーが検出されなかったビットに対応する接点を含む第2配線と、に対してテスト波形を入力し、このテスト波形に応じて第1及び第2配線夫々にて生じる反射波のレベル差を評価することで第1配線の状態を判定する接続確認回路50と、を備える。

(もっと読む)

試験装置及び試験方法

【課題】光インターフェースを備える被試験デバイスを試験する。

【解決手段】被試験デバイスを試験する試験装置であって、被試験デバイスを試験する試験信号を発生する試験信号発生部と、試験信号を光試験信号に変換する電光変換部と、電光変換部が変換した光試験信号を被試験デバイスの光入力部に伝送すると共に、被試験デバイスが出力する光応答信号を受け取って出力する光インターフェース部と、光インターフェース部が出力する光応答信号を電気信号の応答信号に変換して送信する光電変換部と、光電変換部が送信する応答信号を受信する信号受信部と、を備える試験装置および試験方法を提供する。

(もっと読む)

1 - 20 / 109

[ Back to top ]