Fターム[2G132AL13]の内容

Fターム[2G132AL13]の下位に属するFターム

初期設定(校正、較正は除く) (8)

校正、較正 (57)

タイミングの調整(スキュー等) (140)

Fターム[2G132AL13]に分類される特許

1 - 20 / 83

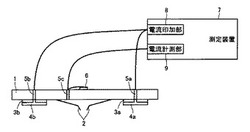

半導体検査装置

【課題】プローブカードの熱変形の影響によるプローブのコンタクト位置ずれなどを防止した半導体検査装置を提供すること。

【解決手段】プローブカード1に、発熱体4aおよび4bと、発熱体4aおよび4bによって高温にされたプローブカード1表面の温度を計測する温度センサ6とが設けられる。測定装置7は、発熱体4aおよび4bに電流を印加する電流印加部8と、温度センサ6の電流値を計測することによって、プローブカード1表面の温度を計測する電流計測部9とを含み、電流計測部9によって計測された電流値に応じて、電流印加部8を制御することによりプローブカード1表面の温度を制御する。したがって、プローブカード1の表面温度を一定値に保つことができ、プローブカード1の熱変形の影響によるプローブ2のコンタクト位置ずれなどを防止することが可能となる。

(もっと読む)

半導体集積回路及びその制御方法

【課題】精度の高いディレイテストを行うことが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路1は、クロック信号CLKに同期して動作する複数のレジスタを有する内部回路11と、クロック信号CLKに同期して動作し第1ノードから第2ノードまでの信号伝搬時間を測定する遅延測定回路12と、遅延測定モードの場合に、遅延測定回路12に対してのみクロック信号CLKを供給し、電圧検出モードの場合に、内部回路11及び遅延測定回路12に対してクロック信号CLKを供給するクロック供給回路13と、を備える。

(もっと読む)

試験装置用の電源装置およびそれを用いた試験装置

【課題】負荷や寄生インピーダンスに応じた最適な制御が可能な電源装置を提供する。

【解決手段】第1A/Dコンバータ22は、DUT1の電源端子P1に供給される電源信号S2に応じたアナログ観測値S2’をデジタル観測値S3に変換する。デジタル信号処理回路24は、デジタル観測値S3が所定の基準値Refと一致するように調節される制御値S4をデジタル演算処理によって生成する。第1D/Aコンバータ26は、制御値S4をデジタル/アナログ変換して得られるアナログの電源信号S1を、電源ライン4を介してDUT1の電源端子P1に供給する。負荷推定部40は、電源端子P1が接続されるべきノードN1に、電源ライン4を介して所定の周波数成分を含む試験信号S7を印加し、試験信号S7および観測信号S2’に応じて、デジタル信号処理回路24の制御パラメータS8を生成する。

(もっと読む)

半導体試験装置

【課題】複数のドライバのタイミングを校正するときに、高い精度のタイミング校正を行うことを目的とする。

【解決手段】本発明の半導体試験装置は、DUT1に信号を出力するドライバ10およびドライバ10に接続されるコンパレータ11とドライバ10のタイミングを校正するために設けた基準コンパレータ6との間の校正経路Lに信号を反射する複数の半導体スイッチ15が設けられる半導体試験装置2であって、コンパレータ11がドライバ10から出力されて基準コンパレータ6で反射した校正信号を検出するときに、半導体スイッチ15で多重反射した反射信号が校正信号の検出に干渉しないように、校正経路Lを基準コンパレータ6が分割した各分割経路L1〜L3の電気長Tpd1〜Tpd3を設定している。

(もっと読む)

半導体試験装置および半導体試験装置のタイミング校正方法

【課題】複数のドライバのタイミングを校正するときに、高い精度のタイミング校正を行うことを目的とする。

【解決手段】本発明の半導体試験装置は、DUT1に信号を出力する複数のドライバ10を備える半導体試験装置2であって、ドライバ10のタイミングを校正するための基準コンパレータ6にドライバ10からの信号を入力したときの波形が変化する間の第1の時間T1とドライバ10の出力端での信号の波形が変化する間の第2の時間T2とに基づいてドライバ10のタイミングを校正する校正値を補正する補正部25を備えている。これにより、伝送損失による波形なまりの影響を除去でき、校正値を補正して、ドライバのタイミング校正を高い精度で行うことができる。

(もっと読む)

半導体検査装置、及び荷電粒子線の画像、或いは光学条件の選択装置

【課題】本発明は、光学条件の調整を容易に行うことを目的とする半導体検査装置等の提供を目的とする。

【解決手段】上記目的を達成するために、荷電粒子線装置を備えた半導体検査装置、或いは荷電粒子線装置の画像,光学条件選択装置であって、異なる複数の光学条件にて得られた画像データと、設計データに基づいて形成される画像データとの間でマッチングを行い、当該マッチングに基づいて、前記光学条件、或いは画像の選択を行う半導体検査装置、或いは荷電粒子線装置の画像,光学条件選択装置を提案する。

(もっと読む)

ドライバ回路およびそれを用いた試験装置

【課題】ポジティブエッジの波形、ネガティブエッジの波形の少なくとも一方を調節可能なドライバ回路を提供する。

【解決手段】分岐回路10は、送信すべき入力信号SINを複数の経路12に分岐する。各タイミング調節回路20は、それぞれが対応する経路に分岐された送信すべき信号Saのポジティブエッジおよびネガティブエッジの少なくとも一方に遅延を与える。合成出力回路30は、複数のタイミング調節回路20の出力信号Sbを合成し、合成された信号SOUTを伝送線路3に出力する。

(もっと読む)

試験装置

【課題】安定した電源電圧を供給する。

【解決手段】メイン電源10は、DUT1の電源端子P1に電力を供給する。電源補償回路20は、メイン電源10からDUT1に流れる電源電流IDDから、補償電流ICMP’をDUT1とは別経路に引きこむ。補償電流ICMP’は、それとDUT1の電源端子P1に流れ込む動作電流IOPとの和が実質的に一定となるように生成される。電源補償回路20は、試験状態においてDUT1と熱的に結合されるように配置される。

(もっと読む)

試験装置および試験方法

【課題】電源電圧変動を補償可能な試験装置を提供する。

【解決手段】電源補償回路12は、スイッチ素子12b、12cがオンした状態において補償パルス電流ISRC、ISINKを生成する。パターン発生器ALPGは、ドライバDR1〜DR4が出力すべき試験信号STESTを記述するテストパターンSPTN1〜SPTN4を生成する。特徴点検出部6は、パターン発生器ALPGが発生するテストパターンSPTN1〜SPTN4を参照し、電源端子P1の電源電圧VDDに変動を発生させるイベントを検出する。そしてスイッチ素子(12b、12c)に割り当てられたドライバ(DR6、DR5)が出力すべき制御信号SCNTを記述する制御パターンSPTN_CMPを出力する。制御パターンSPTN_CMPは、各イベントに応じてあらかじめ定められている。

(もっと読む)

半導体試験装置

【課題】配線や伝送線路のインピーダンスを調整することなく、高品質な信号を被試験デバイスに入力させることを目的とする。

【解決手段】本発明は、複数のDUT7を搭載したDUTボード4とDUT7に試験信号を出力するテストピン4とDUTボード4とテストピン2との間を接続する伝送線路3とを備える半導体試験装置1であって、DUTボード4は、DUT7に試験信号を分配するための分岐配線9が分岐する分岐点10と伝送線路3との間に設けられ、分岐配線9の合成インピーダンスとテストピン2に設けられる出力抵抗11との間のインピーダンス不整合を補正するために設けた補正抵抗11を備えていることを特徴としている。

(もっと読む)

半導体試験装置

【課題】ユーザの使い勝手を向上することが可能な半導体試験装置を実現する。

【解決手段】異なる速度の低速レート信号と高速レート信号を用いて被試験対象デバイスの試験を行う半導体試験装置において、高速レート信号のレート長が設定されるレート長設定レジスタと、パターンプログラムに設定されている高速レート番号の組み合わせを抽出し、この組み合わせの中の1つの高速レート番号を調整レート番号に置き換え、低速レート信号のレート長の時間分解能に基づいて調整レート番号のレート長を算出して調整レート番号のレート長設定レジスタに設定する演算制御部とを備える。

(もっと読む)

被測定デバイス搭載ボード、及びデバイスインタフェース部

【課題】複数種類のパフォーマンスボードと接続できる接続ユニットを提供する。

【解決手段】ICソケットが載置されたパフォーマンスボードと、ICソケットに保持される電子デバイスを試験する試験装置とを電気的に接続する接続ユニットであって、パフォーマンスボードと対向して設けられる保持基板と、保持基板上における位置が変更可能に保持基板上に設けられ、パフォーマンスボードが備えるパフォーマンスボード側コネクタと接続されるべき接続ユニット側コネクタとを備えることを特徴とする接続ユニットを提供する。

(もっと読む)

テスト装置、テスト方法、及びテストプログラム

【課題】正確に合否判定を行う。

【解決手段】被測定装置が装着された装着テストボードを介して前記被測定装置に電流を印加し、前記被測定装置の所定部位の電圧を測定する測定部と、前記測定部による測定結果を取得し、規格値と比較することにより、前記被測定装置の合否を判定する判定部と、を具備する。前記判定部は、前記装着テストボードに対して固有である固有抵抗値を取得し、前記固有抵抗値に基づいて、合否を判定する。

(もっと読む)

検査装置の操作方法及び検査装置の操作プログラム

【課題】複数のステージを有する検査装置の検査効率を格段に高めることができる検査装置の操作方法を提供する。

【解決手段】本発明の検査装置の操作方法は、複数のモニター14それぞれの操作画面に表示される操作ボタンを用いて複数の検査用のステージ17を備えた検査装置10において、検査装置10の各種の機能を実行するために必要なデータをまとめた排他条件データDと、排他条件データDの排他条件を、各機能を実行するための操作ボタンを押下できるか否かのデータとしてまとめた排他条件パターンPと、を用いて、操作ボタンを排除するための排他条件ボタンを少なくとも一つのモニター14に設定し、排他条件ボタンを押下して他のモニターでは少なくとも一つのモニターの排他条件に即した画面の表示を禁止する。

(もっと読む)

LSIテスタ

【課題】新旧のシステムソフトウェアバージョンを切り替えて測定が行えるLSIテスタを提供する。

【解決手段】新旧バージョンのシステムソフトウェアを格納するシステムソフトウェア格納部33と、これらシステムソフトウェアのバージョン別の校正データを格納する校正データ格納部34と、DUTの機種に対応したテストプログラムを格納するテストプログラム格納部44と、これらテストプログラムとシステムバージョンとを対応付けたデータセット・システムバージョン対応テーブル35と、前記テストプログラム格納部から所望のテストプログラムを選択し、前記データセット・システムバージョン対応テーブルからこの選択されたテストプログラムに応じたシステムバージョンを選択し、前記バージョン別校正データ格納部から所定の校正データを読み出してテストシステムを駆動するインタフェース、とで構成されたことを特徴とするLSIテスタ。

(もっと読む)

半導体試験装置および半導体試験方法

【課題】基準クロックの周波数よりも低い周波数で動作する素子を用いて信号特性の変化を検出することを目的とする。

【解決手段】DUTから出力された試験信号の良否判定のテストを行う半導体試験装置であって、基準クロックを分周した周波数で動作し、試験信号を入力して遅延量の異なる負の遅延を与えて検査信号として出力する複数の負側遅延素子6−1〜6−4および負側フリップフロップ7−1〜7−4と、基準クロックを分周した周波数で動作し、試験信号を入力して遅延量の異なる正の遅延を与えて検査信号として出力する複数の正側遅延素子6−5〜6−8および正側フリップフロップ7−5〜7−8と、各検査信号が試験信号を基準としてそれぞれ信号変化点を含むように遅延量を設定する遅延量設定部16と、検査信号の値に基づいて試験信号の信号特性の検査を行う信号特性検査部14と、を備えている。

(もっと読む)

電気チャネル自己検査式半導体試験システム

【課題】電気チャネル自己検査式半導体試験システムの提供。

【解決手段】本電気チャネル自己検査式半導体試験システムは、試験ヘッド、複数のパラメータ検出ユニット、自己検査コントローラを包含し、該試験ヘッド内に複数の試験回路板が挿入され、それは複数の電源チャネル、複数の伝送チャネル、及び複数の駆動チャネルを具備する。自己検査コントローラが異なる検査信号を各電源チャネル、伝送チャネル、及び駆動チャネルにそれぞれ入力し、さらに複数のパラメータ検出ユニットにより各電源チャネル、伝送チャネル、及び駆動チャネルが上述の検査信号を受けて発生する応答信号を検出し並びに判断する。これにより本発明はウエハ試験の前に、各電気チャネルのオープンループ或いは短絡状態が正常であるか、或いは漏電が発生しているか否かを自己検査できる。

(もっと読む)

プローブカードのメンテナンス方法

【課題】半導体集積回路の電気的特性検査用の治具に用いられるプローブカードを正確、迅速、且つ容易にメンテナンスすることができるプローブカードのメンテナンス方法を提供する。

【解決手段】プローブカード及びプローブカードに設置されたプローブを電気的特性検査における検査温度と同一の温度まで加熱し、プローブカード及び複数のプローブを当該検査温度に維持しつつ、複数のプローブのそれぞれの位置調整を行う。

(もっと読む)

定電流回路、及び試験装置

【課題】帰還回路を用いて負荷回路に供給する電流を制御して、負荷変動による誤差を生じない定電流回路並びにその定電流回路を備えた試験装置を提供する。

【解決手段】変換回路Roは、負荷回路90の入力端に接続される。演算増幅器12は、出力端には変換回路Roを介して負荷回路90が接続され、変換回路Roから出力される信号と、演算増幅器12の出力端から出力される出力信号とを帰還信号とする。補償抵抗Rcは、演算増幅器12の一方の入力端と基準電位VGに接続され、帰還信号により生じる誤差を補償する。

(もっと読む)

半導体試験装置

【課題】試験信号を印加する度にクロック遅延が異なるDUTを試験する場合であっても、試験精度の低下を招くことなく高い精度で試験を行うことができる半導体試験装置を提供する。

【解決手段】半導体試験装置1は、可変遅延素子17a〜17cから出力されるストローブ信号ST1〜ST3のタイミングでDUT30から出力される信号S0をサンプリングしてデータD1〜D3を得るフリップフロップ12a〜12cと、データD1,D2と期待値パターンE1とを比較する比較部13と、比較部13の比較結果に基づいて可変遅延素子17a〜17cで生成されるストローブ信号ST1〜ST3のタイミングを調整する調整部(演算制御部14、DAC15、PLL回路16)とを備える。

(もっと読む)

1 - 20 / 83

[ Back to top ]