Fターム[4G077DB09]の内容

結晶、結晶のための後処理 (61,211) | 気相成長−CVD (2,039) | 基板上に気相成長させるもの (1,635) | 反応原料の選択 (1,331) | 有機化合物 (666) | 有機珪素化合物 (55)

Fターム[4G077DB09]に分類される特許

1 - 20 / 55

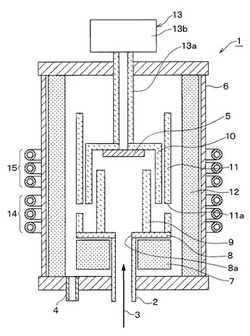

炭化珪素単結晶製造装置

【課題】原料ガスのガス流の安定化を図り、長時間安定してSiC単結晶を成長させることを可能とする。

【解決手段】台座10とヒータ11とを別体にすると共に、排気ガス出口11aが台座10よりも下方位置に配置されるようにすることで台座10によって覆われないようにし、台座10が引上げられても面積の変動が無いようにする。このような構成とすることで、SiC単結晶の成長中に原料ガス3のガス流が変化しないようにできる。これにより、原料ガス3のガス流の安定化を図ることが可能となり、長時間安定してSiC単結晶を成長させることが可能となる。

(もっと読む)

単結晶炭化シリコン膜の製造方法及び単結晶炭化シリコン膜付き基板の製造方法

【課題】結晶欠陥の少ない高品質なエピタキシャル膜を得ることが可能な単結晶炭化シリコン膜の製造方法及び単結晶炭化シリコン膜付き基板の製造方法を提供する。

【解決手段】シリコン基板11上に単結晶炭化シリコン膜14を形成する単結晶炭化シリコン膜14の製造方法であって、シリコン基板11の表面に炭化シリコン膜12を形成する第1の工程と、炭化シリコン膜12の表面にマスク材13を形成する第2の工程と、マスク材13に開口部13hを形成し、炭化シリコン膜12の一部を露出させる第3の工程と、原料ガスを含むガス雰囲気中でシリコン基板11を加熱し、炭化シリコン膜12を基点として単結晶炭化シリコンをエピタキシャル成長させ、炭化シリコン膜12及びマスク材13を覆う単結晶炭化シリコン膜14を形成する第4の工程と、を含み、原料ガスを含むガス雰囲気の圧力は、5.0×10−4Pa以上かつ0.5Pa以下である。

(もっと読む)

ウェーハ、エピタキシャルAlxGayInzN結晶構造体、エピタキシャルAlx’Gay’Inz’N結晶ブール、光電子デバイスおよびマイクロ電子デバイス

【課題】優れた表面品質をGa側にて有するAlxGayInzN半導体ウェーハおよびそのようなウェーハの製造方法を実現する。

【解決手段】ウェーハのGa側における10×10μm2面積内で1nm未満の根二乗平均表面粗さを特徴とする、AlxGayInzN(式中、0<y≦1およびx+y+z=1)を含む高品質ウェーハ。このようなウェーハは、例えばシリカまたはアルミナなどの研磨粒子と酸または塩基とを含む化学的機械研磨(CMP)スラリーを用いて、そのGa側にてCMPに付される。このような高品質AlxGayInzNウェーハの製造方法はラッピング工程、機械研磨工程、およびその表面品質を更に高めるための熱アニールまたは化学エッチングによるウェーハの内部応力を低下させる工程を含んでよい。このCMP方法はAlxGayInzNウェーハのGa側における結晶欠陥を強調するために有用に適用される。

(もっと読む)

半導体薄膜の製造方法及び製造装置

【課題】欠陥等が無く均質化され同じ内部応力の半導体薄膜を、基板の両面に同時に結晶成長させることができ、しかも、製造工程が簡単で、歩留まりも高い半導体薄膜の製造方法及び製造装置を提供する。

【解決手段】本発明の半導体薄膜の製造方法は、基板3の表面3aに第1の半導体薄膜を、この基板3の裏面3bに第2の半導体薄膜を、同時に形成する半導体薄膜の製造方法であり、基板3の表面3aを赤外線ランプ15で加熱するとともに、この表面3aに第1の原料ガスg1を導入し、この表面3aに第1の半導体薄膜を成長させ、同時に、この基板3の裏面3bに第2の原料ガスg2を導入し、この裏面3bに第2の半導体薄膜を成長させる。

(もっと読む)

立方晶炭化珪素膜の製造方法

【課題】横方向結晶成長における横方向成長速度が縦方向成長速度と同等の成長速度を維持することにより、等方的に立方晶炭化珪素を成長させることができ、より広い低欠陥領域を有する立方晶炭化珪素膜を形成させることのできる立方晶炭化珪素膜の製造方法を提供する。

【解決手段】シリコン基板2の表面2aに立方晶炭化珪素層11を形成する工程と、立方晶炭化珪素層11を選択除去し、結晶成長領域の結晶方位面が{100}面となる所望のパターンの立方晶炭化珪素シード層11aを形成する工程と、この立方晶炭化珪素シード層11a上に立方晶炭化珪素を成長させる工程と、を有する。

(もっと読む)

立方晶炭化珪素半導体基板の製造方法

【課題】結晶欠陥の少ない高品質な3C−SiC層を形成することが可能な立方晶炭化珪素半導体基板の製造方法を提供する。

【解決手段】シリコン基板11の上面11aに炭化層12を形成する第1の工程と、シリコン基板11の温度を第2の温度範囲の温度まで下降させる第2の工程と、シリコン基板11の温度が第2の温度範囲の温度となったところで、シリコン原料ガスを導入し、シリコン基板11と炭化層12の間の界面に形成された空孔11hにシリコンをエピタキシャル成長させて空孔11hを埋める第3の工程と、シリコン原料ガスの導入を止め、炭素原料ガスを導入しつつシリコン基板11の温度を第3の温度範囲の温度まで上昇させる第4の工程と、シリコン基板11の温度が第3の温度範囲の温度となったところで、シリコン原料ガス及び炭素原料ガスを導入し、炭化層12上に立方晶炭化珪素をエピタキシャル成長させる第5の工程と、を有する。

(もっと読む)

炭化珪素単結晶エピタキシャルウエハの製造方法

【課題】加工変質層の除去処理にかかる時間を減少させつつも、加工変質層に由来するエピタキシャル膜の欠陥の発生を抑制できる炭化珪素単結晶エピタキシャルウエハの製造方法を提供する。

【解決手段】炭化珪素単結晶エピタキシャルウエハの製造において、炭化珪素単結晶基板100を1600℃以上に加熱し、C/Si比が1.0以下となるように、原料ガスを供給し、エピタキシャル膜の成長速度を2.0μm/h以下にする。このとき、キャリアガスの流量を50slm以上にし、原料ガスとしてモノシランの流量を20sccm以下にし、成長装置の前記炭化珪素単結晶基板100が配置された空間の圧力を100mbar以上にすることにより、エピタキシャル膜の成長速度を2.0μm/h以下にすることができる。

(もっと読む)

エピタキシャルウェーハの製造方法、エピタキシャルウェーハ

【課題】エピタキシャル層の形成時のオートドープを確実に抑制することで、エピタキシャルウェーハの抵抗率均一性を向上させ、周縁部まで効率的にデバイスの形成が可能なエピタキシャルウェーハの製造方法およびエピタキシャルウェーハを提供する。

【解決手段】一面10a側に第一のエピタキシャル層11を形成したシリコン単結晶基板10は、次に、堆積物除去工程を行う。この堆積物除去工程では、シリコン単結晶基板10の面取り部10cを、例えば鏡面研磨することによって、第一の成長工程S1で生じた堆積物Pを除去する。

(もっと読む)

シリコン膜の製造方法

【課題】 高品質なシリコン膜を高速で結晶成長させる技術を提供する。

【解決手段】 1200℃〜1400℃に加熱されているとともに1500rpm〜3500rpmで回転している基板6に向けて、基板の表面に直交する方向から、塩化シランガス18を供給する。このときの塩化シランガス18の供給量を、基板6の表面1cm2当たり200μmol/分以上とする。

(もっと読む)

シリコンエピタキシャルウエーハ製造システム及びシリコンエピタキシャルウエーハの製造方法

【課題】一定量のシリコン原料ガスをシリコンエピタキシャル成長装置の反応室に供給できるシリコンエピタキシャルウエーハ製造システム及びシリコンエピタキシャルウエーハの製造方法を提供する。

【解決手段】原料混合ガス集中供給装置1で生成した原料混合ガス中のシリコン原料ガスの濃度値を常時測定する複数の濃度値測定装置18a,18bと、前記濃度値、又は前記濃度値から計算された補正値を各シリコンエピタキシャル成長装置11,12,13にデジタル信号で伝達する伝達手段17と、前記濃度値若しくは前記補正値に基づいて、各シリコンエピタキシャル成長装置11,12,13内の反応室11c,12c,13cに供給する前記原料混合ガスの量を随時補正する流量制御装置14,15,16と、を具備するシリコンエピタキシャルウエーハ製造システム10とする。

(もっと読む)

半導体発光素子の製造方法、半導体発光素子及びサファイア単結晶基板

【課題】直径100mm以上の大口径であっても結晶欠陥部分が少なく、化合物半導体層のエピタキシャル形成に適した高品質かつ低コストのサファイア単結晶基板、および、かかる基板上に化合物半導体層を成膜した高品質の半導体発光素子を安定的に提供する。

【解決手段】III族化合物半導体層を有する半導体発光素子の製造方法であって、サファイア単結晶のインゴットからウエーハを切り出す基板切り出し工程S200と、切り出したウエーハについてラング法によるX線トポグラフィ測定を行い、(11−20)面のX線回折像が得られるX線の入射角度ωに対し、±0.15°の範囲内を判断基準とする湾曲補正値Δωにより補正したX線によりX線回折像が得られる結晶欠陥部分を含むウエーハを選別する選別工程S500と、選別されたウエーハの被成膜面上にIII族化合物半導体層を成膜する半導体層成膜工程S800と、を有する。

(もっと読む)

炭化珪素単結晶基板および炭化珪素単結晶エピタキシャルウェハ

【課題】デバイス特性の劣化や、歩留まりの低下を抑制するため、貫通転位の転位線の方向を規定する。

【解決手段】貫通転位3の転位線の方向が揃えられ、貫通転位3の転位線の方向と[0001]c軸とが平行となるようにする。[0001]c軸方向に転位線を持つ貫通転位3は、基底面転位の転位線の方向と垂直であるため、C面内の拡張転位とはならず、積層欠陥を発生させることがない。このため、貫通転位3の転位線の方向が[0001]c軸であるSiC単結晶基板に対して電子デバイスを形成すれば、デバイス特性は良好となり、劣化が無く、歩留まりも向上したSiC半導体装置とすることができる。

(もっと読む)

単結晶3C−SiC基板の製造方法およびそれによって得られた単結晶3C−SiC基板

【課題】エピタキシャル成長過程において発生する表面欠陥を大幅に減少させることができ、後工程を簡略化しながら半導体デバイスとしての品質を確保できる単結晶3C−SiC基板の製造方法を提供する。

【解決手段】ベース基板上にエピタキシャル成長によって単結晶3C−SiC層を形成させる単結晶3C−SiC基板の製造方法であって、

上記単結晶3C−SiC層を、平坦性の高い表面とその中に点在する表面ピットからなる表面状態となるよう形成する第1の成長段階と、

上記第1の成長段階で得られた単結晶3C−SiC層を、脱離律速の領域において表面の上記表面ピットを埋めるようさらにエピタキシャル成長させる第2の成長段階とを行う。

(もっと読む)

炭化珪素エピタキシャル膜の製造方法

【課題】高品質のエピタキシャル膜を製造することができる、新たな炭化珪素エピタキシャル膜の製造方法を提供する。

【解決手段】化学気相堆積法によって、炭化珪素単結晶基板上に炭化珪素エピタキシャル膜を成膜する炭化珪素エピタキシャル膜の製造方法であって、圧力条件又は基板温度条件のうち、いずれか一方の条件を固定したまま、成膜途中で、他方の条件を、高い設定条件と低い設定条件との間で切り替えることを特徴とする炭化珪素エピタキシャル膜の製造方法である。

(もっと読む)

エピタキシャル炭化珪素単結晶基板の製造方法

【課題】炭化珪素単結晶基板に含まれる基底面転位がエピタキシャル膜に引き継がれるのを抑制して、高品質のエピタキシャル膜を成膜することができるエピタキシャル炭化珪素単結晶基板の製造方法を提供し、また、これにより得られたエピタキシャル炭化珪素単結晶基板を提供する。

【解決手段】化学気相堆積法によって、炭化珪素単結晶基板上に炭化珪素膜をエピタキシャル成長させる結晶成長工程において、エピタキシャル成長の主たる時間を占める結晶成長主工程での成長温度T1に対し、低い設定温度T0と高い設定温度T2との間で、成長温度を上下に変化させる温度切り替え操作を伴う結晶成長副工程を含むエピタキシャル炭化珪素単結晶基板の製造方法であり、また、この方法を用いて得られたエピタキシャル炭化珪素単結晶基板である。

(もっと読む)

炭化珪素単結晶の製造装置および製造方法

【課題】エッチングガスを使用しなくても、種結晶が設置される台座周囲にSiC多結晶が堆積することを抑制できるSiC単結晶の製造装置および製造方法を提供する。

【解決手段】台座10の円板部10aの背面に温度調整パイプ11aを備え、温度調整パイプ11aによって台座10の円板部を冷却する。これにより、種結晶5の表面の温度を所望温度に維持しつつ、台座10の周囲の温度をそれよりも高温にすることができる。つまり、台座10の円板部10aを背面側から冷却することにより、相対的に台座10の周囲の温度を台座10の中央部よりも高温にできるので、エッチングガスを使用しなくても、種結晶5が設置される台座10の周囲にSiC多結晶が堆積することを抑制できる。

(もっと読む)

成膜装置および成膜方法

【課題】基板を加熱して膜形成を行う際に反応ガスを効率良く使用でき、膜厚均一性の高い高品質のSiC膜を実現できる成膜装置を提供する。

【解決手段】成膜装置100を、成膜室102と、成膜室102内に珪素のソースガスを含む第1の反応ガス131をSiCウェハ101上に供給する第1のガス供給路140と、炭素のソースガスを含む第2の反応ガス132を供給する第2のガス供給路141とを用いて構成し、第1のガス供給路140は先端が成膜室102内のSiCウェハ101の近傍まで延びており、第2のガス供給路141は成膜室102上部に設けられ、第1のガス供給路140から供給された第1の反応ガス131と第2のガス供給路141から供給された第2の反応ガス132とを用いてSiCウェハ101上でSiC(炭化珪素)膜の成膜を行うようにする。

(もっと読む)

半導体基板の製造方法

【課題】SiCを用いた半導体装置を効率よく製造するための半導体基板の製造方法を提供する。

【解決手段】第1の裏面B1を有する第1の炭化珪素基板11と、第2の裏面B2を有する第2の炭化珪素基板12とが準備される。第1および第2の裏面B1、B2の各々が一の方向に露出するように第1および第2の炭化珪素基板11、12が配置される。炭化珪素からなり、かつ第1および第2の裏面B1、B2を互いにつなぐ成長層30が化学気相成長法によって形成される。

(もっと読む)

エピタキシャルウェーハおよびその製造方法

【課題】ヘイズレベルが低く、平坦度(エッジロールオフ)に優れ、また、さらには、エピタキシャル成長速度の方位依存性が低減された、半導体デバイスの高集積化に対応できるシリコンエピタキシャルウェーハおよびその製造方法を提供する。

【解決手段】原料ガスとしてトリクロロシランとジクロロシランの混合ガスを使用し、1000〜1100℃、望ましくは1040〜1080℃の温度範囲内でシリコンウェーハの表面にシリコン層をエピタキシャル成長させ、得られるエピタキシャルウェーハのヘイズレベルを0.050〜0.080ppm(KLA−Tencor社製パーティクルカウンター(SP−1)によるDWNモードでの測定値)とし、エッジロールオフを低い範囲内に維持する。ジクロロシランの使用によるエピタキシャル成長速度の低下を一定範囲内にとどめ、エピタキシャルウェーハの生産効率を比較的良好に維持することができる。

(もっと読む)

III族窒化物半導体の製造方法およびテンプレート基板

【課題】結晶性、表面平坦性に優れた非極性面や半極性面を主面とするIII 族窒化物半導体を製造すること。

【解決手段】a面サファイア基板10の表面10aに、ICPエッチングで長手方向がサファイア基板10のm軸方向に平行なストライプ状に凹部11を形成する(図1(a))。次に、サファイア基板10をMOCVD装置に搬入し、水素とアンモニアを含む雰囲気中で、1020〜1060℃まで昇温する。続いて、凹部11の側面11aにGaN結晶13をエピタキシャル成長させる(図1(b))。成長が進むと、サファイア基板10の表面10aはGaN結晶13に覆われていき、平坦なGaN結晶13が形成される(図1(c))。このGaN結晶13の主面はm面である。

(もっと読む)

1 - 20 / 55

[ Back to top ]