Fターム[4M104EE11]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の構造、形態 (769)

Fターム[4M104EE11]の下位に属するFターム

多層絶縁膜を含むもの (712)

Fターム[4M104EE11]に分類される特許

1 - 20 / 57

半導体装置

【課題】短チャネル効果の抑制およびオフリーク電流の抑制が可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置は、半導体基板において素子分離領域によって仕切られた素子領域と、前記素子領域を横切る所定の方向に沿って前記素子領域の表層に設けられたゲートトレンチにより分離されて前記素子領域の表層に形成されたソース領域およびドレイン領域とを備える。また、実施形態の半導体装置は、少なくとも一部が前記ゲートトレンチ内にゲート絶縁膜を介して埋め込まれて前記ソース領域およびドレイン領域よりも深い位置まで形成されたゲート電極を備える。ドレイン領域における前記ゲート絶縁膜と接触する界面は、前記ゲート電極側に突出した凸部を有する。

(もっと読む)

薄膜トランジスタおよびその製造方法、電子機器

【課題】コンパクトでありながら、より安定した動作を行う薄膜トランジスタを提供する。

【解決手段】この薄膜トランジスタは、ゲート電極と、絶縁膜を介してゲート電極と対向して配置された有機半導体層と、この有機半導体層の上に設けられた絶縁性構造体と、互いに離間して配置され、かつ、有機半導体層の上面の一部とそれぞれ接するソース電極およびドレイン電極と、絶縁性構造体を覆い、ソース電極と接続されると共にドレイン電極と分離された導電性材料層とを有する。

(もっと読む)

半導体装置およびその製造方法

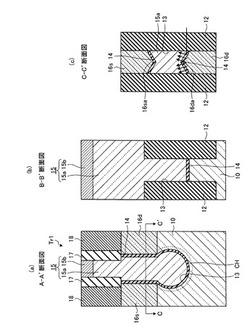

【課題】トレンチの対向する側面上に互いに離間されたゲート電極を有する半導体装置において、微細化に対応することができる半導体装置の製造方法を提供する。

【解決手段】トレンチ4を形成する工程およびゲート絶縁膜6を形成する工程では、トレンチ4のうち第2導電型層3と接する部分を中間部したとき、トレンチ4の対向する側面に形成されたゲート絶縁膜6の間隔において、トレンチ4の開口部に形成されている部分の間隔W1がトレンチ4の中間部に形成されている部分の間隔W2より狭くなるトレンチ4およびゲート絶縁膜6を形成する。そして、導電膜7aを形成する工程では、トレンチ4に導電膜7aで囲まれる空隙14を形成しつつ、導電膜7aを形成する。その後、ゲート電極7を形成する工程では、導電膜7aを異方性エッチングし、空隙14を介してトレンチ4の底面に形成された導電膜7aを除去してゲート電極7を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

化合物半導体装置

【課題】高耐圧特性と低オン抵抗特性とを両立した化合物半導体装置を実現する。

【解決手段】化合物半導体装置を、キャリア走行層2及びキャリア供給層3を含む窒化物半導体積層構造4と、窒化物半導体積層構造の上方に設けられたソース電極5及びドレイン電極6と、窒化物半導体積層構造の上方のソース電極とドレイン電極との間に設けられたゲート電極7と、ゲート電極とドレイン電極との間に少なくとも一部が設けられたフィールドプレート8と、窒化物半導体積層構造の上方に形成された複数の絶縁膜9、10とを備えるものとし、フィールドプレートとドレイン電極との間でゲート電極の近傍よりも複数の絶縁膜の界面の数を少なくする。

(もっと読む)

異種材料接合型ダイオード及びその製造方法

【課題】電流電圧特性を維持しつつ、アノード電極6の剥離に対する機械的強度を向上させる。

【解決手段】異種材料接合型ダイオードは、半導体基体1と、半導体基体1の上に形成された第1導電型のドリフト領域2と、ドリフト領域2の主表面に接合された、ドリフト領域2とは異なる種類の材料からなるアノード電極6と、半導体基体1に接続されたカソード電極7とを備える。ドリフト領域2とアノード電極6との接合によりダイオードが形成されている。アノード電極6の主表面のうち、ドリフト領域2に接している側の主表面に、嵌合構造(3、G1)が形成されている。

(もっと読む)

半導体装置およびその制御方法

【課題】リカバリ損失の低減が図れ、かつ、ノイズによるセルフターンオンが生じ難い構造の半導体装置を提供する。

【解決手段】ゲート電極8を深さの異なる第1、第2ゲート電極8a、8bを備えたダブルゲート構造とする。このような構造では、第1、第2ゲート電極8a、8bのうちの第1ゲート電極8aのみをオンさせることで、p型ベース領域3に対して反転層を形成しながらも、その反転層がn-型ドリフト層2とn+型不純物領域4とを繋ぐ深さまでは形成されないようにすることができる。この第1ゲート電極8aを過剰キャリア注入抑制ゲートとして機能させる。

(もっと読む)

電界効果型有機トランジスタ

【課題】ゲート絶縁層に含まれる高誘電体粒子がゲート電極側に偏在していない場合に比べ、低電圧でも駆動する電界効果型有機トランジスタを提供する。

【解決手段】基板と、ゲート電極と、ゲート絶縁層と、チャネル層と、ソース電極と、ドレイン電極と、を有し、前記チャネル層は有機半導体層であり、前記ゲート絶縁層は高誘電体粒子及び絶縁性樹脂を含み、前記高誘電体粒子がゲート電極側に偏在している電界効果型有機トランジスタ。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタのオン電流の安定を図る。

【解決手段】ELパネル1において、駆動素子として用いるスイッチトランジスタ5、駆動トランジスタ6などの薄膜トランジスタにおけるチャネル保護膜6d(5d)に鋭角なエッジ部6p(5p)を設けて、そのエッジ部6d(5d)でソース電極6i(5i)と不純物半導体膜6g(5g)の積層体を破断するようにして、その積層体がチャネル保護膜6d(5d)の上面に重ならない構造にすることで、チャネルとなる領域を覆うチャネル保護膜6d(5d)に作用するバックゲート効果を抑制することができ、チャネルの乱れを抑えることができるので、薄膜トランジスタ6(5)のオン電流(Id)を従来のものより増加させ、好適な値に安定させることを可能にした。

(もっと読む)

半導体装置

【課題】シリサイドプロセス前にイオン注入を行う半導体装置であって、より確実にMISFETにおけるリーク電流の抑制が図れるものを実現する。

【解決手段】マスク層RMによりPチャネル型MISFETを覆いつつ、Nチャネル型MISFETのN型ソース領域およびN型ドレイン領域に、イオン(F,Si,C,Ge,Ne,Ar,Krのうち少なくとも一種類を含む)を注入する。その後、Nチャネル型MISFETおよびPチャネル型MISFETの各ゲート電極、ソース領域およびドレイン領域にシリサイド化(Ni,Ti,Co,Pd,Pt,Erのうち少なくとも一種類を含む)を行う。これにより、Pチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流を劣化させること無く、Nチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流(基板リーク電流)の抑制が図れる。

(もっと読む)

半導体装置及びその製造方法

【課題】オフセット構成となる場合があった。

【解決手段】第1導電型のドレイン領域と、前記ドレイン領域上に形成された第2導電型のボディ領域と、前記ボディ領域を貫通し、底面部分が前記ドレイン領域に達するトレンチと、前記トレンチに埋設されたゲート電極と、前記ゲート電極と、前記トレンチの側面及び底面とを絶縁する絶縁部と、を有し、前記ボディ領域は、前記トレンチ側面に近づくにつれ前記トレンチの深さ方向に深くなり、前記絶縁部は、トレンチ壁面に形成されたゲート絶縁膜と、トレンチ底部に形成された底部埋込絶縁膜とを備え、前記底部埋込絶縁膜は、前記トレンチの深さ方向に深くなるにつれ、前記ゲート酸化膜よりも厚くなる厚い絶縁膜部分を有し、前記厚い絶縁膜部分は、前記ボディ領域の最低部より前記トレンチの深さ方向に対して所定の深さに位置されている半導体装置。

(もっと読む)

PMOSデバイスのゲートスタックのしきい値電圧を調整する方法

【課題】本発明は、半導体基板上にゲート誘電体層とゲート電極とのゲートスタックを含む半導体デバイスを製造する方法であって、ゲートスタックのVT値を容易に調整することができる方法を提供する。

【解決手段】ゲート誘電体層とゲート電極とのゲートスタックを含む半導体デバイスを製造する方法は、第1の電気陰性度を有する金属酸化物または半金属酸化物であるゲート誘電体層を半導体基板上に形成するステップと、第2の電気陰性度を有する金属酸化物または半金属酸化物である誘電体VT調整層を形成するステップと、ゲート誘電体層およびVT調整層の上にゲート電極を形成するステップと、を含み、前記ゲートスタックの実効仕事関数が、誘電体VT調整層の厚さおよび組成を調整することによって所望の値に調整され、第2の電気陰性度が、第1の電気陰性度およびAl2O3のいずれよりも高い。

(もっと読む)

窒化物半導体発光素子

【課題】光取り出し効率が高く、かつ発光効率が高い窒化物半導体発光素子を提供する。

【解決手段】本発明の窒化物半導体発光素子は、窒化物半導体層と、導電性の第1酸化物層と、絶縁性の第2酸化物層とを含み、第1酸化物層および第2酸化物層は、同一種類の酸化物材料からなることを特徴とする。第1酸化物層を構成する二酸化チタン中のチタンに対し、ニオブ、タンタル、モリブデン、ヒ素、アンチモン、アルミニウムまたはタングステンのいずれかがモル比で1%以上10%以下ドープされ、第2酸化物層を構成する二酸化チタン中のチタンに対し、ニオブ、タンタル、モリブデン、ヒ素、アンチモン、アルミニウムまたはタングステンのいずれかがモル比で1%未満ドープされることが好ましい。

(もっと読む)

表示装置および表示装置の製造方法

【課題】有機半導体層を用いた薄膜トランジスタと画素電極とを含む層間に発生する応力を緩和することが可能で、これによりトランジスタ特性の劣化を防止して、表示特性および信頼性の向上が図られた表示装置を提供する。

【解決手段】有機半導体層を用いた薄膜トランジスタが配列形成された基板と、薄膜トランジスタを覆う状態で基板上に設けられた層間絶縁膜と、層間絶縁膜上に設けられた画素電極とを備えたものである。特に、層間絶縁膜は、薄膜トランジスタよりも平面視的なサイズが小さい凹凸パターンからなる凹凸表面を有しており、この凹凸表面上に画素電極が設けられていることを特徴としている。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN/AlGaN−HEMTをE−mode動作させるに当たり、Vf及び最大ドレイン電流を向上させ、かつ良好なゲート−ドレイン間耐圧を有し、さらに、ゲートリーク電流を抑制する。

【解決手段】基板15と、この基板上に形成されており、GaN層17及びAlGaN層19が順次積層されてなる積層構造体21とを含む下地13と、AlGaN層に開口形成されているゲート形成用凹部27と、このゲート形成用凹部の内側底面27a、ゲート形成用凹部の内側壁面27b、及びゲート形成用凹部外の下地面13aを一体的に被覆して形成されているSiN膜29と、SiN膜の表面を被覆して形成されているアモルファスAlN膜31と、SiN膜及びアモルファスAlN膜が形成されているゲート形成用凹部を埋め込むゲート電極33とを具える。

(もっと読む)

積層構造体及びその製造方法

【課題】生産性が向上し、かつ、半導体膜の導電膜からのはみ出し量が低減できる積層構造体及びその製造方法を提供すること。

【解決手段】本発明にかかる積層構造体は、半導体膜15、ゲート絶縁膜12、ソース電極17、及びドレイン電極18を有するものである。ゲート絶縁膜12は、半導体膜15下において、半導体膜15の端から徐々に膜厚が薄くなるテーパー部を有する。ソース電極17及びドレイン電極18は、半導体膜15上において、半導体膜15のパターンからはみ出さないように形成され、半導体膜15端からの距離が0以上0.3um以下である。

(もっと読む)

半導体装置及びその作製方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極の上に設けられたゲート絶縁膜と、ゲート絶縁膜

の上に設けられソース領域及びドレイン領域を含む半導体膜と、ソース領域又はドレイン

領域に電気的に接続する配線又は電極と、配線又は電極の上に設けられ第1の開口部を有

する第1の絶縁膜と、第1の絶縁膜の上に設けられ第2の開口部を有する第2の絶縁膜と

、第2の絶縁膜の上に設けられた画素電極とを有し、第1の絶縁膜は窒化シリコン膜を含

む積層の無機絶縁膜からなり、第2の絶縁膜は有機樹脂膜からなり、第2の絶縁膜の第2

の開口部の底面において、第1の絶縁膜の上面は第2の絶縁膜に覆われていない露呈した

部分を有し、第2の絶縁膜の第2の開口部の断面において、第2の絶縁膜の内壁面は凸状

の曲面を有しており、画素電極は、第1の開口部及び第2の開口部を介して配線又は電極

に電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】低い閾値電圧を有するFETおよび高い閾値電圧を有するFETのいずれも高性能な特性を有する半導体装置を提供する。

【解決手段】半導体装置100は、FET102と、FET102よりも高い閾値電圧を持つFET104を同一半導体基板上に備える。FET102は、ゲート絶縁膜114とゲート電極126を備える。FET104は、ゲート絶縁膜114とゲート電極121を備える。FET102のゲート電極126、FET104のゲート絶縁膜114、ゲート電極121はHf、Zr、Al、La、Pr、Y、Ta、Wからなる群から選択される少なくとも一つの金属を含む。FET104のゲート絶縁膜114とゲート電極121との界面における前記金属の濃度は、FET102のゲート絶縁膜114とゲート電極126との界面における前記金属の濃度よりも高い。

(もっと読む)

ピンホールアンダーカット部を含む装置と工程

【課題】ピンホールの悪影響の軽減された新たな電子デバイスと新たな電子デバイス製造方法を提供する。

【解決手段】入口92Aと出口94Aのある複数のピンホール90Aを有する誘電領域14と、下側導電領域18とを備え、ピンホール90Aの少なくともいくつかは出口94A周辺において出口94Aより広い下側導電領域18のアンダーカット部96Aに面する誘電領域14の張り出し面98Aを持たせる

(もっと読む)

1 - 20 / 57

[ Back to top ]