Fターム[4M104EE12]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の構造、形態 (769) | 多層絶縁膜を含むもの (712)

Fターム[4M104EE12]に分類される特許

1 - 20 / 712

電界効果トランジスタ

半導体装置およびその製造方法

半導体装置およびその製造方法

電界効果トランジスタ

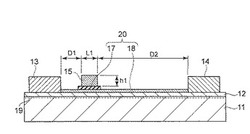

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター

【課題】強誘電体ゲート薄膜トランジスターの伝達特性が劣化し易い(例えばメモリウインドウの幅が狭くなり易い)という問題をはじめとして、PZT層から酸化物導電体層にPb原子が拡散することに起因して生ずることがある種々の問題が解決された強誘電体ゲート薄膜トランジスターを提供する。

【解決手段】強誘電体ゲート薄膜トランジスター20は、チャネル層28と、チャネル層28の導通状態を制御するゲート電極層22と、チャネル層28とゲート電極層22との間に配置された強誘電体層からなるゲート絶縁層25とを備え、ゲート絶縁層(強誘電体層)25は、PZT層23と、BLT層24(Pb拡散防止層)とが積層された構造を有し、チャネル層28(酸化物導電体層)は、ゲート絶縁層(強誘電体層)25におけるBLT層(Pb拡散防止層)24側の面に配置されている。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】酸化物をチャネル及びゲート絶縁層に適用した薄膜トランジスタの高性能化、又はそのような薄膜トランジスタの製造プロセスの簡素化と省エネルギー化を実現する。

【解決手段】本発明の1つの薄膜トランジスタ100は、ゲート電極220とチャネル40との間に、ゲート電極20に接する、ビスマス(Bi)とニオブ(Nb)とからなる第1酸化物(不可避不純物を含み得る)の層32と、チャネル40に接する、ランタン(La)とタンタル(Ta)とからなる酸化物、ランタン(La)とジルコニウム(Zr)とからなる酸化物、及びストロンチウム(Sr)とタンタル(Ta)とからなる酸化物の群から選択される1種の第2酸化物(不可避不純物を含み得る)の層34との積層酸化物30を備え、チャネル40が、インジウム(In)と亜鉛(Zn)とからなるチャネル用酸化物(不可避不純物を含み得る)である。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたトランジスタを有する信頼性の高い半導体装置を提供する。

【解決手段】ガラス基板上に設けられたボトムゲート構造のスタガ型トランジスタを有する半導体装置において、ゲート電極層上に組成を異なる第1のゲート絶縁膜及び第2のゲート絶縁膜が順に積層されたゲート絶縁膜を設ける。又は、ボトムゲート構造のスタガ型トランジスタにおいて、ガラス基板とゲート電極層との間に保護絶縁膜を設ける。第1のゲート絶縁膜と第2のゲート絶縁膜との界面、又はゲート電極層とゲート絶縁膜との界面における、ガラス基板中に含まれる金属元素の濃度を、5×1018atoms/cm3以下(好ましくは1×1018atoms/cm3以下)とする。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】ゲート絶縁膜の膜減り及びダメージを抑え、微細なトランジスタを歩留まり良く作製する。

【解決手段】絶縁表面上の半導体膜と、半導体膜上のゲート絶縁膜と、ゲート絶縁膜上の、第1の金属膜および第1の金属膜上の第2の金属膜を有するゲート電極と、ゲート絶縁膜上に形成され、かつ第1の金属膜の側面と接し、第1の金属膜と同一の金属元素を有する金属酸化物膜と、を有し、第2の金属膜より第1の金属膜のほうが、イオン化傾向が大きい半導体装置である。

(もっと読む)

半導体装置とその製造方法

【課題】特性ばらつきの少ない絶縁ゲートを備えた窒化物半導体の半導体装置を提供すること。

【解決手段】 半導体装置が備える絶縁ゲートは、窒化物半導体層1上に設けられているアモルファスの酸化シリコン膜2と、酸化シリコン膜2上に設けられているゲート電極8を有している。ゲート電極8に対向する窒化物半導体層1が酸化されている。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ別のマスクを用いた別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、ソース電極層またはドレイン電極層は、開口を埋め込むように絶縁層上に導電膜を形成し、絶縁層上の導電膜を化学的機械研磨処理によって除去することで形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

半導体装置

【課題】配線抵抗に伴う電圧降下や信号遅延によるトランジスタへの信号の書き込み不良

を防止した半導体装置を提供することを課題の一つとする。例えば、表示装置の画素に設

けたトランジスタへの書き込み不良が引き起こす階調不良などを防止し、表示品質の高い

表示装置を提供することを課題の一つとする。

【解決手段】配線抵抗が低い銅を含む配線に、バンドギャップが広く、且つキャリア濃度

が低い高純度化された酸化物半導体を接続してトランジスタを作製すればよい。バンドギ

ャップが広い酸化物半導体を用いて、トランジスタのオフ電流を低減するだけでなく、キ

ャリア濃度が低い高純度化された酸化物半導体を用いて正のしきい値電圧を有し、所謂ノ

ーマリーオフ特性のトランジスタとして、オフ電流とオン電流の比を大きくできる。

(もっと読む)

半導体装置の製造方法

【課題】特性の良好な半導体装置を製造する。

【解決手段】本発明は、MISFETを有する半導体装置の製造方法であって、(a)半導体基板の上方に、シリコン膜と絶縁膜CPとの積層膜を形成する工程と、(b)積層膜をパターニングすることによりゲート電極GE1とその上部に配置された絶縁膜CPとの積層体を形成する工程と、(c)積層体の側壁にサイドウォール膜SWを形成する工程と、(d)絶縁膜CPを除去する工程と、(e)サイドウォール膜SWおよびゲート電極GE1の合成体の両側の半導体基板中および前記ゲート電極GE1中にヒ素(As)を注入する工程と、を有する。かかる製法によれば、ヒ素(As)のイオン注入によるゲート電極GE1の体積膨張、特に、横方向への膨らみを低減することができ、ゲート電極とコンタクトプラグとの短絡を低減できる。

(もっと読む)

酸化アンチモン膜の原子層堆積

【課題】アンチモン反応物質および酸素ソースを使用して酸化アンチモン薄膜を原子層堆積によって堆積させるプロセスを提供する。

【解決手段】アンチモン反応物質は、ハロゲン化アンチモン、例えばSbCl3、アンチモンアルキルアミン、およびアンチモンアルコキシド、例えばSb(OEt)3を含んでもよい。酸素ソースは、例えばオゾンであってもよい。いくつかの実施形態では、この酸化アンチモン薄膜は、バッチ反応器の中で堆積される。この酸化アンチモン薄膜は、例えば、エッチング停止層または犠牲層としての役割を果たしてもよい。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を得る。

【解決手段】HEMTは、化合物半導体層2と、開口を有し、化合物半導体層2上を覆う保護膜と、開口を埋め込み、化合物半導体層2上に乗り上げる形状のゲート電極7とを有しており、保護膜は、酸素非含有の下層絶縁膜5と、酸素含有の上層絶縁膜6との積層構造を有しており、開口は、下層絶縁膜5に形成された第1の開口5aと、上層絶縁膜6に形成された第1の開口5aよりも幅広の第2の開口6aとが連通してなる。

(もっと読む)

化合物半導体装置の製造方法

【課題】化合物半導体積層構造上の絶縁膜に所期の微細な開口を形成するも、リーク電流を抑止した信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2上にパッシベーション膜6を形成し、パッシベーション膜6の電極形成予定位置をドライエッチングにより薄化し、パッシベーション膜6の薄化された部位6aをウェットエッチングにより貫通して開口6bを形成し、この開口6bを電極材料で埋め込むように、パッシベーション膜6上にゲート電極7を形成する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電極と化合物半導体層との界面に電極材料が到達することを抑止し、ゲート特性の劣化を防止した信頼性の高い高耐圧の化合物半導体装置を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成され、貫通口6aを有するパッシベーション膜6と、貫通口6aを埋め込むようにパッシベーション膜6上に形成されたゲート電極7とを有しており、ゲート電極7は、相異なる結晶配列の結晶粒界101が形成されており、結晶粒界101の起点が貫通口6aから離間したパッシベーション膜6の平坦面上に位置する。

(もっと読む)

半導体装置

【課題】頻繁なリフレッシュ動作が不要で、正常な読み出しを行うことのできる2トランジスタ型のDRAMを備えた半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、ゲートが第1配線に接続され、第1ソース/ドレインの一方が第2配線に接続された第1トランジスタと、ゲート絶縁膜、ゲート電極、および前記ゲート絶縁膜と前記ゲート電極との間に設けられしきい値を変調するしきい値変調膜を有するゲート構造と、第2ソース/ドレインとを備え、前記ゲート電極が前記第1トランジスタの前記第1ソース/ドレインの他方に接続され、前記第2ソース/ドレインの一方が第3配線に接続され、前記第2ソース/ドレインの他方が第4配線に接続された第2トランジスタと、を備えている。

(もっと読む)

1 - 20 / 712

[ Back to top ]