Fターム[4M104FF27]の内容

半導体の電極 (138,591) | 構造 (12,435) | コンタクト面の位置、配置 (799) | 基板の凹部 (569)

Fターム[4M104FF27]に分類される特許

561 - 569 / 569

半導体装置におけるセルフアラインドコンタクトを形成する製造方法

【課題】半導体装置におけるセルフアラインドコンタクトを形成する製造方法であって、基板のコアエリアとターミネーションエリアの一部分まで拡張してトレンチをエッチングで形成する方法を提供する。

【解決手段】第一の酸化物はトレンチの壁部に隣接した前記基板上に生成される。ポリシリコン層は前記コアエリアと前記ターミネーションエリアに蒸着される。このポリシリコン層は、前記コアエリアの前記トレンチの一部分にゲート領域を形成するように選択的にエッチングされる。このポリシリコン層のエッチングは、また、前記ゲートインターコネクト領域の第一部分を前記ターミネーションエリアの前記トレンチ部分に形成し、ゲートインターコネクト領域の第二部分を前記ターミネーションエリアにおける前記トレンチの外側に形成する。

(もっと読む)

半導体装置

【課題】 ブレークダウン電圧を低電圧化しても電極の基板領域への突き抜けによるリーク電流の発生がない半導体装置を提供する。

【解決手段】 ベース領域13の表面とカソード電極15とが層間絶縁膜14bを介して電気的非接触であり、ベース領域13より接合深さが深いガードリング領域12内に埋め込まれた導電体プラグ19によりガードリング領域12とカソード電極15との電気的接触が図られているため、アルミニウムによるアロイスパイク現象が発生する虞がなくなる。

(もっと読む)

インコンフォーマルな堆積を用いて半導体プロセス技術において基板を垂直にパターニングする方法

典型的には半導体ウェーハである基板(1)の、レリーフ状にパターニングされた基板表面(101)上に、堆積方法(ADL;atomic layer deposition:原子層堆積)を用いて、基板表面(101)に対して傾斜し、および/または垂直である処理表面(2)に、被覆層(3)が提供される。被覆層(3)は、前駆材料の少なくとも1つの処理量の制限によって、および/または堆積方法の時間的制限によって、簡易な方法において、基板表面(101)に対して垂直な方向にパターニングされ、後続のプロセス工程のための機能層あるいはマスクとして形成される。  (もっと読む)

(もっと読む)

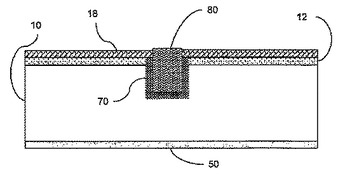

平面デュアルゲート半導体装置

デュアルゲート半導体装置の製造方法は、シリコン体(16)の第1の表面(14)の一部分上に第1のゲート(12)が形成された後であるが、前記第1の表面の反対側のシリコン体の第2の表面(44)上に第2のゲート(52)を形成する前に行われるソース及びドレインコンタクト領域(34,36)のシリサイド化を備える。第1のゲート(12)はソース及びドレインコンタクト領域がシリコンチャネル(18)に位置合わせされることを保証するマスクの働きをする。さらに、製造の早い段階でシリサイド化を行うことにより、第2のゲートの材料の選択が高温処理により制限されない。シリサイド化によるシリコン体の第2の表面での材料特性の違いがシリサイドのソースコンタクト領域とドレインコンタクト領域との間に前記第2のゲートを横方向に位置合わせされることを可能にすることが有利である。  (もっと読む)

(もっと読む)

セルフドーピングコンタクトを有した埋設コンタクト型太陽電池

埋設コンタクト型太陽電池、埋設コンタクト型太陽電池構成要素、及び埋設コンタクト型太陽電池太陽電池の製造方法であって、複数の埋設コンタクト面の溝内にセルフドーピングコンタクト材料が配置される。溝ドーピング処理とメッキ処理とを組み合わせることで、太陽電池をより単純な方法で経済的に製造できる。  (もっと読む)

(もっと読む)

トレンチデバイスのための自動整合された接点構造体

【課題】オン時の電流を下げることなく、セルの実装密度を高める。

【解決手段】 トレンチタイプのパワー半導体デバイスを製造する方法であって、開口部を有するマスク層を半導体の表面に形成するステップを含んでいる。マスクの開口部を通し、半導体本体内に、ゲートを有するトレンチを形成する。次に、ゲートの頂部であって、かつマスク層の開口部内に絶縁プラグを形成する。次に、マスク層を除去し、半導体表面の上方に延びる絶縁プラグを残す。次に、トレンチ間にソース打ち込み領域を形成する。その後、絶縁プラグの側面に沿って、スペーサーを形成し、トレンチに隣接するソース打ち込み領域の部分をカバーする。次に、このスペーサーをマスクとして使用することにより、ソース打ち込み領域の露出部分をエッチングし、除去する。次に、スペーサーの下の残りのソース打ち込み領域を駆動し、ソース領域を形成する。その後、エッチングされた領域内に、浅い高導電タイプの接点領域を形成し、次に、デバイスの上にソースおよびドレイン接点を形成する。

(もっと読む)

モノリシック集積型エンハンスメントモードおよびデプリーションモードFETおよびその製造方法

【課題】 製造コストを低減し品質の均一性および安定性を高めたモノリシック集積型エンハンスメントモード/デプリーションモードFETデバイスを提供する。

【解決手段】 単一の半導体多層構造でデプリーションモード(Dモード)FETをエンハンスメントモード(Eモード)FETとモノリシックに集積回路化する。上記多層構造にはチャネル層を設け、その上に障壁層をオーバーレイし、さらにその上にオームコンタクト層をオーバーレイする。これらDモードFETおよびEモードFETのソースコンタクトおよびドレーンコンタクトをオームコンタクト層に接続する。またDモードFETおよびEモードFETのゲートコンタクトを障壁層に接続する。障壁層の中のEモードゲートコンタクトの下に非晶質化領域を設ける。この非晶質化領域が障壁層との間の埋込みEモードSchottkyコンタクトを構成する。代わりに実施例ではDモードFETのゲートコンタクトを障壁層にオーバーレイした第1の層に接続し、その第1の層の中にDモード非晶質化領域を形成する。

(もっと読む)

化合物半導体発光素子の製造方法

【課題】 本発明は、1回のワイヤボンディングで済み、位置合わせの容易な実装が可能で、工数の低減につながるチップを作製することを課題とする。

【解決手段】 基板11の一面上に、n型半導体薄膜層13と、活性層と、p型半導体薄膜層17とを積層形成し、このp型半導体薄膜層17上面に一方の電極32を基板11の他面上に他方の電極33aを設ける化合物半導体発光素子の製造方法において、基板11の他面側から電極33aと接続されるn型半導体薄膜層13に到達する深さの縦穴20を波長が500nm以下の短波長レーザを照射して設け、基板11の他面に設けた電極33aとn型半導体薄膜層13を縦穴20に形成した導電性材料30を介して電気的に接続し、電極32を基台100の第1のリード電極101に接続し、電極33aを第2のリード電極103にワイヤボンド線104で接続する。

(もっと読む)

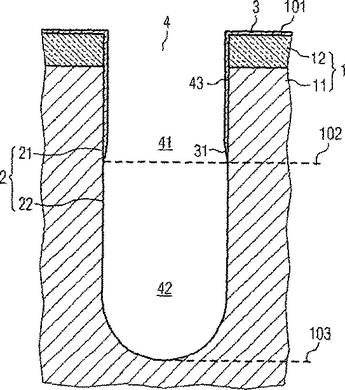

半導体装置

【課題】低オン抵抗の縦型トランジスタが形成されてなる半導体装置を提供する。また、マルチチャネル化の自由度の高い半導体装置を提供する。

【解決手段】半導体基板30の一方の表面である主面側に形成された第1電極と、もう一方の表面である裏面側に形成された第2電極とを有する縦型トランジスタ101が形成されてなる半導体装置100であって、第1電極が、主面上に形成された層間絶縁膜43を介して、主面側の半導体基板30表層部に形成された拡散領域41,42,48に接続する第1金属層44からなり、裏面側には、半導体基板30の内部に向かってトレンチ35が形成され、第2電極が、トレンチ内に形成され、トレンチ35によって露出された半導体基板30内の半導体層33に接続する第2金属層37からなる半導体装置100とする。

(もっと読む)

561 - 569 / 569

[ Back to top ]