Fターム[4M106AD02]の内容

半導体等の試験・測定 (39,904) | パッド(電極) (883) | 配列、配置 (168) | スクライブ部 (84)

Fターム[4M106AD02]に分類される特許

1 - 20 / 84

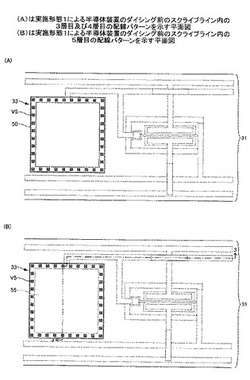

半導体装置、半導体ウェハ及び半導体装置の製造方法

【課題】ダイシングの際にクラック発生を抑制できる半導体装置を提供する。

【解決手段】半導体基板の上に形成された複数の配線層と、前記複数の配線層の間に配置されたビア層と、前記複数の配線層に形成された導電膜と、前記ビア層の上下の前記配線層の前記導電膜と接続するビアプラグV5とを有し、スクライブ領域31は、チップ領域の外周であって前記半導体基板の縁に接して位置し、前記スクライブ領域31は前記縁に接するパッド領域33を有し、前記パッド領域33は、前記複数の配線層の各々に、平面視において相互に重なって配置され、前記複数の配線層は、第1の配線層と第2の配線層を有し、前記第1の配線層の前記導電膜は、前記パッド領域33の全面に形成された第1の導電パターン55を有し、前記第2の配線層の前記導電膜は、前記パッド領域の一部に形成された第2の導電パターン50を有する。

(もっと読む)

半導体ウエハ

【課題】複数のタイミングで半導体チップの電気特性を高精度に評価することができ、スクライブ領域の総メタル量を低減することが可能な半導体ウエハを提供する。

【解決手段】半導体ウエハ1は、複数の配線層が積層され、平面視において複数の半導体チップ領域Cと、複数の半導体チップ領域Cを分離するスクライブ領域Sとを有し、スクライブ領域Sに配置された電気特性評価用のモニタ素子10と、スクライブ領域Sに配置され、モニタ素子10と接続され、複数の配線層のうちいずれかの配線層に形成された第1の電極パッド20と、半導体チップ領域Cに配置され、第1の電極パッド20と接続され、第1の電極パッド20が形成された配線層よりも上層に形成された第2の電極パッド40を備えている。

(もっと読む)

電子部品、電子部品の製造方法、基板

【課題】チッピング検出用配線が他の部材で覆われている状態であっても、ダイシングによって電子部品を形成した後に、チッピング検出用配線の導通状態を検出するための電圧を印加できる基板を提供する。

【解決手段】電子部品40は、互いに平行を成す一方の主面41aと他方の主面41bが矩形状の基体41を有する。基体41の一方の主面41aには、第一チッピング検出用配線42が配されている。また、基体41の他方の主面41bには、第二チッピング検出用配線44が配されている。第一チッピング検出用配線42は貫通配線43aを介して第二チッピング検出用配線44に電気的に接続される。

(もっと読む)

半導体装置

【課題】LSIチップの製造コストを低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板に形成され、第1の電源配線を含む第1の電源配線層を備える複数のLSI領域と、前記半導体基板に形成された第1の電源端子と、前記LSI領域の間のダイシングライン領域に、前記LSI領域と前記ダイシングライン領域とを区画するダイシングラインに沿って形成され、前記第1の電源配線と前記第1の電源端子とを電気的に接続する第2の電源配線を含む第2の電源配線層と、を備える。少なくとも前記LSI領域において、前記第1の電源配線と前記第2の電源配線との境界にバリアメタル膜が形成されている。

(もっと読む)

半導体装置

【課題】本発明は、TEGを備えた半導体装置において、1枚の半導体基板から取得可能な半導体チップの数を増加させることの可能な半導体装置を提供することを課題とする。

【解決手段】第1のスクライブ領域11の幅W1をTEG用パッド21〜24の幅W3よりも広くして、第1のスクライブ領域11にTEG18及びTEG用パッド21〜24を配置すると共に、第1のスクライブ領域11と交差する第2のスクライブ領域12の幅W2をTEG用パッド21〜24の幅W3よりも狭くする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極パッド部の安定した電気的接触を確保しつつ電極パッド部の面積を小さくすることができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主表面上であって平面視において素子形成領域内およびダイシングライン領域内の少なくともいずれかに形成された半導体チップ用電極パッド部,TEG用電極パッド部PTとを備えている。半導体チップ用電極パッド部,TEG用電極パッド部PTは、外部と電気的に接続するための表面OSFを有し、かつ半導体チップ用電極パッド部,TEG用電極パッド部PTの辺SIDに対して斜めに傾斜した方向に延びた溝部THPを表面OSFに有している。

(もっと読む)

半導体素子における配線不良検出方法、半導体ウェーハ及び半導体素子

【課題】製品用半導体ウェーハについて配線不良を検出することが可能で、かつ、製品となる各半導体素子について配線不良を検出することが可能な、半導体素子における配線不良検出方法を提供する。

【解決手段】半導体ウェーハ10に複数の半導体素子100を製造する際に、素子形成領域R1の外周部に形成する接地配線112よりもさらに外周側に当該接地配線112よりも細い不良検出用配線122を各半導体素子100に形成するとともに、不良検出用配線122に接続された測定用端子124を素子形成領域R1の周囲のスクライブ領域R2に形成しておき、当該測定用端子124を用いて配線不良を検出することを特徴とする半導体素子における配線不良検出方法。

(もっと読む)

マザー基板、電子部品の検査方法、電子部品、及び電子部品の製造方法、並びに電子機器

【課題】電子部品の貫通電極において、基板の両面から貫通電極に接触することが必要であることに起因して高度な検査技術が必要である貫通電極の検査を容易にすることができる、マザー基板、電子部品の検査方法、電子部品、及び電子部品の製造方法、並びに電子機器を提供する。

【解決手段】電子部品の製造方法は、マザー基板に区画形成された電子部品の製造方法であって、基板の第1面における複数の区画領域に回路を形成する回路形成工程と、区画領域にて、第1面と第1面の反対面である第2面とを電気的に接続する貫通電極を形成する貫通電極形成工程と、互いに異なる区画領域に位置する貫通電極を第1面にて連結配線で電気的に接続する連結配線形成工程と、第2面にて、連結配線形成工程で電気的に接続された複数の貫通電極に検査プローブを電気的に接続させることによって、貫通電極の機能を検査する機能検査工程と、を有する。

(もっと読む)

試験装置

【課題】プローブ検査においても、理想の電源環境を提供する。

【解決手段】試験装置は、ウエハ上に形成されたDUT1を試験する。電源補償回路20は、制御信号SCNT1、SCNT2に応じて制御されるソーススイッチSW1、シンクスイッチSW2を含み、それぞれがオンした状態において補償パルス電流ISRC、ISINKを生成し、補償パルス電流ISRCをメイン電源とは別経路からDUT1の電源端子P1に注入し、またはメイン電源からDUT1へ流れる電源電流から、補償パルス電流ISINKをDUT1とは別経路に引きこむ。電源補償回路20のうち、ソーススイッチSW1、シンクスイッチSW2を含む一部は、ウエハW上に形成される。ウエハには、ウエハ上に形成される電源補償回路20の一部に信号を印加するためのパッドP5〜P7が設けられる。

(もっと読む)

半導体装置

【課題】外部ループバックテストが容易な半導体装置を提供する。

【解決手段】主面に形成された格子状のダイシングライン14、15と、ダイシングライン14、15で囲まれた矩形状格子に形成され、信号出力パッド24有する送信回路22と、信号入力パッド25を有する受信回路23と、送信回路22および受信回路23に入出力されるデータを処理する内部回路21とを有する複数の集積回路12と、ダイシングライン14、15上に形成され、信号出力パッド24と信号入力パッド25間を電気的に接続する信号配線26とを具備する。

(もっと読む)

半導体装置およびその製造方法ならびに半導体ウエハ

【課題】ダイシングブレードの寿命を延ばすことができるとともに、半導体装置のエッジ部へのダメージを低減できる半導体装置を提供する。

【解決手段】機能素子領域2においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続される上配線29およびキャップメタル層32が形成されている。下配線25はCu以外の配線材料からなり、上配線29はCuからなる。このキャップメタル層32におけるパッシベーション膜33のパッド開口34から露出した部分が第1パッド6である。一方、スクライブ領域3においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続されるキャップメタル層32が形成されている。このキャップメタル層32におけるパッシベーション膜33のパッド開口44から露出した部分が第2パッド10である。

(もっと読む)

半導体装置

【課題】半導体チップを切り出す際に生じるばりによる半導体装置の歩留まりの低下及び信頼性の低下を防止し且つ半導体チップの取り数を向上させることができるようにする。

【解決手段】上面に複数のボンディングパッド14と複数の検査用パッドのパッド断片19とが形成された平面方形状の半導体チップにおいて、複数のパッド断片19は半導体チップの4辺のうちの対向する2辺に沿って形成されている。複数のボンディングパッド14は異なる2辺に沿って形成されている。

(もっと読む)

半導体装置および半導体装置の検査方法

【課題】検査に用いるプローブの耐久性を向上できる半導体装置を提供する。

【解決手段】ウエハーのスクライブ線150上に配置された第1チェック素子1を具備する。第1チェック素子1は、第1配線絶縁膜5と、第1配線絶縁膜5の第1開口部に配置された第1チェック素子パッド10とを備える。第1チェック素子パッド10は、導電性の第1パッドメタル部12と、矩形の平面形状を有する絶縁性の第1ダミー部13とを含む。第1ダミー部13の平面形状は、スクライブ線150の長手方向と垂直な2つの第1長辺と、第1チェック素子パッド10の外周部近傍に配置される2つの第1短辺とを含む。

(もっと読む)

半導体ウェハ

【課題】テストパッドの数を減らすことができ、かつウェハ状態で各トランジスタを個別にテストすることができる半導体ウェハを得る。

【解決手段】半導体ウェハ1内に複数の半導体装置2が行列状に配置されている。複数の半導体装置2を分離するためのダイシングライン3が設けられている。各半導体装置2は、複数のトランジスタ4を含む。複数のトランジスタ4のコレクタ(第1端子)に、それぞれ個別に複数のテストパッド5(第1テストパッド)が接続されている。複数のトランジスタ4のエミッタ(第2端子)に接地電極11が共通に接続されている。複数のトランジスタ4のベース(制御端子)に、ダイシングライン3内を通る配線6を介して、共通にテストパッド7(第2テストパッド)が接続されている。

(もっと読む)

半導体装置

【課題】針傷を防止し、有効チップ数の減少を抑える半導体装置を提供すること。

【解決手段】対象チップ2−1は、ウェハ1に設けられている。隣接チップ2−2は、ウェハ1に設けられ、対象チップ2−1に隣接する。ボンディングパッド3は、対象チップ2−1の表面に設けられている。スクライブ領域4は、ウェハ1の対象チップ2−1と隣接チップ2−2との間に設けられ、ウェハ1の検査後にダイシングされる。貫通ビア5は、対象チップ2−1又は隣接チップ2−2に設けられている。表面配線6は、ボンディングパッド3からスクライブ領域4を介して対象チップ2−1又は隣接チップ2−2の表面の貫通ビア5に接続されている。検査用パッド7は、対象チップ2−1又は隣接チップ2−2の裏面に設けられている。裏面配線8は、対象チップ2−1又は隣接チップ2−2の裏面の貫通ビア5から検査用パッド7に接続されている。

(もっと読む)

半導体装置

【課題】チップサイズパッケージのように半導体基板上に再配線と外部接続端子とを形成するパッケージにおいて、再配線を短く形成して、回路ブロック間のアイソレーションを高めるように半導体基板の中央部にPADを配置する場合にも、ウエハ検査プローブが相互に接触することがないように対策する。

【解決手段】半導体装置を構成する半導体基板2を縦方向及び横方向に2分割して、半導体基板2を合計4つの四角形状の領域である回路領域a 101、回路領域b 102、回路領域c 103、回路領域d 104に区分する。前記4つに区分された回路領域では、各々、外周に沿って複数個のPAD200が配置される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の組み立てにおいて再配線形成後にも電気的特性検査を実施する。

【解決手段】再配線形成後のダイシング工程において、レーザーダイシングとブレードダイシングを行うことで、半導体ウェハのダイシング領域1c上に形成された再配線9e等の厚いメタル層であっても前記メタル層を残すことなくきれいに切断を行うことができるようになり、その結果、再配線形成後にもダイシング領域1c上に配置されたテスト用電極パッド9sを用いて半導体ウェハや再配線9e等の電気的特性検査を行うことができる。

(もっと読む)

半導体装置の製造方法、および、それに用いる半導体ウェハ

【課題】多層配線層の検査工程を含む半導体装置の製造技術において、検査の迅速性を損なうことなく、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体ウェハの主面上に中間配線層(工程s03,s05)、ビア層(工程s04,s06)、最上配線層(工程s07)を形成する。中間配線層を形成した後の電位コントラスト観察工程vc01,vc02と、最上配線層を形成した後の電気的検査工程ec01とを有する。中間配線層は、平面積が大きい第1配線パターンと、面積が小さく、浮遊状態となる第2配線パターンとを有する。最上配線層は、第1配線パターンに導通する第1最上配線パターンと、第2配線パターンに導通する第2最上配線パターンとを有する。電気的検査では、第1最上配線パターンと第2最上配線パターンとの間に電位差を与えて導通状態を検査する。

(もっと読む)

半導体ウェハの検査方法及び半導体ウェハの検査装置

【課題】電極パッドに対してプローブピンを確実に接触させ、半導体ウェハに備えられる半導体チップ全てを漏れなく確実に検査可能な半導体ウェハの検査方法及び検査装置を提供する。

【解決手段】半導体ウェハ50に、予め、少なくとも1以上のダミーパッド53を設け、プローブカード3は、ダミーパッド53に対応する配列でダミープローブピン33を備えており、電極パッド52が複数並べられてなるパッド列57の配列方向に対して交差する一方向側から、電極パッド52にプローブピン32を接触させるとともに、前記一方向と反対側の方向から、ダミーパッド53にダミープローブピン33を接触させ、ダミープローブピン33は、プローブピン32よりも少ない本数とされ、且つ、ダミープローブピン33のダミーパッド53への接触荷重F2を、プローブピン32の各々の電極パッド52への接触荷重F1よりも大きな荷重として検査を行なう。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体ウェハ上における同層のショット間の位置の合わせずれ量を高精度で測定及び検出できるようにする。

【解決手段】半導体装置は、ウェハ状の半導体基板における、第1の露光でパターニングされる少なくとも1つのチップ領域1の周縁部に、第2の露光によって二重露光されてなり、第1の露光及び第2の露光における縦方向又は横方向の互いの位置の合わせずれ量を電気的に測定する検査用評価素子5abを有している。検査用評価素子5abは、第1の露光によって形成される第1の配線パターン5aと、第2の露光によって形成される第2の配線パターン5bとから形成されている。

(もっと読む)

1 - 20 / 84

[ Back to top ]