Fターム[4M106BA14]の内容

半導体等の試験・測定 (39,904) | 手段 (6,361) | 電圧の印加 (693)

Fターム[4M106BA14]に分類される特許

681 - 693 / 693

エッチング条件の設定方法、半導体装置の製造方法、及び半導体装置

【課題】 少ない労力でビアホール等を形成するときのエッチング条件が適切か否かを確認できるようにする。

【解決手段】 基準部、該基準部より低地である低地部、及び前記基準部より高地である高地部を有する半導体基板1上に、導電膜2及び層間絶縁膜3を形成し、層間絶縁膜3の表面を平坦化する。層間絶縁膜3をエッチングすることにより、低地部の上方に位置する第1及び第2の接続孔3a、前記基準部の上方に位置する第3の接続孔3b、及び高地部の上方に位置する第4の接続孔3cを同時に形成する。第1〜第4の接続孔3a〜3cそれぞれに、第1〜第4の導電体4a〜4cを埋め込む。層間絶縁膜3上に、第1の導電体3a、第3の導電体4b及び第4の導電体4cを互いに接続する上部電極5bを形成し、上部電極5bと、第1の導電体3aとの間の抵抗を測定する。

(もっと読む)

半導体装置の評価方法。

【課題】 簡便に、注目する要素もしくはパラメータに対する評価を行うことができる評価方法を提供する事を課題とする。また、より正確な結果を得ることができる評価方法を提供する事を課題とする。また、より迅速に結果を得ることができる評価方法を課題とする。

【解決手段】 本発明は、複数の評価回路を同じ基板上に形成し、その複数の評価回路を同時に動作させ、該基板上に形成された選択回路により選択された一の評価回路の出力を適宜評価することを要旨とする。

(もっと読む)

電気的接続装置

【課題】 基板の上面及びその上方空間を有効に利用可能にすることにある。

【解決手段】 電気的接続装置は、複数の接続ランドを下面に有する基板と、基板の中央に位置された支持体であって、基板と平行に伸びかつ厚さ方向に貫通する複数の第1の貫通穴を有する板部、及び板部と共同して内側空間を形成すべく板部の上方に位置する支持部を備える支持体と、板部の下側に配置されたプローブ組立体であって、上下方向へ伸びる複数のプローブを備えると共に、プローブが状態に差し込まれた複数の第2の貫通穴を有するプローブ組立体と、プローブと前記接続ランドとを接続する複数の配線であって一端が第1の貫通穴に上方から差し込まれた複数の配線とを含む。支持部は内側空間をその周りの外側空間に連通させる連通空間を有しており、配線は連通空間に通されている。

(もっと読む)

ウエハ測定装置および測定方法

【課題】 ウエハの研磨面となる表面を非接触にした状態で、このウエハの導電型を判別することが可能なウエハ測定装置および測定方法を提供する。

【解決手段】 電極プレート部11と電極ピン12とを備え、ウエハ31に電極プレート部11の電極面11bおよび電極ピン12を接触させた状態でこれらの電極面11bと電極ピン12との間に電圧を印加して、この際の電極面11bと電極ピン12との間で電流が流れる方向を判別し、ウエハ31の導電型を判別する構成とされたウエハ測定装置10であって、電極プレート部11には電極面11bにウエハ31を吸着保持する負圧吸引手段が備えられ、電極ピン12は電極面11bに対して出没可能に設けられている。

(もっと読む)

電気的接続装置

【課題】 下板の撓みを防止することにある。

【解決手段】 電気的接続装置は、上板と、該上板から下方に間隔をおいた下板と、上板及び下板の間に配置された枠状の第1のスペーサと、上板、上板及びスペーサにより形成される内側空間にあって上板及び下板の間に配置された第2のスペーサと、該第2のスペーサの配置位置を避けて内側空間を通る状態に上板及び下板を上下方向に貫通する複数のプローブとを含む。各プローブの上端及び下端は、上板及び下板と平行の面内において一方向に相対的にずれている。

(もっと読む)

非振動式接触電位プローブを使用した表面検査

材料の表面上の欠陥または汚染を特定する方法およびシステム。この方法およびシステムでは、半導体ウェハなどの材料を提供し、非振動式接触電位差センサを用いてウェハを走査し、接触電位差データを発生し、このデータを処理して、欠陥または汚染の特性を示すパターンを特定する。

(もっと読む)

(もっと読む)

集積回路製造をモニタするためのテスト構造体またはライン・アレイを接続するための方法および構成

テスト・チップは、各領域が少なくとも1つのテスト構造体を含むことができる複数領域のアレイを有する少なくとも1つのレベルを具える。その少なくとも幾つかの領域はそれぞれのテスト構造体を含む。そのレベルは、テスト構造体に入力信号を供給する複数のドライバ・ラインを有する。そのレベルは、テスト構造体から出力信号を受信する複数の受信機ラインを有する。そのレベルは、電流を制御するための複数のデバイスを有する。各テスト構造体は、ドライバ・ラインの中の少なくとも1本のラインに、その間にあるそのデバイスの中の第1のデバイスで接続される。各テスト構造体は、受信機ラインの中の少なくとも1本のラインにその間にあるそのデバイスの中の第2のデバイスで接続されていて、そのテスト構造体の各々がドライバ・ラインおよび受信機ラインを用いてテストを行うべく個々にアドレス可能である。  (もっと読む)

(もっと読む)

半導体処理ステップに関連するエッチ・バイアスを決定する試験装置及び方法

半導体処理ステップに関連するエッチ・バイアスを決定するテスト装置であって、基板と、基板上にあり第1の幅を有する第1のカソード層と、基板上にあり第2の幅を有する第2のカソード層と、基板上にあるカソードの大きな面積とを含んでおり、カソードの大きな面積は、第1及び第2の幅のいずれよりも実質的に大きな第3の幅W“及び長さL”を有する。  (もっと読む)

(もっと読む)

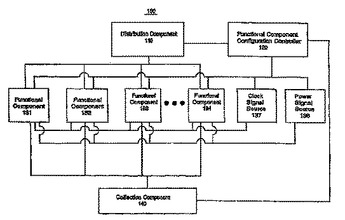

半導体機能回路のテストおよび構成のためのシステムおよび方法

集積回路において機能要素の構成を可能にするためのシステムおよび方法が開示される。本発明のシステムおよび方法が、製造欠陥、柔軟性特性、性能要求、およびシステムの健全性(例えば、適切に動作する要素の数)を含む種々の要因に基づいて、集積回路ダイの機能要素の動作特性を柔軟に変更し得る。様々なレベルの構成抽象化および要素組織化(例えば、トポロジーインバージョン解析)で、機能要素動作挙動がテストおよび解析される。テストおよび解析は、多数の機能要素で並列に実行され得る。様々なレベルの粒度および実時間で、グラフィカルユーザインタフェース(GUI)に機能要素構成関連の情報が提示される。グラフィカルユーザインタフェースは、フェイルパターンの認識、生産テストの調整、およびフィールド構成アルゴリズムの調節においてユーザの相互作用を容易にし得る。また、テストおよび解析情報は、種々の使いやすいデータベース形式で組織化され得る。  (もっと読む)

(もっと読む)

ゴールデンサンプルによるテスタ及びテストボードの較正

自動試験機器(ATE)における試験の実施において、RF(無線周波数)電力を正確に生成する及び測定することは、難題である。例示的な一実施例においては、増幅器(140)の入力及び出力特性を測定するのに使用される試験装置(100)において、試験プログラムパラメータを決定する方法が提供される。前記方法(200)は、前記試験装置の電源から増幅器(220)の入力までの入力損失を計算するステップと、入力損失補正係数を規定するステップとを有する。前記増幅器(220)の出力から前記試験装置の電力計までの出力損失が計算され、出力損失補正係数が規定される。前記入力損失補正係数(230)を使用して、実際の入力電力レベルが決定され、前記出力損失補正係数(230)を使用して、実際の出力レベルが決定される。  (もっと読む)

(もっと読む)

プローブカード

【課題】 狭ピッチでの配置が可能であり、検査用電極の高さバラツキを十分に吸収して各検査用電極に対してコンタクトピンを安定して接触させ、かつ高速信号伝送を実現する。

【解決手段】 半導体チップの電気的特性を検査するために半導体チップの検査用電極と接触接続されるコンタクトピンが配線基板の表面に複数植設されたプローブカードにおいて、コンタクトピンをマイクロスプリング構造とする。

(もっと読む)

プローブ検査装置及びプローブ検査方法

【課題】 接触状態でのプローブ先端の位置及びプローブの最適な押し込み深さを事前に測定することができるプローブ検査装置及びプローブ検査方法を提供する。

【解決手段】 被検査物と同じ程度の平坦な接触面を有する変形体7と、複数のプローブ1からなるプローブカード3と、接触面と複数のプローブ1を接触させる手段と、接触面上に形成された複数のプローブ痕8を観察する手段と、複数のプローブ痕8の開口の大きさ及び複数のプローブ先端痕の位置を測定する手段と、複数のプローブ痕8の開口の大きさからプローブ1の押し込み深さを算出する手段とを有する。

(もっと読む)

半導体装置、半導体装置の製造方法及び試験方法

【課題】本発明は、複数の半導体素子が連なった状態で封止され、画像認識により位置決めされて試験に供される半導体装置、半導体装置の試験製造方法及び半導体装置の試験方法に関し、既存のウェーハプローバで認識可能なアライメントマークを容易に形成することを課題とする。

【解決手段】 半導体チップ14の電極を所定の位置に配置された電極パッドに接続するための再配線層18を半導体チップ14上に形成する。ハンダボール22が形成されるメタルポスト16を再配線層の電極パッド上に形成する。再配線18上に、メタルポスト16と所定の位置関係で配置されたアライメントマークを提供するマーク部材24を形成する。マーク部材24はメタルポスト16と同じ材質で形成される。

(もっと読む)

681 - 693 / 693

[ Back to top ]