Fターム[4M106DD11]の内容

半導体等の試験・測定 (39,904) | ウェーハ・プローバ(接触型検査装置) (3,541) | プローブ (3,210) | 回路配置 (92)

Fターム[4M106DD11]に分類される特許

1 - 20 / 92

試験信号仲介基板

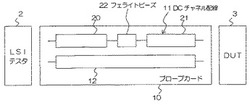

【課題】 伝搬遅延時間の測定値が所定範囲外になる恐れがある配線が、外部のLSIテスタによって測定対象となっても、LSIテスタにエラー処理を実行させないようにできるプローブカードを提供する。

【解決手段】 プローブカードの少なくとも一部の配線はそれぞれ、自配線の一端に、投入された伝搬遅延時間測定用のパルス波形を、自配線の他端以外の箇所で反射させる反射箇所規定構造を有する。例えば、反射箇所規定構造を有する配線は、LSIテスタ寄りの配線部分と、DUT寄りの配線部分と、これらの配線部分間に介挿された、パルス波形の周波数成分に対し、各配線部分より高インピーダンスのフェライトビーズとを有し、LSIテスタ寄りの配線部分とフェライトビーズとの境界をパルス波形の反射箇所にしている。

(もっと読む)

検査装置及び検査システム

【課題】汎用性を有し、高速で動作する半導体装置を検査できる検査装置を提供する。

【解決手段】検査装置は、第1貫通電極24bと、テスト信号を生成する信号生成ユニット30とを有する第1半導体基板24と、複数の接触子60を有するプローブ基板27と、第2貫通電極25bと、複数の接触子60と信号生成ユニット30との間の信号経路をプログラム可能に設定するスイッチマトリックス20eとを有する第2半導体基板と、を備え、第1半導体基板24と第2半導体基板25とは積層されており、第1貫通電極24bは、信号生成ユニット30が生成したテスト信号をスイッチマトリックス20eに伝達し、第2貫通電極25bは、スイッチマトリックス20eによって経路設定されたテスト信号を所定の接触子60に伝達し、信号生成ユニット30から、着脱自在に接続される電気的接続部を介さずに、接触子60にテスト信号が伝達される。

(もっと読む)

プローブ装置

【課題】パワーデバイスの静特性及び動特性の双方をウエハレベルで測定することができ、特に静特性に使用される測定ラインに影響されることなく、パワーデバイスの動特性をウエハレベルで確実に測定することができるプローブ装置を提供する。

【解決手段】本発明のプローブ装置10は、複数のパワーデバイスが形成されたウエハWを載置する移動可能な載置台12と、載置台12の上方に配置された複数のプローブ14Aを有するプローブカード14と、載置台12の載置面とその外周面に形成された導体膜電極13と、導体膜電極13とテスタ17とを電気的に接続する測定ライン16と、を備え、載置台12上のパワーデバイスの電気的特性をウエハレベルで測定するプローブ装置であって、第2の測定ライン16には、導体膜電極13とテスタ17の間で測定ライン16の電路を開閉するスイッチ機構18を設けたものである。

(もっと読む)

テストシステム

【課題】ノイズ減衰の効果を損なうことなく、低コストで、半導体装置の電気的測定のテスト時間を短縮する。

【解決手段】半導体テスタ2に設けられた電源回路4は、動作電源として半導体装置DUTに供給する電源電圧VCC、電源電圧VCCと略同じ電圧レベルの電源電圧VCC1を生成する。半導体装置DUTが搭載されるテスト用ボード3には、電源電圧VCCのノイズを除去するコンデンサ5,6を有している。470μF程度の静電容量値を有するコンデンサ5は、電源電圧VCCが接続される電源ライン7と電源回路4が生成する電源電圧VCC1が接続される電源ライン8との間にそれぞれ接続されている。コンデンサ5をACカップリング接続することにより、コンデンサ5の充放電時間をキャンセルしながら、電源電圧VCCに印加されるノイズを除去する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】半導体集積回路装置の電気的テストにおいて、テストヘッド内の電源からプローブ等に至る比較的長い経路を介して供給される電源電圧の変動を防止するために、通常、テストボード上等に、電界コンデンサ等の大容量のバイパスコンデンサを設置している。しかし、大容量のバイパスコンデンサで吸収できる変動は、せいぜい数十ナノ秒程度の比較的短時間の変動のみであり、100ナノ秒を超えるような比較的長時間の変動には対応できない。

【解決手段】本願発明は、半導体集積回路装置の製造工程中において、半導体集積回路装置の電気的テストを実行するに当たり、電源電圧をテストボード上に設けられた電池から供給するものである。

(もっと読む)

プローブ装置

【課題】パワーデバイスの静特性及び動特性(スイッチング特性)をウエハレベルで確実に測定することができるプローブ装置を提供する。

【解決手段】本発明のプローブ装置10は、ダイオードを含むパワーデバイスが複数形成された半導体ウエハWを載置する移動可能な載置台12と、載置台12の上方に配置されたプローブカード13と、少なくとも載置台12の上面に形成された導体膜と半導体ウエハWの裏面に形成された導体層とが導通する状態で半導体ウエハWにプローブ13Aを電気的に接触させてパワーデバイスの電気的特性をウエハレベルで測定するテスタ15と、を備え、プローブカード13の外周縁部に導通ピン14を設け、パワーデバイスの電気的特性をウエハレベルで測定時に、導通ピン14を介して載置台12の導体膜電極(コレクタ電極)とテスタ15とを電気的に接続する。

(もっと読む)

プローブカードのリペア方法及びこれを利用するプローブ基板

【課題】本発明は、プローブカードのリペア方法及びリペアされたプローブ基板に関する。

【解決手段】相対する位置に第1及び第2の主面を有するセラミック焼結体からなる基板本体において、上記第1の主面に形成された第1のパッドと前記第2の主面に形成された第2のパッドとを電気的に連結するための複数のメインチャンネルと、当該メインチャンネルに隣接して損傷されたメインチャンネルをリペアするための予備チャンネルとを備える基板本体を用意する段階と、メインチャンネルが損傷された場合に当該メインチャンネルと上記予備チャンネルとに形成された第1及び第2のパッドを除去する段階と、上記損傷されたメインチャンネルと当該メインチャンネルに隣接する予備チャンネルとの間の基板を一部除去してキャビティーを形成する段階と、当該キャビティーに損傷されたメインチャンネルと上記隣接する予備チャンネルが電気的に連結されるようにリペア連結部を形成する段階とを含む。

(もっと読む)

半導体測定装置及び測定方法並びにそれに用いる同軸プローブ針ユニット

【課題】 薄いウエハでも撓みなく支持でき、測定される半導体素子が切り替わった場合でも、ウエハの裏面電極と接触するプローブ針を移動させる必要のない半導体測定装置及び測定方法並びに同軸プローブ針ユニットを提供すること。

【解決手段】 試験対象ウエハを支持する支持面を備えたウエハチャックと;ウエハチャックを上プローブ針に対して相対的に上下方向及び水平方向に移動させる移動機構と;ウエハチャックに保持され、前記支持面内でマトリックス状に配置されている複数の下プローブ針と;上プローブ針と電気的に接続されるとともに、複数の下プローブ針の各々と選択スイッチを介して接続されるテスタ装置と;測定位置にある半導体素子に対応する下プローブ針がテスタ装置と電気的に接続されるように選択スイッチを切り換える切換装置とを有している半導体測定装置及び測定方法、並びに同軸プローブ針ユニットを提供することによって解決する。

(もっと読む)

試験装置及び試験方法

【課題】光インターフェースを備える被試験デバイスを試験する。

【解決手段】被試験デバイスを試験する試験装置であって、被試験デバイスを試験する試験信号を発生する試験信号発生部と、試験信号を光試験信号に変換する電光変換部と、電光変換部が変換した光試験信号を被試験デバイスの光入力部に伝送すると共に、被試験デバイスが出力する光応答信号を受け取って出力する光インターフェース部と、光インターフェース部が出力する光応答信号を電気信号の応答信号に変換して送信する光電変換部と、光電変換部が送信する応答信号を受信する信号受信部と、を備える試験装置および試験方法を提供する。

(もっと読む)

半導体集積回路用テスト回路

【課題】トランジスタの特性と配線系における配線負荷の特性とを高精度で分離でき、配線負荷に大きな影響を及ぼす層間絶縁膜等の特性を評価できる技術を提供することである。

【解決手段】(2k+1:kは1以上の整数)個のインバータを具備したリング発振回路を有してなり、隣接するインバータの間に、各々、同一インピーダンス値の負荷回路が設けられてなる半導体集積回路用テスト回路。

(もっと読む)

半導体検査用プローブカードおよびその製造方法

【課題】接触方式と非接触方式を用いた検査装置における検査コストの低減が可能な半導体検査用プローブカードおよびその製造方法を提供する。

【解決手段】

本発明の半導体検査用プローブカードは、基材と、前記基材の第一の主面に配置されたプローブカード基板と、非接触結合回路を備えた検査用LSIと、電源供給ピンと、を有し、前記検査用LSIと前記電源供給ピンは、前記基材の第一の主面と反対側の第二の主面上に配置され、前記プローブカード基板と前記検査用LSIが電気的に接続され、前記プローブカード基板と前記電源供給ピンが電気的に接続される。

(もっと読む)

コンタクタ、半導体装置の試験装置、及び半導体装置の製造方法

【課題】コンタクタ、半導体装置の試験装置、及び半導体装置の製造方法において、試験の信頼性を高めること。

【解決手段】第1の材料を含むコンタクタ母材1と、コンタクタ母材1の先端部1aのうち、半導体装置30の電極31との接触面1bにのみ選択的に形成された、第2の材料を含む導体膜10aとを有するコンタクタ9による。

(もっと読む)

プローブカード及びそれを備えるテスト装置

【課題】スイッチの動作時に半導体素子に印加されうるスパークを低減させ、電気的特性測定値の信頼性を向上させることができるプローブカード及びそれを備えるテスト装置を提供する。

【解決手段】本発明によるプローブカードは、第1入力端と第1入力プローブピンとを接続する第1入力端MEMS(Micro Electro Mechanical Systems)スイッチと、第1出力端と第1出力プローブピンとを接続する第1出力端MEMSスイッチとを有し、前記第1入力端MEMSスイッチは、動作信号を受信する制御部と、前記第1入力端と前記第1入力プローブピンとを接続する接続部とを含み、前記第1出力端MEMSスイッチは、動作信号を受信する制御部と、前記第1出力端と前記第1出力プローブピンとを接続する接続部とを含む。

(もっと読む)

プローブカード及びそれを用いた半導体ウェーハの検査方法

【課題】ウェーハに対して非接触状態の容量性結合又は誘導性結合により信号の授受を行う際にこれらの電磁的結合をより大きくして信号の授受を安定して行えるようにするプローブカードの提供。

【解決手段】ウェーハ4と対向する第1の面上で、且つ各パッド電極4aと対向する位置に設けられた複数のバンプ電極3a及び容量性結合又は誘導性結合によりパッド電極と電気的に接続される非接触パターン3bを有する薄膜基板3と、薄膜基板の反対側に配置され、バンプ裏面電極と対向する位置に設けられた複数の電極21aを有する配線基板2とを備えている。第1の密閉空間5及び第2の密閉51が減圧されることにより、バンプ裏面電極と電極21aとが密着されると共にパッド電極とバンプ電極とが密着される。第1及び第2の密閉空間はそれぞれの圧力が独立して調整できる。

(もっと読む)

半導体集積回路の製造方法

【課題】狭ピッチ化されたテストパッドを有する半導体集積回路装置の電気的検査を実現する。

【解決手段】複数のチップ領域に区画され、上記複数のチップ領域の各々には半導体集積回路が形成され、主面上において上記半導体集積回路と電気的に接続する複数の電極が形成された半導体ウエハを用意し、上記複数の電極に接触可能な複数の接触端子を有するプローブカードを用意する。このとき、上記複数の電極に接触させるための複数の接触端子(7)と、上記複数の接触端子と上記第1配線とに電気的に接続する第2配線と、上記複数の接触端子の近傍に形成され、上記第2配線に接続された受動素子による電気回路と含む第1シート(2)を用意し、その後、上記複数の接触端子が形成された領域を上記第1シートの裏面より押圧可能な状態に、上記第1シートを上記配線基板に取り付ける。

(もっと読む)

半導体装置の検査用アンテナ、検査装置及び検査方法

【課題】ICチップ上にアンテナが一体形成されており、オンウエハ状態での性能検査が可能な検査用アンテナを提供する。

【解決手段】本発明の半導体装置の検査用アンテナ10は、基板11を貫通して配され、該基板の両面を電気的に接続する一対の貫通配線12a、12bと、前記基板の一面側に配され、前記一対の貫通配線の一端部とそれぞれ電気的に接続された一対の第一ランド13a、13bと、前記基板の一面側に配され、前記一対の第一ランドとそれぞれ電気的に接続された一対の第一配線14a、14bと、前記基板の一面側において前記一対の第一配線間に配され、該一対の第一配線と電気的に接続されたコンデンサ15と、前記基板の他面側に配され、前記一対の貫通配線の他端部とそれぞれ電気的に接続された第二ランド17a、17bと、前記基板の他面側に配され、前記一対の第二ランド間を電気的に接続する第二配線18と、を備えたことを特徴とする。

(もっと読む)

ウエハテスト装置

【課題】設置面積を縮小させ、装置が有するケーブルを細くかつ短くすることが可能なウエハテスト装置を提供する。

【解決手段】テスト対象ウエハ13が載置されるステージ12を有する筐体11と、ステージ12上に配置され、複数のピン21を有するプローブカード20と、プローブカード20に接続され、テスト対象ウエハ13をテストするために必要な回路が形成されたテストボード19と、テストボード19が載置されたテストヘッド15と、テストヘッド15を旋回可能に支持するテストヘッド旋回装置16と、を具備するウエハテスト装置であって、前記テストヘッド15にはテスト対象ウエハ13の静特性または動特性をテストする複数のユニット25乃至29が収められるとともに、テストヘッド旋回装置16内には、電源を供給する電源ユニット23および、テストヘッド15を冷却する冷却ユニット22が収められ、ケーブル29により接続されている。

(もっと読む)

集積回路の試験に用いるテストチップ

【課題】対外部装置通信用チャンネル数低減と正確・迅速な試験を、簡略化回路構成で可能とする技術の提供。

【解決手段】被検査体の電気試験のための信号処理回路130と、電気信号の受け渡しをする回路132とを含むテストチップを使用する。信号処理回路130は、外部供給パターン情報を基に、信号を発生するフォーマッタ134と、信号を基に被検査体駆動信号を発生するドライバー136と、被検査体からの応答信号を受けて、被検査体不良信号を受け渡し回路132に出力する比較回路138とを含む。受け渡し回路132は、レイト・ジェネレータ144と、不良セルを特定して、外部に出力するフェイル・キャプチャー・コントロール146と、基準試験周波数信号を基に、タイミング信号を発生するタイミング・ジェネレータ148と、パターン情報を外部から読み出すためのアドレス信号外部に出力するパターン・ジェネレータ150とを備える。

(もっと読む)

半導体装置の試験方法および試験装置

【課題】試験時の電源変動を効率的に抑制することができる。

【解決手段】錘付バイパスコンデンサ部10は、IC211上に自重により載置される。コンデンサ11は、電源側の端子12とGND側の端子13,14と接続される。コンデンサ11は、IC211の電源線に流れる電源電流の高周波成分を端子12から端子13,14へ排流する。端子12,13,14は、錘付バイパスコンデンサ部10を3点で支えると共に、パスコン用パッド213,214と自重により電気的に接続する。

(もっと読む)

プローブカード

【課題】検査体の電気的特性の検査をするためのプローブカードを小型化しつつ、被検査体と接触子との接触を安定させて、検査を適切に行う。

【解決手段】プローブカードの回路基板10の下方且つ支持板12の上方には、複数のプローブに所定の接触圧力を付与する流体チャンバ20が設けられている。流体チャンバ20は、内部に気体が封入され、可撓性を有している。流体チャンバ20の全面外周には、検査時に回路基板10とプローブを電気的に接続する配線30、31が積層されている。配線30、31には、配線30、31の積層方向且つ平面視における流体チャンバ20の径方向に延伸する切り込み部32が形成されている。各配線30、31は、柔軟性を有する絶縁部材40と、絶縁部材40の表面に形成された導電部材41をそれぞれ有している。各絶縁部材40の表面には、複数の導電部材41が形成されている。

(もっと読む)

1 - 20 / 92

[ Back to top ]