Fターム[4M106DJ28]の内容

半導体等の試験・測定 (39,904) | 装置の共通部 (6,103) | 分類手段 (273) | ふりわけ手段 (34)

Fターム[4M106DJ28]の下位に属するFターム

回転筒

Fターム[4M106DJ28]に分類される特許

1 - 20 / 34

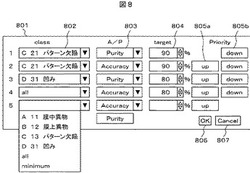

欠陥分類方法及びその装置

【課題】外観検査の欠陥分類において、重要欠陥のピュリティまたはアキュラシーまたはその両方が目標値以上になるように調整するなどのニーズがあるが、教示型の欠陥分類は平均的に分類正解率が高くなるよう条件設定されるため、そのようなニーズに応えられないという問題があった。

【解決手段】特徴量抽出部、欠陥分類部、分類条件設定部を含み、分類条件設定部は、欠陥の特徴量と正解のクラスを対応づけて教示する機能と分類の優先順位を指定する機能を有し、優先順位の高い分類の正解率が高くなるよう条件設定を行う。

(もっと読む)

単結晶シリコンウェーハの評価方法

【課題】加工起因欠陥をより高感度に検出することが可能な単結晶シリコンウェーハの評価方法を提供する。

【解決手段】鏡面加工された単結晶シリコンウェーハ10の表面10aに、SiO2よりもSiのエッチング速度が大きい条件でドライエッチングを施す第1の工程S11と、ドライエッチングされた前記表面に存在するピットの個数を計測する第2の工程S12,S13とを備える。本発明によれば、SiO2よりもSiのエッチング速度が大きい条件でドライエッチングを施していることから、結晶欠陥については突起(凸型の欠陥)として顕在化し、加工起因欠陥についてはピット(凹型の欠陥)として顕在化する。このため、ピットの個数を計測することにより、加工起因欠陥だけを正しく検出することが可能となる。

(もっと読む)

検査装置及び欠陥分類方法

【課題】炭化珪素基板又は炭化珪素基板に形成されたエピタキシャル層に存在する欠陥を検出し、検出された欠陥を分類する検査装置を実現する。

【解決手段】本発明では、微分干渉光学系を含む走査装置を用いて、炭化珪素基板の表面又はエピタキシャル層の表面を走査する。炭化珪素基板からの反射光はリニアイメージセンサ(23)により受光され、その出力信号は信号処理装置(11)に供給する。信号処理装置は、炭化珪素基板表面の微分干渉画像を形成する2次元画像生成手段(32)を有する。基板表面の微分干渉画像は欠陥検出手段(34)に供給されて欠陥が検出される。検出された欠陥の画像は、欠陥分類手段(36)に供給され、欠陥画像の形状及び輝度分布に基づいて欠陥が分類される。欠陥分類手段は、特有の形状を有する欠陥像を識別する第1の分類手段(50)と、点状の低輝度欠陥像や明暗輝度の欠陥像を識別する第2の分類手段(51)とを有する。

(もっと読む)

マルチチャネルデータのグラフィック表現を用いて基板の表面において生じる欠陥を分類するための方法及びシステム

【課題】シリコンウェーハ基板の欠陥検査において、欠陥を分類するための効率的で、信頼性のある方法及びシステムを提供する。

【解決手段】複数のシリコンウェーハからの走査データを解析する方法であり、各ウェーハのグラフィック表現であるウェーハマップに重ねて少なくとも1つの欠陥タイプを指示する複数のデータ点から成る、対応する母集団からのデータ点を表すシンボルを表示する。ここで、プロットされるシンボルは、各ウェーハマップに対応するウェーハ上に存在する少なくとも1つの欠陥タイプのグラフィック描写を与えることができるように、データ点が関連付けられる場所のウェーハマップ上にプロットされる。また、ウェーハマップを積み重ねられて表示され、その積み重ね順序はウェーハの既知の特徴や走査データが得られた処理に予め決められた順序で表示される。

(もっと読む)

半導体チップの組付け方法

【課題】 電気部品に組付けられた半導体チップ間の電気的特性の差を小さくすることのできる半導体チップの組付け方法を実現する。

【解決手段】 パワーMOSFETの寄生ダイオードD1〜D4の順方向電圧VFが近似しているN型MOSFETチップ21,22を特定し、それらをペアにして、半導体ウエハ1の分断後、直接回路基板3に組付ける。また、同様にP型MOSFETチップ61,62を直接回路基板3に組付ける。モータ制御装置のHブリッジ回路を構成する各パワーMOSFETの寄生ダイオードの順方向電圧VFが近似しているため、モータ制御装置をバッテリに逆接続した場合に流れる逆電流がHブリッジ回路の一方に偏るおそれがないので、回路やモータが破壊され難い。

(もっと読む)

半導体用ウエハの評価方法、半導体ウエハの製造方法及び半導体ウエハの製造工程の評価方法

【課題】シリコンウエハ等の半導体用ウエハの電気的特性を適切に評価すること。

【解決手段】ロットPLから任意に選択されたシリコンウエハ1について(S1)、I−V特性を測定し(S2,S3)、測定値6と基準値7とが一致するか否かを判定する(S4)。一致の場合は良品であるから出荷工程に送られる(S6)。不一致の場合は、犠牲酸化膜の成長及びその除去等を行うことにより、シリコンウエハ1に付着した不純物を取り除く。同一ロットPL内の別のシリコンウエハ1について再びI−V測定を行い、測定値6と基準値7とが一致するか否かを判定する。

(もっと読む)

欠陥検査装置、欠陥検査方法、及び半導体装置の製造方法

【課題】 プロセス中で発生した欠陥と、疑似欠陥とを区別することができない。

【解決手段】 プロセスに起因する欠陥と、他の疑似欠陥とを切り分けるための切り分けサイズが、切り分けサイズ記憶部(21)に記憶される。欠陥の情報が、欠陥情報記憶部(17)に記憶される。処理装置が、画像データに基づいて、ウエハ表面上の欠陥を検出し、欠陥の情報を、欠陥情報記憶部に記憶させる。ウエハ表面の欠陥検出を行うべき範囲の全域について欠陥検出処理が終了する前に、一部の範囲について検出された欠陥のサイズと、前記切り分けサイズ記憶部に記憶されている切り分けサイズとを比較し(SB3)、該切り分けサイズ以上の大きさの欠陥が検出されている場合には、前記出力装置から検査装置異常であることを知らせる警報を出力させ(SB5)、該切り分けサイズ以上の大きさの欠陥が検出されていない場合には、未だ欠陥検出処理が行われていない範囲について欠陥検出処理を行う(SB6)。

(もっと読む)

チッピング検出方法

【課題】TEGの存在する分割予定ラインをカーフチェックの対象とした場合であっても、TEGに影響されることなく、正確なチッピング検出を行えるようにする。

【解決手段】TEGが存在する分割予定ラインを切削した場合とTEGが存在しない分割予定ラインを切削した場合との撮像画像上の特性の違いに基づきTEGが存在する分割予定ラインを判定し(ステップS6)、さらに、TEGが存在する分割予定ラインについてはTEG領域抽出工程(ステップS8)によってTEG領域を抽出することで、TEGの存在しない部分のみをチッピング領域として認定するようにした(ステップS7,S9)。

(もっと読む)

半導体欠陥検査装置、および半導体欠陥検査方法

【課題】

電気的評価を行わなくても、最適なプロセス条件を決定することができる半導体欠陥検査装置、および半導体欠陥検査方法を提供する。

【解決手段】

試料を検査して得られる欠陥の種類を記憶したデータベースを参照して、抽出した欠陥の種類を特定し、試料の領域ごとに欠陥の種類別の欠陥密度を求め、表示するようにしたものである。また、試料を検査して得られる欠陥の種類を記憶したデータベースを参照して、抽出した欠陥の種類を特定し、試料の製造プロセスごとに欠陥の種類別の欠陥密度を求め、表示するようにしたものである。

(もっと読む)

欠陥分類装置、欠陥分類方法およびそのコンピュータ・プログラム

【課題】欠陥検査結果から不良発生率を容易に予測することが可能な欠陥分類装置を提供すること。

【解決手段】データベース24には、欠陥検出回数と不良発生率との関係が予め格納される。欠陥同一判定部21は、複数の検査工程に配置された欠陥検査装置によって検出された欠陥が同一欠陥であるか否かを判定して欠陥検出回数を求める。不良発生率導出部22は、データベース24を参照して、欠陥同一判定部21によって求められた欠陥検出回数から不良発生率を導出する。したがって、欠陥検査結果から不良発生率を容易に予測することが可能となる。

(もっと読む)

欠陥検査装置及び欠陥検査方法

【課題】試料表面の撮像画像を検査して試料表面のパターンの欠陥を検出する欠陥検出において疑似欠陥の発生を効果的に抑制する。

【解決手段】試料2の表面に形成されたパターンの欠陥を検出する欠陥検査装置1は、撮像部13により撮像された撮像画像上にて検出された欠陥候補のサイズが撮像部13の結像光学系の解像限界よりも小さく、かつ欠陥候補を示す欠陥候補画素の周囲の画素からこの欠陥候補画素までのグレイレベル値の空間的変化が結像光学系の解像力を超えているとき、この欠陥候補を疑似欠陥として判定する疑似欠陥判定部31を備える。

(もっと読む)

基板分類方法および装置、異常設備推定方法および装置、基板分類方法または異常設備推定方法をコンピュータに実行させるためのプログラム、並びに上記プログラムを記録したコンピュータ読み取り可能な記録媒体

【課題】既知の欠陥分布に関する知識情報に基づいてそれに対応した欠陥分布をもつ基板群を精度良く分類でき、未知の欠陥分布が発生した基板をも自動的に分類できる基板分類方法および基板分類装置を提供すること。

【解決手段】各基板上で欠陥が存在する閉領域を1個以上抽出して、その閉領域を占める欠陥の群を対象欠陥クラスタとして定める(S101)。既知欠陥クラスタに関する知識情報を用意する。S101で得られた複数の対象欠陥クラスタを、既知欠陥クラスタに類似する既知グループと既知欠陥クラスタに類似しない未知グループとに分類する(S102)。基板群を既知グループと未知グループとに分類する(S103)。未知グループに分類された対象欠陥クラスタを複数のサブグループに分類することによって、未知グループに分類された基板群を複数のサブグループに分類する(S105)。

(もっと読む)

半導体集積回路とその検査装置

【課題】配線要素の抵抗を正確に測定することができる半導体集積回路およびその検査装置を提供する。

【解決手段】端子14〜16、41、42を有する半導体パッケージ40と、この半導体パッケージ40に収納され、IOパッド25を有する半導体チップ50からなり、接続要素を用いてIOパッド25を対応する端子に接続する構成の半導体集積回路において、IOパッド25に流れる電流を変化させて、そのときのIOパッド25の電圧と電流を測定することにより、接続要素の抵抗値を正確に測定できるようにした。断線には至らないが、フリップチップバンプの接合不良や微細配線の形成不良を検出することができるので、2次実装時のストレスや長期使用で発生する断線を事前に検出することができる。

(もっと読む)

シリコンウェーハの評価方法およびシリコンウェーハの製造方法

【課題】シリコンウェーハを水銀プローブ法により短時間で評価するための手段を提供すること。

【解決手段】弗酸処理を施したシリコンウェーハ表面と水銀を接触させ、シリコンウェーハと水銀との間に電圧を印加して電気的特性を測定することによりシリコンウェーハを評価する方法。前記測定中、少なくとも、シリコンウェーハの水銀と接触する表面近傍の湿度を50%以上に制御する。

(もっと読む)

異物判定装置および方法

【課題】検査時間を短縮できる異物判定装置および方法を提供すること。

【解決手段】本発明の異物判定装置1は、ウェハ9の検査面91上に載置される基準板4と、基準板4に所定の圧力をかける加圧手段6とを備えている。また、加圧手段6により基準板4に所定の圧力が加えられた状態で、ウェハ9と基準板4との隙間を測定する測定手段7を備えている。さらに、異物判定装置1は、隙間が閾値より小さい場合には、そのウェハ9の検査面91には除去が必要な異物X2は存在しないと判定し、隙間が閾値以上の場合には、そのウェハ9の検査面91には除去が必要な異物X2が存在すると判定する判定手段811を備えている。従って、検査面91に除去が必要な異物X2は存在しないと判定されたウェハ9においては、当該ウェハ9に付着する異物X1,X2の位置の測定および除去を不要にできるので、その分、検査時間を短縮できる。

(もっと読む)

半導体装置の製造方法及びシステム、並びに半導体装置

【課題】ランク分けにて装置を大型化することなく、生産管理が容易で、かつ組み立て不良の発生を防止することができる半導体装置の製造方法及びシステム、並びにこれによって製造された半導体装置を提供する。

【解決手段】ウエハのダイシング後、マウントテープにクリップリングを装着し、個片化された各半導体チップが互いに離間するようにマウントテープを拡張させた状態で、マップデータに基づいてマウントテープ上の半導体チップのうちAランクの半導体チップをダイボンディングする。Aランク品のダイボンティングが終了した複数のマウントリングを、クリップリングを装着したままキャリアマガジンに収容する。そして、Bランク品の組み立て要求に応じて、キャリアマガジンからマウントリングを取り出し、マップデータに基づいて、マウントテープ上の半導体チップのうちBランクの半導体チップをダイボンディングする。

(もっと読む)

欠陥レビュー方法および装置

【課題】検査装置の検出欠陥数の増大に伴い、データ処理/整理に多くの時間を要する。操作性を改良して、使い勝手を向上させ、原因究明の手がかりを早期に探索できる機能を備えた欠陥レビュー方法および装置を提供する。

【解決手段】検査装置とレビュー装置から出力されたデータを処理し、同じ検査条件あるいは検査条件を変えて複数回検査した結果の欠陥マップと、その画像一覧とを並べて表示し、かつ、両者の欠陥をリンクさせ、所望の欠陥が検出できているか、大量の画像データから確認・判定する事が出来る欠陥レビュー方法および装置を提供する。

(もっと読む)

半導体チップの検査方法

【課題】 従来の検査方法では、第1および第2の検査環境で測定した電源電流値が、それぞれ基準値を満たしていても、電源電流値の温度依存性が温度に比例して減少している不良品の半導体チップを検出することができないという問題を有している。

【解決手段】 本発明に係る検査方法では、第1の検査環境下で半導体チップの電気的特性を測定する第1検査工程と、第1検査工程で得られた第1の測定値を記憶装置に記憶する第1測定値記憶工程と、第2の検査環境下で半導体チップの電気的特性を測定する第2検査工程と、第2検査工程で得られた第2の測定値と前記第1の測定値との比が所定の規格値を満たすか否かを判定する測定値比較工程とを有することで、上記課題を解決することができる。

(もっと読む)

デバイスの製造方法

【課題】1工程単独の欠陥数の歩留まりに対する影響を定量的に把握することができる欠陥解析方法を含むデバイスの製造方法を得る。

【解決手段】所定の工程による新規欠陥の有無及び電気テスタによる良否判定をチップ単位に行った後、ウエハ上の複数のチップを(1)新規欠陥なし・良品、(2)新規欠陥なし・不良品、(3)新規欠陥有り・良品、(4)新規欠陥有り・不良品の4種類に分類し、この分類結果に基づき、所定の工程の新規欠陥によってのみ不良となったチップ数と推測される新規不良チップ数、所定の工程の新規欠陥によってチップを不良にした割合と推定される致命率及び所定の工程によって不良となったチップ数と推定される工程不良チップ数を求める。

(もっと読む)

LSI品種決定方法、LSI設計支援方法、LSI品種決定プログラム、LSI設計支援プログラム、記録媒体、LSI品種決定装置およびLSI設計支援装置

【課題】LSIの製造途中において、中間製造物のトランジスタ性能を推定することにより、各中間製造物に合った適切な品種を決定し、LSI製造における歩留まりを向上させる。

【解決手段】ストラクチャードASIC製造時において、トランジスタ層またはトランジスタ層およびメタル1層が形成された中間製造物を製造後、当該中間製造物ごとのトランジスタ速度を測定し、この測定結果とトランジスタ速度に関連付けられた統計データとを用いて、トランジスタ速度の最大遅延推定値を算出する。そして、この算出結果に基づいて、LSIの品種リストの中から、ストラクチャードASICの品種を決定する。

(もっと読む)

1 - 20 / 34

[ Back to top ]