Fターム[4M119AA10]の内容

MRAM・スピンメモリ技術 (17,699) | 目的 (2,141) | 漏れ磁界の低減 (34)

Fターム[4M119AA10]に分類される特許

1 - 20 / 34

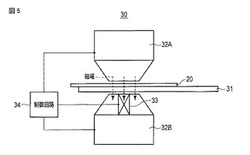

磁気メモリの製造装置

【課題】より小さい磁場で磁性層の磁化方向を所定の方向に設定する。

【解決手段】磁気メモリ21の磁場印加装置30は、磁気メモリ21の磁性層に磁場を印加し、磁性層の磁化方向を初期化する磁石32A及び32Bと、磁性層に磁場が印加されている間に、磁気メモリ21の温度を上昇させる温度上昇機構33と、制御回路34とを含む。磁石32A及び32Bはそれぞれ、設定する磁化方向に応じて、磁場を発生し、磁気メモリ21の上から下へ向かう磁場、又は下から上へ向かう磁場が印加される。

(もっと読む)

磁気メモリの製造装置

【課題】より小さい磁場で磁性層の磁化方向を所定の方向に設定する。

【解決手段】磁気メモリ10の磁場印加装置(製造装置)30は、磁気メモリ10の磁性層15に磁場を印加し、磁性層15の磁化方向を初期化する磁石32A及び32Bと、磁性層15に磁場(反転磁場)が印加されている間に、磁性層15に高周波磁場(マイクロ波磁場)を印加する磁場発生器33と、制御回路34とを含む。磁性層15に磁場を印加すると同時に、高周波磁場を印加することで、小さい反転磁場で磁性層15の磁化方向を所定の方向に設定することができる。

(もっと読む)

磁気記憶素子

【課題】書き込み電流を低減する。

【解決手段】磁気記憶素子10は、膜面に垂直方向の磁気異方性を有し、かつ磁化方向が可変である記憶層12と、記憶層12上に設けられた非磁性層13と、非磁性層13上に設けられ、かつ膜面に垂直方向の磁気異方性を有し、かつ磁化方向が不変である参照層14とを含む。記憶層12の面積は、参照層14の面積より大きく、記憶層12の端部の磁化は、記憶層12の中央部の磁化より小さい。

(もっと読む)

磁気記憶素子

【課題】記憶層に印加される漏れ磁界を低減する。

【解決手段】磁気記憶素子10は、膜面に垂直方向の磁気異方性を有し、かつ磁化方向が可変である記憶層11と、記憶層11上に設けられた非磁性層12と、非磁性層12上に設けられ、かつ膜面に垂直方向の磁気異方性を有し、かつ磁化方向が不変である参照層13と、参照層13上に設けられた非磁性層14と、非磁性層14上に設けられ、かつ参照層13からの漏れ磁界を低減する調整層15とを含む。調整層15は、界面層16と、膜面に垂直方向の磁気異方性を有する磁性層17とが積層されて構成され、界面層16の飽和磁化は、磁性層17の飽和磁化より大きい。

(もっと読む)

磁気抵抗効果素子およびその製造方法

【課題】書き込み電流の低減およびリテンション特性の向上を図る。

【解決手段】磁気抵抗効果素子は、磁化方向が膜面に対して垂直でかつ可変である第1磁性層31と、前記第1磁性層上に形成されたトンネルバリア層32と、前記トンネルバリア層上に形成され、磁化方向が膜面に対して垂直でかつ不変である第2磁性層40と、を具備する。前記第2磁性層は、垂直磁気異方性の起源となる本体層34と、前記トンネルバリア層と前記本体層との間に形成され、前記本体層よりも高い透磁率を有し、前記本体層よりも大きい平面サイズを有する界面層33と、を備える。前記本体層の側面に、前記本体層よりも高い透磁率を有するシールド層90が形成されている。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】記録層に作用する参照層からの漏洩磁界を低減しつつ、トンネルバリア層の絶縁不良を低減する。

【解決手段】実施形態による磁気ランダムアクセスメモリは、膜面に垂直方向の磁気異方性を有し、磁化方向が可変である記録層18と、膜面に垂直方向の磁気異方性を有し、磁化方向が不変である参照層16と、記録層及び参照層間に設けられた第1の非磁性層15と、をそれぞれ具備する複数の磁気抵抗素子10を備え、記録層は、複数の磁気抵抗素子毎に物理的に分離され、参照層及び第1の非磁性層は、複数の磁気抵抗素子を跨いで連続的に延在する。

(もっと読む)

磁気抵抗素子及び磁気メモリ

【課題】微細化に伴って増大する固定層からの漏れ磁場を低減でき、記憶層における磁化の平行と反平行の2つの状態を安定に存在できるようにした磁気抵抗素子を提供する。

【解決手段】磁気抵抗素子1は、固定層2、記憶層3、及び非磁性層4を備える。固定層2は、非磁性層4に接する第1強磁性材料31、第2強磁性材料32、第1強磁性材料31と第2強磁性材料32との間に設けられた第1非磁性材料33を有する。第1強磁性材料31は、Zr、Nb、Mo、Hf、Ta、Wのうちの少なくとも1つの元素と、Coとを含む。

(もっと読む)

磁気抵抗素子及び磁気メモリ

【課題】磁気抵抗素子の微細化に伴って増大する漏洩磁界をキャンセルする。

【解決手段】実施形態に係わる磁気抵抗素子は、垂直及び可変の磁化を持つ記憶層2と、垂直及び不変の磁化を持つ参照層4と、垂直、不変及び参照層3の磁化に対して逆向きの磁化を持つシフト調整層6と、記憶層2及び参照層4間の第1の非磁性層3と、参照層4及びシフト調整層6間の第2の非磁性層5とを備える。参照層4の反転磁界は、記憶層2の反転磁界と同じ又はそれよりも小さく、参照層4の磁気緩和定数は、記憶層2の磁気緩和定数よりも大きい。

(もっと読む)

磁気抵抗効果素子及び磁気メモリ

【課題】記憶層にかかる漏れ磁界を可及的に低減することを可能にする。

【解決手段】膜面に垂直方向の磁気異方性を有する強磁性層10と、強磁性層上に設けられた第1の非磁性層8と、第1の非磁性層上に設けられ、かつ膜面に垂直方向の磁気異方性を有するとともに前記強磁性層の磁化の向きと反平行の磁化を有し、かつ強磁性層の積層方向の膜厚の1/2.8以上1/1.5以下の膜厚を有する参照層6と、参照層上に設けられた第2の非磁性層8と、第2の非磁性層上に設けられ、膜面に垂直方向の磁気異方性を有しスピン偏極した電子の作用により磁化の方向が変化する記憶層2と、を備えている。

(もっと読む)

薄膜磁性体記憶装置

【課題】高集積化に適したメモリセル配置、特に折り返し型ビット線構成に適したメモリセル配置を有する薄膜磁性体記憶装置を提供する。

【解決手段】メモリアレイにおいて、1個のメモリセルMCと対応する繰り返し単位140aが連続的に配置されて、メモリセルMCが行列状に配置される。隣接するメモリセル列間で、繰り返し単位140aは、1/2ピッチ(ハーフピッチ)分だけずらして配置される。ビット線BL1およびBL2は同一のビット線対を構成し、ビット線BL2はデータ読出時において、ビット線BL1の相補線/BL1として動作する。選択されたリードワード線RWLに対応して、1本おきのビット線にメモリセルが接続されるので、セルサイズを増加させることなく折返し型ビット線構成に基づくデータ読出に適したメモリセル配置を実行できる。

(もっと読む)

磁気記録素子および不揮発性記憶装置

【課題】書き込みに必要な電流を低減させることができる磁気記録素子および不揮発性記憶装置を提供する。

【解決手段】実施態様によれば、第1積層部と第2積層部とを備えた磁気記録素子が提供される。第1積層部は、膜面に対して垂直な成分を有する第1の方向に磁化が実質的に固着された第1の強磁性層と、磁化の方向が膜面に対して垂直な方向に可変である第2の強磁性層と、第1、第2の強磁性層の間に設けられた第1の非磁性層と、を含む。第2積層部は、磁化の方向が膜面に対して平行な方向に可変である第3の強磁性層と、膜面に対して垂直な成分を有する第2の方向に磁化が実質的に固着された第4の強磁性層と、第3、第4の強磁性層の間に設けられた第2の非磁性層と、を含む。第1の方向は、第2の方向と逆である。

(もっと読む)

記憶素子、記憶素子の製造方法、及び、メモリ

【課題】消費電力化が可能な記憶素子を提供する。

【解決手段】積層方向に電流を流して、スピン偏極した電子を注入することにより、記憶層16の磁化M1の向きが変化して、記憶層16に対して情報の記憶が行われる記憶素子3を構成する。この記憶素子3は、情報を磁性体の磁化状態により保持する記憶層16と、記憶層16に対してトンネルバリア層15を介して設けられている磁化固定層14とを備える。そして、トンネルバリア層15は、厚さが0.1nm以上0.6nm以下であり、且つ、界面ラフネスが0.5nm未満である。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

磁気記憶装置

【課題】配線に流れる電流によって発生した誘導磁界による磁気記憶素子の誤作動を低減しつつ、大容量化および高集積化を図ることができる磁気記憶装置を提供する。

【解決手段】複数の磁気記憶素子3とビット線4と複数のトランジスタ2と磁気シールド用磁性膜22とを備えている。磁気記憶素子3は、磁化方向が一定である固着層19、磁化方向が可変である記憶層21、および、固着層19と記憶層21との間に配置されたトンネル絶縁膜20を有し、スピン偏極した電子により記憶層21の磁化方向を反転させる。ビット線4は、複数の磁気記憶素子3のそれぞれが互いに間隔を置いて接続され、複数の磁気記憶素子3に対向して配置されている。トランジスタ2は、複数の磁気記憶素子3の内の対応した磁気記憶素子3を経由してビット線4に電気的に接続されている。磁気シールド用磁性膜22は、ビット線4と磁気記憶素子3との間に配置されている。

(もっと読む)

半導体装置

【課題】磁気抵抗素子における磁場の漏洩をより抑制し、性能をより向上することが可能な半導体装置を提供する。

【解決手段】半導体基板は主表面を有する。磁気抵抗素子32は半導体基板の上記主表面上に位置する。配線43は上記磁気抵抗素子32上に位置する。バリア層41a、410は上記配線43の側面および上面を連続するように覆うように配置される。クラッド層41c、41dは上記バリア層41a、410の、配線43に対向する表面と反対側の表面を連続して覆うように配置される。上記磁気抵抗素子32と上記配線43と上記バリア層41a、410と上記クラッド層41c、41dとを含むメモリユニットが複数形成される。複数の上記メモリユニットが配線43の延在する方向に交差する方向に並列しており、複数のメモリユニット間でクラッド層41c、41dが分離されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】磁気抵抗素子における磁場の漏洩をより抑制し、性能をより向上することが可能な半導体装置を提供する。

【解決手段】下部電極31は、半導体基板100の主表面上に形成される。磁気抵抗素子32は、固定層35と、トンネル絶縁膜38と、自由層37とを含む。上部電極44は、自由層37のトンネル絶縁膜38と対向する一方の主表面と反対側に位置する他方の主表面上に配置される。磁気抵抗素子32を構成する固定層35は、下部電極31の一方の主表面上に配置された、磁化の方向が一定である層である。自由層37は、トンネル絶縁膜38の、固定層35と対向する一方の主表面と反対側に位置する他方の主表面上に配置された、磁化の方向が可変である層である。上記下部電極31、固定層35、トンネル絶縁膜38、自由層37、上部電極44の積層方向に交差する方向において、上部電極44の幅は、下部電極31および固定層35の幅よりも小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】書き換え特性の劣化が抑制される半導体装置を提供する。

【解決手段】メモリセル領域RMでは、半導体磁気記憶装置における磁気抵抗素子18は、一方向に延在するディジット線3と、これと略直交する方向に延在するビット線32とが交差する部分に配置される態様で、アレイ状に形成されている。ディジット線3とビット線32は、配線本体となる銅膜3b、31aにクラッド層3a、36aを被覆した配線構造とされる。磁気抵抗素子18の一端側は、非磁性材料から形成されたトップヴィア25aを介してビット線32に電気的に接続されている。

(もっと読む)

半導体集積回路装置および磁気メモリ装置

【課題】正確に書込データを選択メモリセルに書込むことのできる磁気メモリ装置を提供する。

【解決手段】メモリセルに書込み電流を伝達する書込電流線(BL0、BL1)と平行にかつ異なる配線層に、制御信号を転送する分割構造の制御信号線(210l、211a

、211b)を配置する。電流ドライブ回路が各書込み電流線に対応して配置されて、制御信号線上の制御信号と書込データとに従って対応の書込電流線に電流を流す。

(もっと読む)

磁気トラック、磁気トラックを備える情報保存装置及び該情報保存装置の動作方法

【課題】磁気トラック、磁気トラックを備える情報保存装置及び該情報保存装置の動作方法を提供する。

【解決手段】開示された磁気トラックは相異なる長さの第1及び第2磁区領域を備える。該第1及び第2磁区領域で磁壁移動速度は相異なりうる。該第1及び第2磁区領域のうち長さの長い領域は、情報の記録/再生領域でありうる。第1磁区領域での磁壁移動速度は、第2磁区領域での磁壁移動速度より速い。第1磁区領域の長さl1、前記第2磁区領域の長さl2、第1磁区領域での磁壁移動速度V1及び第2磁区領域での磁壁移動速度V2は、V1=(l1/l2)×V2を満たす。

(もっと読む)

磁気メモリ

【課題】記録層に作用する参照層からの漏洩磁界を低減する。

【解決手段】磁気メモリは、膜面に垂直方向の磁気異方性を有しかつ磁化方向が可変である第1の磁性層12と、膜面に垂直方向の磁気異方性を有しかつ磁化方向が不変である第2の磁性層14と、第1の磁性層12及び第2の磁性層14に挟まれた非磁性層13とを有する磁気抵抗素子10と、第2の磁性層14と平行な磁化を有し、かつ磁気抵抗素子10を囲むバイアス磁界層16とを含む。

(もっと読む)

1 - 20 / 34

[ Back to top ]