Fターム[4M119AA13]の内容

MRAM・スピンメモリ技術 (17,699) | 目的 (2,141) | クロストーク防止 (15)

Fターム[4M119AA13]に分類される特許

1 - 15 / 15

3次元半導体装置

【課題】増加された集積度を有し且つ高密度で高速の3次元(抵抗性)半導体(メモリ)装置を、最小限のマスク工程数で提供する。

【解決手段】チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時,前記選択ラインは平面形状及び平面位置において、前記水平電極の各々と実質的に同一であり得る。

(もっと読む)

半導体素子及びその形成方法

【課題】ビットラインを容易に形成することができ、ビットライン工程マージンを増加させ、さらに隣接したビットライン間のキャパシタンスを減少させる半導体素子及びその形成方法を提供する。

【解決手段】本発明に係る半導体素子は、半導体基板10で一方向に延長され、垂直チャンネル領域12b,14bを含む第1及び第2ピラー12,14と、第1及び第2ピラー12,14の内部で垂直チャンネル領域12b,14bの下部に位置する第1ビットライン22と、第1ビットライン22を含む第1ピラー12及び第2ピラー14の間に位置する絶縁膜32とを含む。

(もっと読む)

磁気メモリ及びその製造方法

【課題】磁気抵抗素子間での電気的特性のバラツキを低減する。

【解決手段】磁気メモリの製造方法は、半導体基板20上のセルアレイ部に磁気抵抗素子37を形成する工程と、半導体基板20上の周辺回路部に、磁気抵抗素子37と同じ積層構造を有しかつ磁気抵抗素子37と同じレベルに配置されたダミー素子68を形成する工程と、磁気抵抗素子37及びダミー素子68を一括して平坦化する工程と、ダミー素子68にレーザー光線を照射し、ダミー素子68を非磁性体化する工程と、平坦化された磁気抵抗素子37上に上部電極41を形成する工程とを含む。

(もっと読む)

磁気記憶装置

【課題】集積度が高い磁気記憶装置を提供する。

【解決手段】実施形態に係る磁気記憶装置は、基板と、前記基板上に設けられた複数個の磁気抵抗効果素子と、を備える。そして、前記複数個の磁気抵抗効果素子のうち、上方から見て互いに最も近い位置にある2個の磁気抵抗効果素子は、前記基板からの距離が相互に異なる。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

パンチスルーアクセスを有する縦型不揮発性スイッチおよびその製造方法

不揮発性メモリセルにアクセスするための半導体装置が提供される。いくつかの実施形態においては、半導体装置は、ソース、ドレインおよびウェルを含む半導体層の縦型スタックを有する。半導体装置へのドレイン−ソースバイアス電圧の印加は、ウェルにわたってパンチスルー機構を生成し、ソースとドレインとの間の電流の流れを発生させる。  (もっと読む)

(もっと読む)

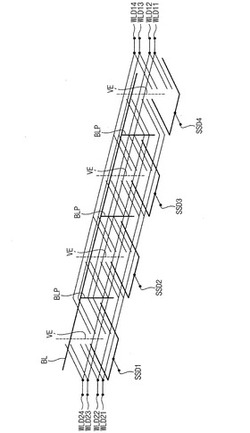

3次元垂直チャンネル構造を有する不揮発性メモリ装置のプログラム方法

【課題】本発明は、ビットラインとストリング選択ラインとの交差領域に各々形成され、各々が基板上に垂直に多層構造で形成されたメモリセルを有するストリングを含む不揮発性メモリ装置のプログラム方法を提供する。

【解決手段】本発明のプログラム方法によると、シャドープログラム方式によってYZ平面の各層に属したメモリセルがマルチビットデータにプログラムされ、YZ平面のN番目の層(ここで、Nは1、またはそれより大きい定数)のメモリセルがプログラムされる場合、YZ平面の他層のメモリセルがプログラムされる前にN番目の層に対応するXZ平面の残りのメモリセルがプログラムされる。

(もっと読む)

半導体集積回路装置および磁気メモリ装置

【課題】正確に書込データを選択メモリセルに書込むことのできる磁気メモリ装置を提供する。

【解決手段】メモリセルに書込み電流を伝達する書込電流線(BL0、BL1)と平行にかつ異なる配線層に、制御信号を転送する分割構造の制御信号線(210l、211a

、211b)を配置する。電流ドライブ回路が各書込み電流線に対応して配置されて、制御信号線上の制御信号と書込データとに従って対応の書込電流線に電流を流す。

(もっと読む)

スピントランスファートルク−磁気トンネル接合デバイスおよび動作方法

磁気メモリデバイスのソース線またはビット線を介して送られる電流に関する電流の流れ方向を制御するステップを含む方法が開示される。電流で生ずる磁場は、STT−MTJ(スピントランスファートルク磁気トンネル接合)デバイス内の磁気素子の自由層の磁場方向を切り換えることを助ける。  (もっと読む)

(もっと読む)

磁気ランダムアクセスメモリ及びその書き込み方法

【課題】セルの高集積化を図ることが可能な磁気ランダムアクセスメモリ及びその書き込み方法を提供する。

【解決手段】磁気ランダムアクセスメモリは、第1の方向に延在された第1の配線BLと、第1の方向と交差する第2の方向に延在された第2の配線WLと、第1及び第2の配線間の第1及び第2の配線の交点に配置され、第1の配線に接続された一端を有し、固定層と記録層と固定層及び記録層の間に設けられた非磁性層とを有し、固定層の膜厚は記録層の膜厚よりも厚く、固定層の幅は記録層の幅より広く、固定層及び記録層の間に第1の電流を流すことで記録層の磁化方向が反転する磁気抵抗効果素子MTJと、磁気抵抗効果素子の他端に接続された一端と第2の配線に接続された他端とを有し、第1の電流を一方向のみに流すダイオードDとを具備する。

(もっと読む)

トンネル電界効果トランジスタを用いたメモリ

【課題】抵抗メモリの一種として挙げられ、抵抗記憶素子に相変化材料を用いた相変化メモリを提供する。

【解決手段】メモリは、第1ドレイン124と第1ソース122aとを含む第1トンネル電界効果トランジスタ108aを含んでいる。上記第1ドレインは、第1抵抗記憶素子106aに結合されている。上記メモリは、第2トンネル電界効果トランジスタ108bを含んでいる。上記第2トンネル電界効果トランジスタは、第2ドレインを含み、上記第1ソース122aを共有している。上記第2ドレインは、第2抵抗記憶素子に結合されている。上記メモリは、ソースノードを設けるために、上記第1ソースに結合されている第1領域114を含む。

(もっと読む)

金属/半導体/金属の積層構造を有する双方向ショットキーダイオード及びその形成方法

【課題】 金属/半導体/金属の積層構造の双方向ショットキーダイオードの形成方法を提供する。

【解決手段】 下部電極104と上部電極114との間に挟持されるシリコン半導体層110を堆積する工程と、閾値電圧、降伏電圧、及び、オン/オフ電流比を有する双方向ショットキーダイオードを形成する工程と、双方向ショットキーダイオードの閾値電圧、降伏電圧、オン/オフ電流比をシリコン半導体層の膜厚112の制御によって調整する工程と、を備える。閾値電圧と降伏電圧は何れもシリコン半導体層の膜厚の増加に従って増加する。オン/オフ電流比に対してシリコン半導体層の最適膜厚が存在する。化学気相成長法またはDCスパッタリング法を用いて非晶質シリコンまたは多結晶シリコンの半導体層を形成する。シリコン半導体層はV族のドナー材料でドーピングできる。当該ドーピングによって閾値電圧は減少し、降伏電圧は増加する。

(もっと読む)

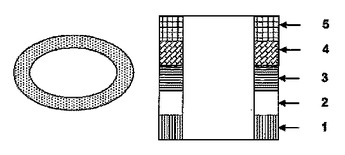

金属芯を含む又は含まない閉鎖形状磁性多層膜、その製造方法及び用途

本発明は、磁性多層膜、その製造方法及び磁性メモリにおける応用に関するものであり、当該磁性多層膜の各層が閉鎖の円環形または楕円環形であり、その磁性セルには、強磁性を有する薄膜層の磁気モーメントまたは磁束が、時計方向または反時計方向の閉鎖状態に形成される。本発明は、また前記の閉鎖形状磁性多層膜の幾何中心位置に1つの金属芯が設けられる磁性多層膜に関するものであり、当該金属芯の横断面が対応的に円形または楕円形状である。本発明は、さらに前記閉鎖の、金属芯を含む(または含まない)磁性多層膜により製造される磁性メモリ。本発明は、微細加工方法によって前記閉鎖形状磁性多層膜を製造する。本発明に係る閉鎖の、金属芯を含む(または含まない)形状の磁性多層膜は、磁気ランダムアクセスメモリ、コンピュータ磁気読み出しヘッド、磁気センサー、磁気論理デバイス、スピントランジスタなどのような磁性多層膜を核とする各種のデバイスに広く用いられる。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】読出し電流と参照電流との間のマージンを十分な大きさに保つことができ大きな読出し速度を維持することができる。

【解決手段】メモリセルアレイMCAは、複数のワード線WLsと複数のビット線BLsの交点に設けられる複数のメモリセルMCを含んでいる。メモリセルMCの制御ゲートはワード線WLに接続され、メモリセルMCのドレインはビット線BLに接続されている。浮遊ゲートに電子が注入され閾値電圧が高くなった状態が“0”データ、逆に低い状態が“1”データとされる。“1”データの場合には、ビット線BLに電流が流れる。カラムゲート340は、カラムデコーダからのカラムアドレス信号に基づき複数のビット線BLsを同時にデータ線DLsに接続するためのものである。また、カラムゲート340は、複数のビット線BLsのうち隣接するビット線同士を、それぞれ複数のデータ線DLsのうち互いに隣接していないデータ線に接続する。

(もっと読む)

クロスポイント型抵抗メモリアレイの製造方法、及びクロスポイント型抵抗メモリアレイ積載体の製造方法

【課題】各抵抗メモリが完全に絶縁され、かつ自己整合するクロスポイント型抵抗メモリアレイを実現する。

【解決手段】本発明は、第1シリコン基板に第1P+層および第1N+埋込層を形成する工程34と、第1下部電極、犠牲材料層、第1ハードマスクを堆積する工程40と、第1ハードマスクを、第1パターンにパターンニングし、第1ハードマスク、犠牲材料層及び第1下部電極をエッチングし、第1N+埋込層をオーバーエッチングする工程48と、第1絶縁層を堆積する工程50と、第1ハードマスクを、第2パターンになるようにパターニングし、第1ハードマスク、第1絶縁層、犠牲材料層、第1下部電極、及び第1N+埋込層をエッチングし、第1シリコン基板をオーバーエッチングする工程56と、第2絶縁層を堆積する工程58と、残存第1ハードマスク及び犠牲材料層をエッチングする工程と、第1抵抗材料層を堆積する工程と、第1上部電極を堆積しエッチングする工程とを含む。

(もっと読む)

1 - 15 / 15

[ Back to top ]