Fターム[4M119DD45]の内容

MRAM・スピンメモリ技術 (17,699) | セル構成 (5,615) | アーキテクチャ (1,063) | Tr+記憶素子方式 (867) | 1Tr+1記憶素子でセル、ユニット (716)

Fターム[4M119DD45]に分類される特許

161 - 180 / 716

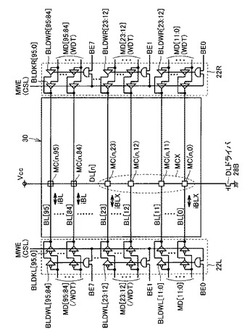

半導体装置

【課題】メモリ素子の信頼性と消費電流の抑制を両立させることができる半導体装置を提供する。

【解決手段】半導体装置は、複数の磁気メモリセルMCと、複数のディジット線DLと、ディジット線ドライブ回路28Bと、ビット線BL[0:95」とを備える。複数のビット線BL[0:95」は、たとえば12本ごとの複数の群に分割される。半導体装置は、複数のビット線の各々を少なくとも2段階の強度で駆動可能に構成されたビット線ドライブ回路22L,22Rとをさらに備える。ビット線ドライブ回路22L,22Rは、書込群に対しては、書込データに対応する極性の電流で2段階のうち強い強度でビット線を駆動し、非書込群に対しては、2段階のうち弱い強度で自分自身のデータに対応する極性のデータ保持電流を流す。

(もっと読む)

磁気抵抗効果素子、磁気メモリ、磁気抵抗効果ヘッド、および磁気記録再生装置

【課題】MR変化率の向上が図れる磁気抵抗素子、磁気メモリ、磁気ヘッド、及び磁気記録再生装置を提供する。

【解決手段】磁化方向が実質的に一方向に固着された第1の磁性層と、外部磁界に応じて磁化方向が変化する第2の磁性層と、上記第1の磁性層と前記第2の磁性層との間に設けられたスペーサ層とを有し、上記第1の磁性層と前記第2の磁性層の少なくともいずれかは、式M1a M2bXc (5≦a≦68、10≦b≦73、22≦c≦85)で表される磁性化合物を有し、M1は、Co,Fe,Niから選択される少なくとも一種の元素、M2は、Ti,V,Cr,Mnから選択される少なくとも一種の元素、Xは、N,O,Cから選択される少なくとも一種の元素である。

(もっと読む)

不揮発性メモリ素子及びその製造方法

【課題】リードディスターブ現象の発生を抑制し得る不揮発性メモリ素子を提供する。

【解決手段】本発明の不揮発性メモリ素子は、第1電極51、正のペルチェ係数を有する第1材料層53、情報記憶層60、負のペルチェ係数を有する第2材料層54、及び、第2電極52が積層されて成る。第1材料層53はp型熱電材料から成り、第2材料層54はn型熱電材料から成ることが好ましい。

(もっと読む)

薄膜磁性体記憶装置

【課題】高集積化に適したメモリセル配置、特に折り返し型ビット線構成に適したメモリセル配置を有する薄膜磁性体記憶装置を提供する。

【解決手段】メモリアレイにおいて、1個のメモリセルMCと対応する繰り返し単位140aが連続的に配置されて、メモリセルMCが行列状に配置される。隣接するメモリセル列間で、繰り返し単位140aは、1/2ピッチ(ハーフピッチ)分だけずらして配置される。ビット線BL1およびBL2は同一のビット線対を構成し、ビット線BL2はデータ読出時において、ビット線BL1の相補線/BL1として動作する。選択されたリードワード線RWLに対応して、1本おきのビット線にメモリセルが接続されるので、セルサイズを増加させることなく折返し型ビット線構成に基づくデータ読出に適したメモリセル配置を実行できる。

(もっと読む)

記憶素子、メモリ装置

【課題】書込電流を増大させることなく、熱安定性を改善することができる記憶素子の提供。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層17と、記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層15と、記憶層と磁化固定層の間に設けられる非磁性体による絶縁層16とを有する。そして積層方向にスピン偏極した電子を注入することにより、記憶層の磁化の向きが変化して情報の記録が行われる。ここで記憶層が受ける実効的な反磁界の大きさが、記憶層の飽和磁化量よりも小さいものとされている。

(もっと読む)

縦型トランジスタSTRAMアレイ

【課題】複数の不揮発性可変抵抗メモリセルを含む縦型のメモリアレイを提供する。

【解決手段】方法は、半導体ウェハから垂直に伸延する複数のピラー構造を有する半導体ウェハを提供するステップを含む。導電相互接続素子が、少なくとも選択された縦型ピラートランジスタ上に堆積されるとともに、不揮発性可変抵抗メモリセルが、導電相互接続素子上に堆積されて、縦型トランジスタメモリアレイを形成する。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】不揮発性記憶装置およびその製造方法に関し、抵抗変化材料を利用したメモリの信頼性の向上を実現する。

【解決手段】積半導体素子を形成する基板の上方に、第1方向に延伸するように複数の金属配線層2を設け、金属配線層2のさら上方に、前記第1方向に直交する第2方向に延伸するように複数の金属配線層3を設ける。また、金属配線層2と金属配線層3とが交差する空間のそれぞれにメモリセルを設ける。前記メモリセルは、選択素子と相変化材料層7とが並列接続された構成とする。ここで、前記選択素子の前記第1方向の寸法が、相変化材料層7の前記第1方向の寸法よりも大きくなるように加工する。

(もっと読む)

半導体装置

【課題】正常な書込動作が実現できるセグメント書込み手法を用いた半導体装置を提供する。

【解決手段】第1および第2DLドライバ12a,12bは、それぞれ選択された1つのブロックのディジット線に磁化電流を流す。BLドライバ6は、データ信号の論理に応じた方向の書込電流を選択されたセグメント内の全ビット線に流して、選択されたブロックのメモリセルにデータ信号を書込む。セグメントデコーダ14は、外部から1個のセグメントのアドレスが入力されたときに、アドレスに対応する1個のセグメントを選択し、選択したセグメント第1DLドライバ12aへ接続し、外部から2個以上のセグメントのアドレスが入力されたときに、アドレスに対応する2個以上のセグメントを選択し、選択した2個のセグメントをそれぞれ第1DLドライバ12aと第2DLドライバ12bへ接続する。

(もっと読む)

記憶素子及びメモリ

【課題】スピン注入効率を改善することにより、情報の記録に要する電流を低減することができる記憶素子を提供する。

【解決手段】情報を磁性体の磁化状態により保持する記憶層17を有し、この記憶層17に対して中間層16を介して磁化固定層19が設けられ、積層方向に電流を流すことにより、記憶層17の磁化の向きが変化して、記憶層17に対して情報の記録が行われる記憶素子10において、記憶層17を構成する磁性体のダンピング定数αが、α<0.015を満足する構成とする。

(もっと読む)

薄膜磁性体記憶装置

【課題】製造時ばらつきに対応して、データ読出時における高い信号マージンを確保可能な薄膜磁性体記憶装置を提供する。

【解決手段】ダミーメモリセルDCPは、2個のセルユニットCU0およびCU1を含む。各セルユニットCU0,CU1は、メモリセルと同様の構成を有し、ビット線BLと接地電圧Vssとの間に直列に結合された、トンネル磁気抵抗素子TMRおよびアクセストランジスタATRを有する。セルユニットCU0,CU1に対しては、異なる記憶データ“0”および“1”がそれぞれ書込まれる。データ読出時において、2個のセルユニットCU0,CU1が、読出参照電圧Vrefを伝達するためのビット線BLと接地電圧Vssとの間に並列に接続される。さらに、ダミーメモリセルDCPに対して、電流供給回路52からメモリセルに供給されるセンス電流Isの2倍、すなわち2・Isの一定電流が供給される。

(もっと読む)

磁気記録素子

【課題】磁化反転のバラツキを小さくすること、あるいは高速化すること、あるいは反転電流を低減させること、ができる磁気記録素子を提供する。

【解決手段】磁化が第1の方向に実質的に固定された第1の強磁性層10aと、磁化の方向が可変の第2の強磁性層30と、前記第1の強磁性層と前記第2の強磁性層との間に設けられた第1の非磁性層20と、磁化の方向が可変の第3の強磁性層50と、前記第1の強磁性層と前記第3の強磁性層との間に設けられた第2の非磁性層40aと、を積層し、各層の膜面に対して垂直な方向に流れる電流が前記第1の強磁性層を流れることによりスピン偏極した電子が生じ、且つ前記スピン偏極した電子により前記第3の強磁性層の磁化が歳差運動し、前記歳差運動により発生する磁場を前記第2の強磁性層に作用させることにより、前記第2の強磁性層の磁化の方向を前記電流の向きに応じた方向に決定する。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMを構成する上部の導電要素と下部の導電要素との短絡を抑制することが可能な半導体装置、およびその製造方法を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に位置する、ピン層MPLと、トンネル絶縁層MTLと、フリー層MFLとを含む磁気トンネル接合構造MRDと、磁気トンネル接合構造MRDの下側側面に接する下側絶縁層III1と、下側絶縁層III1上に位置して磁気トンネル接合構造MRDの上側側面に接し、かつ磁気トンネル接合構造MRDの上面を露出する側壁絶縁層III2と、側壁絶縁層III2から露出する磁気トンネル接合構造MRDの上面に接する導電層BLとを備えている。

(もっと読む)

磁気抵抗素子及び磁気ランダムアクセスメモリ

【課題】熱擾乱耐性が大きく、低電流でスピン注入磁化反転書き込みが可能な磁気抵抗素子を提供する。

【解決手段】実施形態は、Mo、Nb、Wのいずれかを有する金属層を備えた電極層と、金属層上に前記金属層と接するように配置され、膜面垂直方向に磁化容易軸を有し、磁化方向が可変の記憶層3と、記憶層3上に配置され、膜面垂直方向に磁化容易軸を有し、磁化方向が不変の参照層2と、記憶層3と参照層2との間に設けられた第1非磁性層4とを備える。記憶層3の磁化方向は、記憶層3、第1非磁性層4、及び参照層2を貫く電流により可変とされる。

(もっと読む)

半導体記憶装置

【課題】 チップ面積を増加することなく、フューズセルを実現する。

【解決手段】 実施形態による半導体記憶装置は、第1セルアレイ10−1内に配置された第1参照セルRCと、第1セルアレイ10−1内に配置され、第1参照セルRCが配置されたロウ又はカラムと同一のロウ又はカラムに並べられた複数の第1フューズセルFCと、を具備する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】上部電極と下部電極との間の短絡、あるいは、上部電極と配線との接触不良を抑制しながら、MTJ素子を微細化することができる半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板の表面上に形成された選択素子を備えている。下部電極は、選択素子に接続されている。磁気トンネル接合素子は、下部電極上に設けられている。上部電極は、磁気トンネル接合素子上に設けられている。成長層は、上部電極上に設けられ、導電性材料からなり、半導体基板の表面上方から見たときに上部電極よりも面積が大きい。配線は、成長層上に設けられている。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 セルの微細化を図る。

【解決手段】 実施形態による磁気ランダムアクセスメモリは、半導体基板1上に形成された選択素子Trと、選択素子上に形成された多層配線層7a−cと、多層配線層上に形成された層間絶縁膜8と、層間絶縁膜内に形成され、多層配線層を介して選択素子と電気的に接続されたコンタクト層9と、コンタクト層と電気的に接続され、金属材で形成された下部電極層21と、下部電極層の側面を取り囲み、金属材の酸化物で形成された金属酸化絶縁膜26と、下部電極層上に形成された磁気抵抗素子10と、磁気抵抗素子上に形成された上部電極層23と、磁気抵抗素子及び上部電極層の側面上に形成された側壁絶縁膜25と、上部電極層と電気的に接続されたビット線29と、を具備する。

(もっと読む)

半導体装置

【課題】電源電圧の変動に起因した書込電流の変動を抑制する。

【解決手段】ドライブ回路25において、第1のMOSトランジスタPMは、第1および第2の電源ノード28,29間にデータ書込線DLと直列に設けられる。第2のMOSトランジスタPSは、第1のMOSトランジスタPMと並列に設けられる。第3および第4のMOSトランジスタPa,Pbは、互いに同じ電流電圧特性を有する。第1の素子Eaは、第1および第2の電源ノード28,29間に第3のMOSトランジスタPaと直列に接続される。第2の素子Ebは、第1および第2の電源ノード28,29間に第4のMOSトランジスタPbと直列に接続され、第1の素子Eaの電流電圧特性曲線と交差する電流電圧特性を有する。比較器30は、第1の素子Eaにかかる電圧と第2の素子Ebにかかる電圧とを比較し、比較結果に応じて第2のMOSトランジスタPSをオンまたはオフにする。

(もっと読む)

記憶素子、メモリ装置

【課題】書込電流の減少と熱安定性を改善できる記憶素子の提供。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層17と、記憶層17の上下に配される絶縁層16U、16Lと、さらに膜面に垂直な磁化を有する上下の磁化固定層15U、15Lを備えたデュアル構造とする。そして積層方向にスピン偏極した電子を注入することにより、記憶層の磁化の向きが変化して情報の記録が行われる。ここで記憶層が受ける実効的な反磁界の大きさが、記憶層の飽和磁化量よりも小さいものとされている。さらに2つの磁化固定層のそれぞれの膜面に垂直な磁化方向は逆方向とされている。また素子全体の面積抵抗値が10Ωμm2以上、40Ωμm2以下であり、上側の絶縁層の面積抵抗値は、下側の絶縁層の面積抵抗値より高くする。

(もっと読む)

磁気抵抗効果素子、磁気メモリ及び磁気抵抗効果素子の製造方法

【課題】磁気抵抗効果素子の素子特性の向上を図る。

【解決手段】本実施形態の磁気抵抗効果素子は、膜面に対して垂直方向の磁気異方性を有し、磁化の向きが不変な第2の磁性層92と、膜面に対して垂直方向の磁気異方性を有し、磁化の向きが可変な第1の磁性層91と、第1及び第2の磁性層91,92との間に設けられた非磁性層93と、を具備し、第1の磁性層92は、Tb、Gd及びDyからなる第1のグループから選択される少なくとも1つの元素とCo及びFeからなる第2のグループから選択される少なくとも1つの元素とを含む磁化膜21を備え、磁化膜21は、アモルファス相29と粒径が1nm以下の結晶28とを含む。

(もっと読む)

記憶素子、メモリ装置

【課題】垂直磁気異方性を強化し、書込電流を増大させることなく、熱安定性を改善することができる記憶素子の提供。

【解決手段】記憶素子3は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層17と、記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層15と、記憶層と磁化固定層の間に設けられる非磁性体による絶縁層16とを有する。上記記憶層は、Co−Fe−B層と1a族、2a族、3a族、5a族又は6族の何れかに属する元素との積層構造からなり、上記Co−Fe−B層1nmに対して上記元素を0.05nm〜0.3nmの薄膜として挿入するものであり、上記記憶層、上記絶縁層、上記磁化固定層を有する層構造の積層方向にスピン偏極した電子を注入することにより、上記記憶層に対して情報の記録が行われるとともに、上記記憶層が受ける、実効的な反磁界の大きさが、上記記憶層の飽和磁化量よりも小さい。

(もっと読む)

161 - 180 / 716

[ Back to top ]