Fターム[4M119DD60]の内容

MRAM・スピンメモリ技術 (17,699) | セル構成 (5,615) | その他のセル構成に関する技術 (22)

Fターム[4M119DD60]に分類される特許

1 - 20 / 22

3次元半導体装置

【課題】増加された集積度を有し且つ高密度で高速の3次元(抵抗性)半導体(メモリ)装置を、最小限のマスク工程数で提供する。

【解決手段】チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時,前記選択ラインは平面形状及び平面位置において、前記水平電極の各々と実質的に同一であり得る。

(もっと読む)

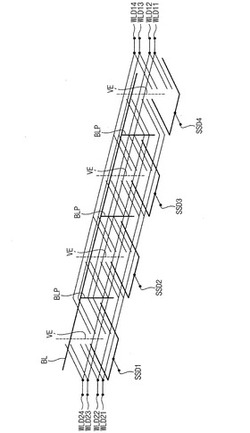

半導体記憶装置およびその製造方法

【課題】ビット当たりの単価を低減できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、第1方向に沿う第1部分(11a)と第2方向に沿いかつ第1部分と接続された第2部分(11b)とを有し、第2部分において半導体材料を含み、第1方向および第2方向からなる第1平面と交わる方向に沿って離れて並ぶ少なくとも2つの第1配線(11)を含む。可変抵抗膜(15)は、第1配線の第2部分に接続された第1面を有し、相違する抵抗値を示す複数の状態を取り得る。第2配線(12)は、可変抵抗膜の第1面と対向する第2面と接続されている。制御線(13)は、第1平面と交わる方向に沿い、少なくとも2つの第1配線の第2部分の半導体材料を含む部分と絶縁膜を介して接し、第1配線の第2部分の半導体材料を含む部分および絶縁膜とともにトランジスタを構成する。

(もっと読む)

半導体記憶装置

【課題】4個のトランジスタと2個のMTJ素子からなり、電源を印加しないでも不揮発性メモリとして動作するSRAMからなる半導体記憶装置を提供する。

【解決手段】第1及び第2のインバータ2,4と第1及び第2の転送用MOSFET3,5とを含むメモリセル1からなるSRAMにおいて、第1及び第2のインバータ2,4はスピン注入型のMTJ素子6,8と駆動用MOSFET7,9とからなり、これらのインバータ2,4からフリップフロップ回路が構成され、第1及び第2のインバータ2,4の出力端子は、それぞれ第1及び第2の転送用MOSFET3,5を介してビットライン及びビットラインバーに接続され、第1及び第2の転送用MOSFET3,5のゲートは、同一のワードラインに接続される。従来のSRAMに比較してメモリセルの面積が小さく、高速で低消費電力の不揮発性メモリが得られる。

(もっと読む)

磁気記録素子及び磁気メモリ

【課題】磁気記録素子のMR比の向上を図る。

【解決手段】実施形態に係わる磁気記録素子は、磁化が可変で磁化容易軸方向が膜面に垂直となる方向の磁気記録層11と、磁化が膜面に垂直となる方向に固定される磁気固着層12と、磁気記録層11と磁気固着層12との間の非磁性バリア層13と、磁気記録層11と非磁性バリア層13との間の挿入層14とを備える。挿入層14は、軟磁性材料、ホイスラー合金、ハーフメタル酸化物、及び、ハーフメタル窒化物のうちの1つを含む。

(もっと読む)

スピンMOSFETを用いたメモリ回路、メモリ機能付きパストランジスタ回路、スイッチングボックス回路、スイッチングブロック回路、およびフィールドプログラマブルゲートアレイ

【課題】高速、不揮発性、低消費電力のメモリ回路を提供する。

【解決手段】一方のソース/ドレインがノード40に接続された第1導電型スピンMOSFET10と、一方のソース/ドレインがノード40に接続された第1導電型スピンMOSFETもしくは第1導電型のMOSFET12と、ノード40にゲート電極が接続され一方のソース/ドレイン電極が出力端子37に接続されたpチャネルスピンMOSFETもしくはpチャネルのMOSFET14と、ノード40にゲート電極が接続され、一方のソース/ドレイン電極が出力端子37に接続されたnチャネルスピンMOSFETもしくはnチャネルのMOSFET16と、出力端子37と、を備え、第3トランジスタ14と第4トランジスタ16はインバータ回路を構成し、第3トランジスタ14および第4トランジスタ16の少なくとも一方がスピンMOSFETであり、出力端子37からインバータ回路が出力される。

(もっと読む)

磁壁移動素子及びその製造方法

【課題】磁壁移動素子の微細化を促進すること。

【解決手段】磁壁移動素子は、磁気記録層を備える。磁気記録層は、第1磁化固定領域と、第2磁化固定領域と、第1磁化固定領域と第2磁化固定領域との間に挟まれた磁化自由領域と、を含む。磁壁移動素子は更に、第1構造体、第2構造体、及び磁気トンネル接合を備える。第1構造体は、第1磁化固定領域と磁気的に結合し第1磁化固定領域の磁化方向を固定する第1磁性体を備える。第2構造体は、第2磁化固定領域と磁気的に結合し第2磁化固定領域の磁化方向を固定する第2磁性体を備える。磁気トンネル接合は、第1構造体と第2構造体とによって挟まれ、第1構造体及び第2構造体に接触し、磁化自由領域の少なくとも一部を備える。

(もっと読む)

磁気ランダムアクセスメモリ及びその初期化方法

【課題】下層のハード層の面内ばらつきに影響されず初期化可能なMRAMを提供する。

【解決手段】MRAMは、強磁性の磁気記録層10と、磁化が固定された強磁性の磁化固定層30と、磁気記録層10と磁化固定層30との間に設けられた非磁性のスペーサ層20と磁気記録層10の両端部の上部又は下部に設けられた導電層14a、14bとを具備する。磁気記録層10は、磁化が反転可能であり、スペーサ層20を介して磁化固定層30に接合される磁化反転領域13と、第1方向の磁化を有し、磁化反転領域13と平行に設けられた第1磁化領域11aと、第2方向の磁化を有し、磁化反転領域13と平行に設けられた第2磁化領域11bと、磁化反転領域13及び第1磁化領域11aと所定の傾斜角度φを成して結合する第1傾斜領域12aと、磁化反転領域13及び第2磁化領域11bと傾斜角度φを成して結合する第2傾斜領域12bとを備える。

(もっと読む)

抵抗変化メモリ

【課題】高い抵抗値の抵抗素子を実現する。

【解決手段】本実施形態の抵抗変化メモリは、第1の配線レベルILV1に位置し、第1の方向に延びる制御線L1と、第2の配線レベルILV2に位置し、第2の方向に延びる制御線L2と、制御線L1と制御線L2との間に設けられるセルユニットCUとを含むメモリセルアレイを有し、複数の配線レベルに設けられる少なくとも2つの抵抗線RL3A,RL5と、抵抗線RL3A,RL5間に設けられ、セルユニットCUの構成部材又はコンタクトプラグZCの構成部材と同じ構成部材を含む抵抗体91と、を有し、抵抗素子領域17内に設けられる抵抗素子90を含んでいる。

(もっと読む)

磁気メモリ

【課題】書き込み電流を低減する。

【解決手段】本発明の例に関わる磁気メモリは、磁化が可変な磁性層11と、磁化が固定された磁性層13と、中間層12と、膜面に対して平行方向の磁化が可変な磁性層15とを有する磁気抵抗効果素子1と、絶縁膜を介して磁気抵抗効果素子1の側面上に設けられ、磁性層15の端部から発生する磁場を収束する磁性層16と、を有する。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】積層構造を有する柱状の複数のメモリセル間のショート発生を防止した不揮発性半導体記憶装置の製造方法を提供すること。

【解決手段】本発明は、マトリクス状に配置された柱状の複数のメモリセルMCを形成する工程と、直線上に並んだ一群のメモリセルの一方の底面に各々接触し、互いに平行なワードライン47a,47c,47eを形成する工程と、直線上に並んだ一群のメモリセルの他方の底面に各々接触し、互いに平行であり、かつワードラインと同一平面視で交差するビットライン56b,56dを形成する工程とを含み、ワードラインを形成する工程では、複数のメモリセルのうち同じワードラインまたはビットラインに接触する一群のメモリセルの端部に位置する端部メモリセルMCe1,MCe3と所定間隔を隔てて配置され、メモリセルMCと同じ積層構造を有するダミーメモリセルDMC1,DMC2を形成する。

(もっと読む)

3次元垂直チャンネル構造を有する不揮発性メモリ装置のプログラム方法

【課題】本発明は、ビットラインとストリング選択ラインとの交差領域に各々形成され、各々が基板上に垂直に多層構造で形成されたメモリセルを有するストリングを含む不揮発性メモリ装置のプログラム方法を提供する。

【解決手段】本発明のプログラム方法によると、シャドープログラム方式によってYZ平面の各層に属したメモリセルがマルチビットデータにプログラムされ、YZ平面のN番目の層(ここで、Nは1、またはそれより大きい定数)のメモリセルがプログラムされる場合、YZ平面の他層のメモリセルがプログラムされる前にN番目の層に対応するXZ平面の残りのメモリセルがプログラムされる。

(もっと読む)

不揮発性メモリセルの予測的予加熱

熱的前処理を用いてスピン注入磁化反転型ランダムアクセスメモリ(STRAM)メモリセルなどの不揮発性メモリセル(120)にデータを書込むための方法(180)および装置(106)。いくつかの実施形態では、論理状態は、第1のブロックアドレスと関連付けられる未処理不揮発性第1のメモリセルに書込まれる(184)。熱的前処理は、第1のブロックアドレス(186)選択に応答して選択される第2のブロックアドレスと関連付けられる不揮発性第2のメモリセルに同時に適用される(188)ため、記録ブロックアドレスは、不揮発性第1のメモリセルの書込動作に引続く書込動作で選択される可能性が比較的高いブロックのアドレスである。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】最適な書き込み電流を磁気抵抗素子に供給する。

【解決手段】半導体記憶装置は、半導体基板11に設けられた選択トランジスタ13と、半導体基板11の上方に設けられ、かつ第1の方向に延在する第1の配線層BLと、磁化の方向が固定された固定層22Aと、固定層22A上に設けられた非磁性層22Bと、非磁性層22B上に設けられかつ磁化の方向が可変である記録層22Cとを有し、かつ第1の配線層BLの上方に設けられ磁気抵抗素子22と、第1の方向に延在し、かつ選択トランジスタ13の拡散領域17に電気的に接続された第2の配線層bBLとを含む。固定層22Aは第1の配線層BLに電気的に接続され、記録層22Cは選択トランジスタ13の拡散領域16に電気的に接続される。

(もっと読む)

磁性細線ユニット及び記憶装置

【課題】磁性細線の磁壁移動に要する電流を低減し、且つ磁壁保持時の状態を安定にする。

【解決手段】磁性細線の材料として、遷移温度を境に磁化容易軸が面内方向と垂直方向とで遷移する材料を用いる。この場合、磁性細線12の磁化容易軸が面内方向である第1の状態にあるときには、磁壁48を移動させるための電流供給が行われず、磁壁の移動に要する電流が小さい磁化容易軸が垂直方向である第2の状態にあるときにのみ、磁壁を移動させるための電流供給が行われるようなシーケンスを実行することにより、磁壁移動時に必要とする電流を低減することが可能である。また磁壁48を移動しない状態は第1の状態であり、磁壁の保持を安定化させることが可能である。

(もっと読む)

磁気記憶装置

【課題】直流電流に重畳させる交流電流の周波数と磁化自由層の磁化の固有振動数とを完全に一致させてスピン偏極電流を確実に低減し得る。

【解決手段】磁化固定層、磁化自由層、および磁化固定層と磁化自由層との間に配設された非磁性スペーサー層を備えた磁気抵抗効果素子2と、磁化自由層に磁場Hを印加する磁場印加部3と、磁化固定層と磁化自由層との間に交流電流が重畳された交流重畳直流電圧Vddを供給する電源供給部4とを備え、電流供給部4は、磁気抵抗効果素子2についての磁化自由層の磁化の固有振動数を含む周波数範囲内で交流電流の周波数をスイープさせる。

(もっと読む)

磁気記録装置

【課題】磁気記録装置における多層記録・多値記録を実現する解決手段を提供する。

【解決手段】複数層の記録層からなる媒体を異なる磁気共鳴周波数になるように設定し、高周波発振素子を具備する記録ヘッドの高周波発振周波数を変えることによって、記録を行う記録層を選択し、情報を記録する。また、再生時には、複数層からなる媒体層の磁化状態によって、媒体層外部に漏れ出る磁界が異なるようにし、多値状態によって異なる外部磁界を磁気抵抗効果素子で異なる抵抗値として検知することで、多値状態の識別を行う。

(もっと読む)

半導体記憶装置

【課題】メモリセルの高密度化を図れるMRAMやPRAM等の半導体記憶装置を提供する。

【解決手段】間隔を有して順に配置され、膜面に対して垂直方向に電流を流すことで記録が行われる第1乃至第4の抵抗変化素子MTJ1〜MTJ4と、第1及び第2の抵抗変化素子を接続する第1の電極15と、第3及び第4の抵抗変化素子を接続する第2の電極15と、第2及び第3の抵抗変化素子を接続するビット線BL2と、抵抗変化素子と対をなし、第1及び第2の電極と離間して配置されたワード線WL1〜WL4と、第1乃至第4の抵抗変化素子の中の選択素子にデータを書き込む時、第1乃至第4の抵抗変化素子と第1及び第2の電極とビット線とを有するチェーン構造部に第1の電流Iw1を流す第1の電流源と、選択素子にデータを書き込む時、選択素子に対応する第1乃至第4のワード線の中の選択ワード線に第2の電流Iw2を流す第2の電流源とを具備する。

(もっと読む)

磁区壁移動を利用したメモリ装置

【課題】磁区壁移動を利用した記録装置を提供する。

【解決手段】磁区壁移動を利用したメモリ装置において、磁性物質からなり、磁壁を含み、第1方向に形成された書き込み用トラック61と、第1トラック上に形成された中間層62と、中間層上に第2方向に形成され、磁性物質からなり、磁壁を含む情報保存用トラック63と、を備える磁区壁移動を利用したメモリ装置である。

(もっと読む)

磁気メモリ装置及びその製造方法

【課題】記憶容量が大きく、しかも耐熱性に優れる磁気メモリ装置及びその製造方法を提供する。

【解決手段】磁壁30の移動を規制する規制領域32が所定の間隔で形成され、規制領域間の領域が記録ビット34となる線状の記録層22を有し、記録層22に一軸磁気異方性を付与する手段24を有している。記録層に対して一軸磁気異方性を付与する手段を有しているため、十分な一軸磁気異方性を記録層において得ることができる。このため、記録層の幅Dを比較的狭くした場合であっても、耐熱性の高い磁気メモリ装置を提供することができる。

(もっと読む)

磁気メモリ、及びその駆動方法

【課題】高記録密度の磁気メモリを実現する。

【解決手段】情報記録媒体としての磁性細線1に対し、リザーブ領域95の長さに等しい長さで、等間隔に記録素子16a〜16dまたは再生素子17a〜17dを配置している。例えば情報の記録時に、端子21aと端子21cとを選択して電圧を印加し、記録領域94a内の磁壁をリザーブ領域95に向かって移動させると、リザーブ領域95の長さ分、磁壁を移動させる間に、全磁区が、記録素子16aおよび16bのどちらかを通過する。情報の再生時についても、記録領域94bの磁区についても、同じことがいえる。したがって、記録領域94a・94bの全磁区の記録再生を可能としながら、従来より遥かに高密度の記録再生を可能にする。

(もっと読む)

1 - 20 / 22

[ Back to top ]