Fターム[4M119EE40]の内容

MRAM・スピンメモリ技術 (17,699) | 配線構成 (2,374) | その他の配線に関する技術 (41)

Fターム[4M119EE40]に分類される特許

1 - 20 / 41

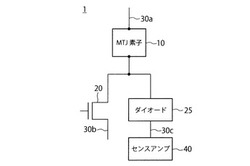

磁気抵抗効果素子、ダイオードおよびトランジスタを用いた磁気ランダムアクセスメモリ

【課題】高速動作を可能にする磁気メモリを提供する。

【解決手段】本実施形態の磁気メモリは、スピン注入書込みによって磁化の方向が不変の第1磁性層と、磁化の方向が可変の第2磁性層と、前記第1磁性層と前記第2磁性層との間に設けられたトンネル障壁層とを有する磁気抵抗効果素子と、前記磁気抵抗効果素子の前記第1および第2磁性層の一方の磁性層に電気的に接続された第1配線と、ソース/ドレインの一方が前記磁気抵抗素子の前記第1および第2磁性層の他方に電気的に接続された選択トランジスタと、前記選択トランジスタのソース/ドレインの他方に電気的に接続された第2配線と、前記磁気抵抗素子の前記第1および第2磁性層の他方に電気的に一端子が電気的に接続されたダイオードと、前記ダイオードの他の端子に電気的に接続された第3配線と、前記第3配線に電気的に接続されたセンスアンプと、を備えている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセル部及び周辺回路部を微細化する。

【解決手段】半導体基板20に設けられたメモリセル部11及び周辺回路部12を有する半導体記憶装置の製造方法であって、メモリセル部11及び周辺回路部12にそれぞれ層間絶縁層37及び47を形成する工程と、層間絶縁層37及び47上にそれぞれ、心材50を形成する工程と、心材50をスリミングする工程と、メモリセル部11及び周辺回路部12の心材50の側面にそれぞれ、側壁38及び48を形成する工程と、側壁38及び48をマスクとして、層間絶縁層37及び47を加工する工程と、加工された層間絶縁層37及び47内にそれぞれビット線BL及び配線層44を形成する工程とを含む。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 セル面積を縮小させつつ、コストの増大を抑制する。

【解決手段】 実施形態による磁気ランダムアクセスメモリは、第1の方向Xに所定のピッチ2Fを有して配置され、第1の方向と直交する第2の方向Yに延在された第1及び第2のゲート電極GC1、GC2と、第1及び第2のゲート電極間の上方に配置された磁気抵抗素子MTJaと、磁気抵抗素子より高い位置に配置され、磁気抵抗素子と第1の方向にピッチの半分の距離Fを有して配置された電極層UE2と、電極層より高い位置に配置され、第1の方向に延在された配線M1と、磁気抵抗素子と配線との接続及び電極層と配線との接続を1つの導電層で行うビアV1Yと、を具備する。

(もっと読む)

半導体装置、及び半導体装置の制御方法。

【課題】簡便な半導体装置の評価試験を実現する。

【解決手段】半導体装置10は、それぞれ内部信号MAを生成する第1及び第2のコアチップCC0,CC1を備え、第1及び第2のコアチップCC0,CC1のそれぞれに、貫通電極を介して他方のコアチップとスパイラル接続された第2及び第3のノードN2,N3を設け、この第2及び第3のノードN2,N3を介して、観測対象の内部信号MAを外部に出力することを技術思想とするものである。こうして出力される複数の内部信号MAを外部のテスター等によって観測することで、各コアチップの評価試験を並列に行える。

(もっと読む)

磁気メモリ装置のためのライトドライバー回路、磁気メモリ装置及びそのレイアウト構造

【課題】本発明の技術的な課題は、共通ソースラインを含む磁気メモリ装置に対してビットラインへ記録電流を供給することができるライトドライバー回路を提供すること、集積度が向上された磁気メモリ装置を提供すること、及び、共通ソースラインを有する磁気メモリ装置のレイアウト構造を提供することにある。

【解決手段】ビットラインとソースラインとの間に接続され、前記ビットライン方向に隣接する一対の磁気メモリセルが前記ソースラインを共有する複数の磁気メモリセルよりなるメモリセルアレイを有する磁気メモリ装置のためのライトドライバー回路であり、正の記録電圧の供給端子と副の記録電圧の供給端子との間に接続されて、ライトイネーブル信号及びデータ信号によって前記正の記録電圧または前記副の記録電圧による電流を前記ビットラインに選択的に供給するスイチング部を備える磁気メモリ装置を提供する。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】書き込み電流を低減する磁気ランダムアクセスメモリを提供する。

【解決手段】磁気ランダムアクセスメモリは、半導体基板と、半導体基板の上方に配置され、垂直磁化膜で形成されたMTJ素子10と、MTJ素子10の上側に配置されかつ半導体基板に対して引っ張る方向に応力を加える引っ張り応力膜21及びMTJ素子10の下側に配置されかつ半導体基板に対して圧縮する方向に応力を加える圧縮応力膜の少なくとも一方を有する応力膜と、を具備する。

(もっと読む)

半導体装置

【課題】制御チップと複数の被制御チップが積層されたタイプの半導体装置において、コマンド信号よりも層アドレス信号を早く伝送させる。

【解決手段】互いに異なる層情報を保持する複数の被制御チップCC0〜CC7と、被制御チップCC0〜CC7に対して層アドレス信号A13〜A15及びコマンド信号ICMDを共通に供給する制御チップIFとを備える。層アドレス信号A13〜A15を構成する各ビットは、複数の第1の貫通電極のうち、被制御チップごとに並列接続された少なくとも2本の貫通電極を経由して伝送され、コマンド信号ICMDを構成する各ビットは、出力切り替え回路及び入力切り替え回路によって選択された対応する1本の貫通電極を経由して伝送される。これにより、コマンド信号ICMDよりも先に層アドレス信号A13〜A15が各被制御チップに到達する。

(もっと読む)

集積磁気薄膜増強回路素子を有する磁気抵抗ランダムアクセスメモリ(MRAM)

不揮発性記憶装置およびその製造方法

【課題】より低抵抗な配線層を有する不揮発性記憶装置を提供する。

【解決手段】実施形態の不揮発性記憶装置は、書き替え可能な複数の不揮発性メモリセルと、前記複数のメモリセルのそれぞれに電気的に接続可能な配線層と、を備えた不揮発性半導体記憶装置である。前記配線層は、絶縁層に設けられたトレンチ内に設けられ、前記配線層は、第1導電層と、前記第1導電層の上に設けられた第2導電層と、を有し、前記配線層が充填されていない前記トレンチに対する前記第1導電層の埋め込み性は、前記配線層が充填されていない前記トレンチに対する前記第2導電層の埋め込み性よりも高く、前記第2導電層の比抵抗は、前記第1導電層の比抵抗よりも低い。

(もっと読む)

不揮発性記憶装置

【課題】電源投入後、高速なセットアップが可能な不揮発性記憶装置を提供する。

【解決手段】不揮発性記憶装置は、データを不揮発的に記憶するメモリセルを有する第1および第2のメモリモジュール16−1、16−2と、第1および第2のメモリモジュールとそれぞれ接続されて、前記第1および第2のメモリモジュールを駆動するための外部電源を供給する第1および第2の外部電源線VL11、VL12とを備え、第1の外部電源線の電源容量C1は、前記第2の外部電源線の電源容量C2よりも小さい。

(もっと読む)

シフトレジスタ型記憶装置及びデータ記憶方法

【課題】信頼性が高いシフトレジスタ型記憶装置及びデータ記憶方法を提供する。

【解決手段】一態様によれば、一方向に沿って連なり、その特徴方向が前記一方向に延びる回転軸についてそれぞれ回転可能な複数の回転子を備えたシフトレジスタが提供される。前記複数の回転子には一軸異方性が付与され、前記複数の回転子は、隣り合う2つの前記回転子毎に複数の対に組分けされており、同一の前記対に属する2つの前記回転子には、前記特徴方向を反平行とするような第1の力が作用し、隣り合う前記対に属する隣り合う2つの前記回転子には、前記第1の力よりも弱く、前記特徴方向を反平行とするような第2の力が作用する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】下層の配線層にMTJ素子を形成しつつ、MTJ素子に熱が加わることを抑制する。

【解決手段】基板10上に絶縁層220を形成する。次いで絶縁層220上にMTJ素子100を形成する。次いで、MTJ素子100上に配線242を形成する。次いで配線242上に絶縁層250を形成する。次いで絶縁層250の表層に配線252を形成する。そして配線252を光照射により熱処理する。そして配線252を形成する工程において遮蔽導体254を形成する。

(もっと読む)

情報処理方法、積層型集積回路メモリ

【課題】メモリの単位メガバイト当たり製造コストを、単にモノリシック回路集積法で慣用的に製造される回路の数分の一に低減させる。

【解決手段】各層が別々に最適化されるように、別々の層(103)上へのメモリ回路(103)および制御論理回路(101)の物理的分離が可能な三次元(3DS)メモリ(100)。幾つかのメモリ回路(103)について1つの制御論理回路(101)で十分であり、コストを低減できる。3DSメモリ(100)の製造は、メモリ回路(103)を50μm以下の厚さに薄肉化する工程と、該メモリ回路を、ウェーハ基板形態のまま回路積層体に接合する工程とを有する。微粒子の高密度層間垂直バス相互接続部(105)が使用されている。3DSメモリ(100)製造方法は、幾つかの性能および物理的サイズ効率を可能にしかつ確立された半導体加工技術により実施される。

(もっと読む)

薄膜磁性体記憶装置

【課題】磁気トンネル接合部(MTJ)を有するメモリセルを用いてデータ記憶を行なう薄膜磁性体記憶装置において、データ読出動作を高速化する。

【解決手段】MTJメモリセルに対しては、データ書込およびデータ読出にそれぞれ用いられるライトワード線WWLおよびリードワード線RWLが独立して設けられる。メモリアレイ10を列方向に分割して形成される領域AR1,AR2ごとにリードワード線RWLを分割配置することによって、リードワード線RWLにおける信号伝搬遅延を低減して、データ読出動作を高速化できる。各リードワード線RWLの活性化は、行選択結果に応じてライトワード線WWLと階層的に制御される。ワード線電流制御回路40は、データ書込時およびデータ読出時のそれぞれに対応して、ライトワード線WWLにおける電流経路を形成および遮断する。

(もっと読む)

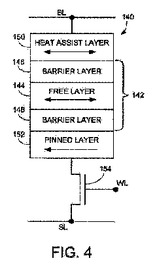

静磁場によりアシストされた抵抗性検知素子

スピン注入型ランダムアクセスメモリ(STRAM)等の不揮発性メモリセル(140,154)にデータを書込むための装置および関連する方法。いくつかの実施例に従うと、抵抗性検知素子(RSE)(140)は、ヒートアシスト領域(150)、磁気トンネル接合(MTJ)(142)およびピン止め領域(152)を有する。スピン分極された電流を用いてMTJに第1論理状態が書込まれるとき、ピン止め領域およびヒートアシスト領域は、各々、実質的にゼロの正味磁気モーメントを有する。静磁場を用いてMTJに第2論理状態が書込まれるとき、ピン止め領域は実質的にゼロの正味磁気モーメントを有し、ヒートアシスト領域は非ゼロの正味磁気モーメントを有する。  (もっと読む)

(もっと読む)

三次元的スタックド不揮発性メモリユニット

メモリユニット(200)であって、メモリユニットの第1の層において第1のトランジスタ領域に広がる第1のトランジスタ(210)と、メモリユニットの第2の層において第2のトランジスタ領域に広がる第2のトランジスタ(220)と、メモリユニットの第3の層において第1のメモリ領域に広がる第1の抵抗センスメモリ(RSM)セル(230)と、メモリユニットの第3の層において、第2のメモリ領域に広がる第2のRSMセル(250)とを含む。第1のトランジスタは第1のRSMセルに電気的に結合され、第2のトランジスタは第2のRSMセルに電気的に結合される。第2の層は第1の層と第3の層との間にある。第1のトランジスタおよび第2のトランジスタは、トランジスタ重畳領域を有する。第1のメモリ領域および第2のメモリ領域は、第1のトランジスタ領域および第2のトランジスタ領域を越えて延在しない。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置

【課題】可変抵抗素子を記憶素子として利用する不揮発性半導体記憶装置のアクセス時間を消費電流を増大することなく短縮する。

【解決手段】メモリセル(MC)に対し、書込ビット線(WBL)および読出ビット線(RBL)をそれぞれ別々に設け、またメモリセルの接続するソース線(SL)を、基板領域と同一導電型のソース不純物領域(3)で形成する。メモリセルトランジスタ(MT)とソース不純物領域とは、低抵抗のメタル配線(4)により接続する。ソース線電位の浮き上がりを防止することができ、正確に記憶データに応じたメモリセル電流を生じさせることができ、高速でデータの読出を行うことができる。また、読出ビット線単位でプリチャージおよびデータ増幅を行うことにより読出ビット線負荷を軽減して高速読出を実現することができる。

(もっと読む)

積層メモリ素子

【課題】集積度を高めることが容易な3次元積層された多層構造メモリ素子を提供する。

【解決手段】本積層メモリ素子は、基板と、基板上に相互積層され、複数の群に分割された複数のメモリ層と、各群内のメモリ層と電気的に接続され、各群内のメモリ層の間に配された複数のインターデコーダと、複数のインターデコーダと電気的に接続され、複数のインターデコーダの間に配された少なくとも一つのプレデコーダと、を備えることを特徴とする。

(もっと読む)

半導体記憶装置

【課題】最適な書き込み電流を磁気抵抗素子に供給する。

【解決手段】半導体記憶装置は、半導体基板11に設けられた選択トランジスタ13と、半導体基板11の上方に設けられ、かつ第1の方向に延在する第1の配線層BLと、磁化の方向が固定された固定層22Aと、固定層22A上に設けられた非磁性層22Bと、非磁性層22B上に設けられかつ磁化の方向が可変である記録層22Cとを有し、かつ第1の配線層BLの上方に設けられ磁気抵抗素子22と、第1の方向に延在し、かつ選択トランジスタ13の拡散領域17に電気的に接続された第2の配線層bBLとを含む。固定層22Aは第1の配線層BLに電気的に接続され、記録層22Cは選択トランジスタ13の拡散領域16に電気的に接続される。

(もっと読む)

1 - 20 / 41

[ Back to top ]