Fターム[4M119FF05]の内容

MRAM・スピンメモリ技術 (17,699) | コンタクト (2,004) | コンタクトの形状又は作成方法 (789) | プラグを有するもの (536)

Fターム[4M119FF05]に分類される特許

161 - 180 / 536

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

磁気メモリ素子

【課題】低い消費電力で動作する磁気メモリ素子の実現。

【解決手段】垂直磁化膜であって情報に対応して磁化の向きが変化する記憶層と、記憶層に対して非磁性層を介して設けられる垂直磁化膜であって磁化方向が固定されて記憶された情報の基準となる参照層とを有する磁気メモリ素子に、磁化が膜面内に環状とされた渦磁化層を設けるようにする。渦磁化層は、記憶層の、参照層側の面とは反対側の面に対して、非磁性層を介して設ける。

(もっと読む)

磁気メモリ素子

【課題】垂直磁化を用いた磁気メモリ素子において、作製プロセスに耐え、薄い膜厚で大きな保磁力と高い耐熱性を有する参照層を実現する。

【解決手段】参照層は、20原子%以上50原子%以下のPtを含有し、1nm以上5nm以下の膜厚を有する、少なくとも2以上のCoPt層が、Ru層を介して積層された構造を有するものとする。そしてRu層の厚みは、0.45±0.05nmあるいは0.9±0.1nmとする。またCoPt層の結晶の3回対称軸が膜面垂直に配向する。またスピン注入層との界面を、1.5nm以下のCo又はFeを主成分とする高スピン分極層とする。

(もっと読む)

不揮発性磁気メモリ装置

【課題】記録層における磁化容易軸が垂直方向を向いている垂直磁化型の不揮発性磁気メモリ装置において、記録層の磁化容易軸をより確実に垂直方向に向かせることを目的とする。

【解決手段】不揮発性磁気メモリ装置は、磁化容易軸が垂直方向を向いている記録層を有する積層構造体50、第1の配線41、及び、第2の配線42から成る磁気抵抗効果素子を備えており、積層構造体50の上、又は、積層構造体50の下、又は、積層構造体50の上及び下には、記録層53を構成する材料のヤング率よりも低い値のヤング率を有する低ヤング率領域481が配置されており、積層構造体50は磁化参照層51を更に有し、低ヤング率領域481を配置することによって記録層53及び磁化参照層51において内部応力が発生し、記録層53及び磁化参照層51の垂直磁気異方性が増大される。

(もっと読む)

磁気メモリ素子、磁気メモリ素子の製造方法

【課題】低電流で高速に動作可能な磁気メモリ素子の実現。

【解決手段】垂直磁化膜であって情報に対応して磁化の向きが変化する記憶層と、記憶層に対して非磁性層を介して設けられる垂直磁化膜であって磁化方向が固定されて記憶された情報の基準となる参照層とを有する磁気メモリ素子であって、記憶層、非磁性層、参照層から成る層間に電流を流した際に発生するスピントルクで磁化反転を行って情報を記憶する。この場合に、記憶層の記憶時の温度(200℃)における保磁力が、室温(23℃)時の保磁力の0.7倍以下とする。また記憶層の一面側に形成される電極の、膜面方向の中央部に、例えば低熱伝導率の絶縁体を補填することで、その周辺部よりも熱伝導度が低くなるように形成する。これにより記憶層の中央部での温度上昇を促進し、記憶時の磁化反転電流を下げる。

(もっと読む)

磁気抵抗素子および磁気抵抗素子の製造方法

【課題】従来のTMR素子に比べて磁気抵抗を大きくし、出力電圧を大きくすることを目的とする。

【解決手段】磁気抵抗素子は、基板と、前記基板上に形成されたCo,Fe,Bを含む磁性合金からなる強磁性体層と、前記強磁性体層上にトンネル障壁層として(001)結晶面が優先配向した多結晶MgOとを有することに特徴がある。

(もっと読む)

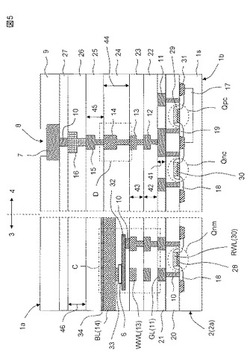

半導体装置、および、半導体装置の製造方法

【課題】磁壁移動型の磁気抵抗素子の微細化を実現する。

【解決手段】基板上に位置する第1の絶縁層24と、第1の絶縁層の24内部に位置し、互いに電気的に絶縁した一対の第1の磁化固定層20a、20bと、第1の絶縁層24上に位置し、平面視で一対の第1の磁化固定層20a、20bいずれとも重なり、かつ、一対の第1の磁化固定層20a、20bいずれとも電気的に接続している磁化自由層31と、磁化自由層31上に位置する第2の絶縁層33と、第2の絶縁層33に形成され、平面視で磁化自由層31と重なる孔と、当該孔の底面および側面に沿って形成された非磁性層41と、非磁性層41形成後の孔内に埋め込まれた第2の磁化固定層42と、を有し、第2の磁化固定層42は、平面視で一対の第1の磁化固定層20a、20bいずれとも重ならず、かつ、平面視で一対の第1の磁化固定層20a、20bの間に位置する半導体装置。

(もっと読む)

磁気抵抗素子

【課題】従来のTMR素子に比べて磁気抵抗を大きくし、出力電圧を大きくすることを目的とする。

【解決手段】磁気抵抗素子は、BCC構造を有するFe系合金であって(001)結晶面が優先配向した単結晶または(001)結晶面が優先配向した多結晶からなる第1の強磁性体層と、BCC構造を有するFe系合金であって(001)結晶面が優先配向した単結晶または(001)結晶面が優先配向した多結晶からなる第2の強磁性体層と、前記第1の強磁性体層と前記第2の強磁性体層との間に位置するトンネル障壁層とを有し、前記トンネル障壁層が、(001)結晶面が優先配向した単結晶MgOあるいは(001)結晶面が優先配向した多結晶MgOを含み、前記(001)結晶面が優先配向した単結晶MgOあるいは(001)結晶面が優先配向した多結晶MgOのトンネル障壁の高さφが0.2〜0.5eVであることに特徴がある。

(もっと読む)

磁気メモリ

【課題】磁気メモリの信頼性及び動作特性の向上を図る。

【解決手段】磁気メモリは、第1及び第2の磁性層の間に設けられた中間層とを有する磁気抵抗効果素子と、磁気抵抗効果素子に書き込まれた第1のデータが第1のデータが誤りを含むか否かを検出し、第1のデータが誤りを含む場合にその誤りが訂正された第2のデータを出力する誤り検出訂正回路と、第1のパルス幅Twp1を有する第1の書き込み電流Iw1及び第1のパルス幅Twp1より長い第2のパルス幅Twp2を有する第2の書き込み電流Iw2のいずれか一方を生成し、磁気抵抗効果素子に流す書き込み回路と、第2のデータを磁気抵抗効果素子に書き込む場合、第2の書き込み電流Iw2を磁気抵抗効果素子に流すように書き込み回路を制御する制御回路と、を備える。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 書き込み電流の低減を図る。

【解決手段】 実施形態による磁気ランダムアクセスメモリは、メモリセルに磁気抵抗素子100を備えた磁気ランダムアクセスメモリであって、磁気抵抗素子100は、第1の金属磁性層24と、第2の金属磁性層26と、第1及び第2の金属磁性層24、26に挟まれた絶縁層25と、を具備し、第1及び第2の金属磁性層24、26の各面積は、絶縁層25の面積より小さい。

(もっと読む)

抵抗変化メモリ

【課題】大きい静電容量のキャパシタを含む抵抗変化メモリを提供する。

【解決手段】本実施形態の抵抗変化メモリは、アクティブ領域としての半導体領域20と、ゲート絶縁膜22を介して半導体領域21の側面に対向するゲート電極21とを有する選択トランジスタと、記憶するデータに応じて抵抗値が変化するメモリ素子1とを含むメモリセルMCと、第1のキャパシタ電極としての半導体領域30と、半導体領域30の側面に対向するキャパシタ電極31と、半導体領域20とキャパシタ電極31との間に設けられたキャパシタ絶縁膜32とを含むキャパシタ3と、を含む。

(もっと読む)

抵抗変化型半導体メモリ

【課題】セル面積の縮小及び動作特性の向上に優れたレイアウトを提案する。

【解決手段】実施形態によれば、抵抗変化型半導体メモリは、第1方向に並ぶ第1乃至第4メモリセルを備える。第1乃至第4メモリセルの各々は、第1ソース/ドレインが第1方向に延びる第1ビット線BLA1に接続され、ゲートが第2方向に延びるワード線WL1, WL2, WL3, WL4に接続されるセルトランジスタT11, T12, T13, T14と、一端がセルトランジスタT11, T12, T13, T14の第2ソース/ドレインに接続され、他端が第2方向に延びる第2ビット線BLB1, BLB2, BLB3, BLB4に接続される抵抗性記憶素子M11, M12, M13, M14とを有する。第1及び第2メモリセル内の第1ソース/ドレインは、共有化され、第3及び第4メモリセル内の第1ソース/ドレインは、共有化される。

(もっと読む)

記憶素子、記憶素子の製造方法、及び、メモリ

【課題】消費電力化が可能な記憶素子を提供する。

【解決手段】積層方向に電流を流して、スピン偏極した電子を注入することにより、記憶層16の磁化M1の向きが変化して、記憶層16に対して情報の記憶が行われる記憶素子3を構成する。この記憶素子3は、情報を磁性体の磁化状態により保持する記憶層16と、記憶層16に対してトンネルバリア層15を介して設けられている磁化固定層14とを備える。そして、トンネルバリア層15は、厚さが0.1nm以上0.6nm以下であり、且つ、界面ラフネスが0.5nm未満である。

(もっと読む)

磁気記憶素子及び磁気メモリ

【課題】情報保持特性を低下することなくスピン注入による磁化反転を起こすために必要な電流を低減化する。

【解決手段】磁化方向が所定の方向に固定された参照層26と、スピン注入により磁化方向が変化する記録層28と、記録層28と参照層26を隔てる中間層27と、記録層28を加熱する発熱部33と、を備える。記録層28の材料は、磁化量が150℃で室温時の磁化量の50%以上となり、150℃以上200℃以下の範囲で室温時の磁化量の10%以上80%以下となる磁性体より構成する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルのトランジスタの配置効率が高い不揮発性半導体記憶装置を提供する。

【解決手段】このMRAMでは、各メモリセルMCのアクセストランジスタを2つのトランジスタQA,QBに分割し、トランジスタQA,QBのゲートをそれぞれワード線WLA,WLBに接続し、奇数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLAに接続し、偶数番のメモリブロックMBのワード線WLA,WLBを主ワード線MWLBに接続する。したがって、メモリセルMCのトランジスタの配置効率を高めることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体集積回路の高集積化と機能素子の高性能化とを同時に実現する。

【解決手段】実施形態に係わる半導体装置は、半導体基板1の表面領域に配置されるスイッチ素子3,4と、下面がスイッチ素子3,4に接続されるコンタクトプラグ6と、コンタクトプラグ6の上面の直上に配置される機能素子7とを備える。コンタクトプラグ6の上面の最大表面粗さは、0.2nm以下である。

(もっと読む)

記憶素子及び記憶装置

【課題】少ない電流で高速に動作させることが可能な記憶素子を提供する。

【解決手段】磁化の向きが膜面に垂直な方向の垂直磁化層17と、非磁性層16と、膜面内方向に磁化容易軸を有し、磁化の向きが膜面に垂直な方向から15度以上45度以下の角度で傾斜している、強磁性層15と、垂直磁化層17と強磁性層15とが非磁性層16を介して積層され、垂直磁化層17と強磁性層15とが磁気的結合して成る記憶層22と、磁化の向きが膜面に垂直な方向に固定された磁化固定層21と、記憶層22及び磁化固定層21の間に配置された、非磁性の中間層15とを含み、各層の積層方向に電流を流すことにより情報の記録が行われる記憶素子20を構成する。

(もっと読む)

磁気記憶装置

【課題】書込み電流の増大や書込みの信用性の向上が図られた磁気記憶装置を提供する。

【解決手段】磁気記憶装置は、基板11と、基板11上に設けられたライト線WTと、ライト線WTに対して基板11の厚み方向に間隔をあけて配置され、ライト線WTの延在方向と交差する方向に延びるビット線BLと、ライト線WTおよびビット線BLの間に位置する磁気記憶素子MMとを備え、磁気記憶素子MMは、磁化方向が固定された固定層1と、外部磁界によって磁化方向が変化する記録層3とを含み、記録層3は合金膜を含み、合金膜はコバルトと鉄とホウ素とを含み、ホウ素は21at%より高い。

(もっと読む)

半導体装置およびその製造方法

【課題】生産コストを抑えながら高いスループットが得られる半導体装置の製造方法と半導体装置とを提供する。

【解決手段】ヨークカバーとなる積層膜として、バリアメタル層、磁性体層およびバリアメタル層が順次形成される。次に、積層膜MLに、四フッ化炭素(CF4)ガスとアルゴン(Ar)ガスとの混合ガスによる反応性イオンエッチング処理、一酸化炭素(CO)、アンモニア(NH3)ガスおよびアルゴン(Ar)ガスの混合ガスによる反応性イオンエッチング処理、四フッ化炭素(CF4)ガスとアルゴン(Ar)ガスとの混合ガスによる反応性イオンエッチング処理を施すことにより、ヨークカバーYCが形成される。

(もっと読む)

抵抗変化メモリ

【課題】高い抵抗値の抵抗素子を実現する。

【解決手段】本実施形態の抵抗変化メモリは、第1の配線レベルILV1に位置し、第1の方向に延びる制御線L1と、第2の配線レベルILV2に位置し、第2の方向に延びる制御線L2と、制御線L1と制御線L2との間に設けられるセルユニットCUとを含むメモリセルアレイを有し、複数の配線レベルに設けられる少なくとも2つの抵抗線RL3A,RL5と、抵抗線RL3A,RL5間に設けられ、セルユニットCUの構成部材又はコンタクトプラグZCの構成部材と同じ構成部材を含む抵抗体91と、を有し、抵抗素子領域17内に設けられる抵抗素子90を含んでいる。

(もっと読む)

161 - 180 / 536

[ Back to top ]