Fターム[4M119FF05]の内容

MRAM・スピンメモリ技術 (17,699) | コンタクト (2,004) | コンタクトの形状又は作成方法 (789) | プラグを有するもの (536)

Fターム[4M119FF05]に分類される特許

201 - 220 / 536

半導体素子の製造方法

【課題】本発明は半導体素子の製造方法を提供すること。

【解決手段】基板上に下地膜を形成する。前記下地膜上に犠牲膜を形成する。前記犠牲膜をパターニングして前記下地膜の所定領域を露出させる開口部を形成する。前記開口部内にマスク膜を形成する。前記マスク膜の一部または全部を酸化させて酸化物マスクを形成する。前記犠牲膜を除去する。前記酸化物マスクをエッチングマスクとして用いて前記下地膜をエッチングして下地膜パターンを形成する。

(もっと読む)

磁気抵抗効果素子、それを用いた磁気メモリセル及びランダムアクセスメモリ

【課題】垂直磁化材料を適用し、TMR比の高い磁気抵抗効果素子を提供する。

【解決手段】CoFeB層41/MgOバリア層10/CoFeB層42の外側に融点が1600℃以上の単体金属、もしくはその金属を含んだ合金からなる中間層31,32を挿入する。中間層31,32の挿入により、アニール時におけるCoFeB層の結晶化をMgO(001)結晶側から進行させ、CoFeB層をbcc(001)で結晶配向させる。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】自由層と固定層の相対的な磁化方向を平行から反平行に反転する際、選択トランジスタのバックバイアス効果による書き込み電流の減少を防止でき、かつメモリセルの面積増大を防ぐことができる磁気ランダムアクセスメモリを提供できる。

【解決手段】半導体基板上に形成され、磁化方向が固定された固定層と、固定層上に形成された非磁性層と、非磁性層上に形成され、磁化方向が可変である自由層とを含むMTJ素子11と、半導体基板に形成されたアクティブ領域12と、アクティブ領域12に形成された第1の拡散領域及び第2の拡散領域を有し、第1の拡散領域が自由層に電気的に接続された第1の選択トランジスタとを備える。さらに、アクティブ領域12に形成された前記第1の拡散領域及び第3の拡散領域を有する第2の選択トランジスタと、固定層に電気的に接続された第1の配線とを備える。

(もっと読む)

減電圧の入出力デバイス(REDUCEDVOLTAGEINPUT/OUTPUTDEVICE)を有する抵抗ベースメモリ

減電圧のI/Oデバイスを含む抵抗ベースメモリが開示される。特定の一実施形態では、回路は、第1の抵抗メモリセルおよび第1の負荷トランジスタを含むデータ経路を含む。基準経路は、第2の抵抗メモリセルおよび第2の負荷トランジスタを含む。第1の負荷トランジスタおよび第2の負荷トランジスタは、回路内のコアトランジスタのコア供給電圧と同等の負荷供給電圧で動作するように構成された入出力(I/O)トランジスタである。  (もっと読む)

(もっと読む)

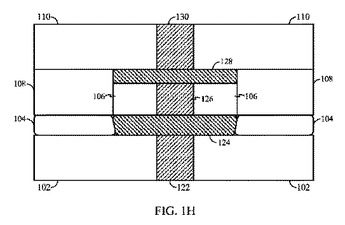

平坦化された電極上の磁気トンネル接合(MTJ)

直接接触を用いた磁気トンネル接合(MTJ)は、より低い抵抗、改善された生産量、及び、より単純な製造を有して製造される。より低い抵抗は、MTJの読み取り方法及び書き込み方法の両方を改善する。MTJ層(126)は、下部電極(124)上に堆積され、下部金属(122)に位置合わせされる。エッチング停止層(302)は、下部金属を囲う絶縁体のオーバーエッチングを防止するために下部金属に隣接して堆積され得る。下部電極は、実質的に平坦な表面を提供するためにMTJ層の堆積前に平坦化される。さらに、下層(202)は、MTJの所望の特性を促進するためにMTJ層の前に下部電極上に堆積され得る。  (もっと読む)

(もっと読む)

スピンMOS電界効果トランジスタ

【課題】スピン分極率の高いフルホイスラー合金と反強磁性結合を形成する磁性体を含む、TMR比が高い磁気抵抗効果素子を用いたスピンMOS電界効果トランジスタを提供する。

【解決手段】半導体基板10上に形成されたフルホイスラー合金層13と、フルホイスラー合金層13上に形成された、面心立方格子構造を有する強磁性体層14と、強磁性体層14上に形成された非磁性層15と、非磁性層15上に形成された強磁性体層16とを含む構造をソース及びドレインのうち少なくとも一つに備える。非磁性層15を介して形成された強磁性層14と強磁性層16との間には反強磁性結合が形成されている。

(もっと読む)

半導体装置の製造方法

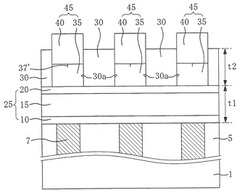

【課題】磁気素子を備えた半導体装置の製造で、磁気素子のダメージを抑止し、下部電極膜の加工に灰化処理を用いないことで下層に存する導電部材の酸化を防止する。

【解決手段】半導体基板10上で、上部電極膜43上に形成したレジストマスク44で上部電極膜43をエッチングして上部電極43aとし、上部電極43aをマスクとしてMTJ膜42をエッチングしてMTJ42aとし、上部電極43a及びMTJ42aを覆う保護膜45aを形成し、上部電極43a及びMTJ42aを保護膜45aを介して覆うように、保護膜45a上にレジスト46を形成し、レジストマスク46で保護膜45aをエッチングし、保護膜45aをマスクとして下部電極膜41エッチングして下部電極41aとし、上部電極43a、MTJ42a及び下部電極41aを覆うように保護膜45bを形成して、保護膜45b上に層間絶縁膜47を形成する。

(もっと読む)

半導体装置

【課題】磁気抵抗素子における磁場の漏洩をより抑制し、性能をより向上することが可能な半導体装置を提供する。

【解決手段】半導体基板は主表面を有する。磁気抵抗素子32は半導体基板の上記主表面上に位置する。配線43は上記磁気抵抗素子32上に位置する。バリア層41a、410は上記配線43の側面および上面を連続するように覆うように配置される。クラッド層41c、41dは上記バリア層41a、410の、配線43に対向する表面と反対側の表面を連続して覆うように配置される。上記磁気抵抗素子32と上記配線43と上記バリア層41a、410と上記クラッド層41c、41dとを含むメモリユニットが複数形成される。複数の上記メモリユニットが配線43の延在する方向に交差する方向に並列しており、複数のメモリユニット間でクラッド層41c、41dが分離されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】磁気抵抗素子における磁場の漏洩をより抑制し、性能をより向上することが可能な半導体装置を提供する。

【解決手段】下部電極31は、半導体基板100の主表面上に形成される。磁気抵抗素子32は、固定層35と、トンネル絶縁膜38と、自由層37とを含む。上部電極44は、自由層37のトンネル絶縁膜38と対向する一方の主表面と反対側に位置する他方の主表面上に配置される。磁気抵抗素子32を構成する固定層35は、下部電極31の一方の主表面上に配置された、磁化の方向が一定である層である。自由層37は、トンネル絶縁膜38の、固定層35と対向する一方の主表面と反対側に位置する他方の主表面上に配置された、磁化の方向が可変である層である。上記下部電極31、固定層35、トンネル絶縁膜38、自由層37、上部電極44の積層方向に交差する方向において、上部電極44の幅は、下部電極31および固定層35の幅よりも小さい。

(もっと読む)

垂直磁気トンネル接合構造体並びにそれを含む磁性素子、及びその製造方法

【課題】垂直磁気トンネル接合構造体並びにそれを含む磁性素子、及びその製造方法を提供することである。

【解決手段】本発明の垂直磁気トンネル接合は、上部磁性層及び下部磁性層のうちいずれか1層の磁性層に自由層を含み、トンネリング層と自由層との間に、分極強化層と交換遮断層とが積層されており、該交換遮断層は、非晶質の非磁性層であり、該分極強化層は、Fe層、体心立方(bcc)構造を有するFe系合金層、CoFeB系非晶質合金層、L21型ホイスラ(Heusler)合金層及びそれらの複合層のうちいずれか1層であり、該非晶質非磁性層は、ジルコニウム・ベース非晶質合金層、チタン・ベース非晶質合金層、パラジウム・ベース非晶質合金層、アルミニウム・ベース非晶質合金層及びそれらの複合層のうちいずれか1層であり、また該非晶質非磁性層は、全体的には非晶質であるが、局所的にはナノ結晶構造を有するものでありうる。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリに用いられる素子特性の劣化を抑制できる。

【解決手段】本発明の例に関わる抵抗変化メモリは、配線60と配線65との交点に設けられ、第1及び第2の端部の少なくとも一方にシリサイド層39を有する非オーミック素子30と抵抗状態の可逆的な変化に応じてデータを記憶するメモリ素子20とを含むセルユニットCUを具備し、シリサイド層39は、Si元素50とシリサイドを形成する少なくとも1種類の3d遷移金属元素51と、3d遷移金属元素51の原子半径r1より大きい原子半径r2を有する少なくとも1種類の添加元素52とを含む。

(もっと読む)

スピン注入型磁気ランダムアクセスメモリ

【課題】スピン注入型磁気ランダムアクセスメモリに関し、同じ面積でスイッチング電流Icの小さなMTJを用いてMulti−levelcell構造を構成するメモリを提供する。

【解決手段】フィルター層22,32が強磁性層23,33/非磁性層24,34/強磁性層25,35からなる反強磁性結合構造を有するとともに互いに異なったスイッチング電流特性を有する強磁性トンネル接合素子21,31を直列に複数個積層し、且つ、前記各強磁性トンネル接合素子21,31の平面面積を同じにする。

(もっと読む)

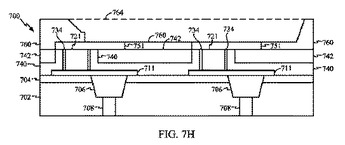

磁気トンネル接合デバイス及び製造

磁気トンネル接合(MTJ)デバイス及び製造方法が開示される。特定の実施形態では、底部電極(110、702)の上方に磁気トンネル接合構造(202)を形成することを含む方法が開示される。また、本方法は、磁気トンネル接合構造の上方及びこれに隣接する拡散障壁層(302、402)を形成することも含む。本方法は、拡散障壁層をエッチングバックして、磁気トンネル接合構造の上方の拡散障壁層を除去することを更に含む。また、本方法は、磁気トンネル接合構造の頂部 を導電層(604、704)に接続することも含む。  (もっと読む)

(もっと読む)

磁気トンネル接合を含む上部および下部電極を有するデバイスの製造および統合

電子デバイス製造プロセスは、下部電極層を堆積する段階を含む。次いで、電子デバイスが下部電極層上に製造される。下部電極層をパターニングする段階は電子デバイスを製造する段階後に、上部電極をパターニングする段階とは個別のプロセスで実施される。第1誘電体層は次いで、電子デバイスおよび下部電極層上に堆積され、上部電極層がそれに続く。上部電極は次いで、下部電極とは別のプロセスでパターン化される。上部および下部電極の別々のパターニングにより、電子デバイス間の誘電体材料におけるボイドが減少することによって収率が向上する。その製造プロセスが適切な1つの電子デバイスが、磁気トンネル接合(MTJ)である。  (もっと読む)

(もっと読む)

導電構造物を含む半導体装置及びその製造方法

【課題】容易に抵抗を調節することができ、高集積化が可能な導電構造物を含む半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板上に配置され、基板の導電領域を露出させる開口部を含む絶縁膜と、開口部内に配置されるバリア膜パターンと、バリア膜パターン上に配置され、開口部の外部に延長される酸化された部分及び開口部内に位置する酸化されなかった部分を含む導電パターンと、を具備し、導電パターンの幅がバリア膜パターンの厚さによって決定される。

(もっと読む)

半導体素子のパターン構造物形成方法

【課題】磁性物質又は相変化物質を含む半導体素子のパターン構造物の形成方法を提供する。

【解決手段】基板上に、磁性物質又は少なくとも3つの元素を含む合金からなった相変化物質のいずれか一つの物質を含むエッチング対象膜を形成する段階と、少なくともアンモニア(NH3)ガスを含むエッチングガスを使って前記エッチング対象膜をプラズマ反応性エッチングすることによってパターン構造物を形成する段階とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMを含む半導体装置において、MRAMの特性を向上することができる技術を提供する。

【解決手段】配線L3およびデジット配線DLを形成した層間絶縁膜IL3の表面に対してプラズマ処理を実施する。まず、半導体基板1Sをチャンバ内に搬入し、窒素を含有する分子(アンモニアガス)と窒素を含有しない不活性分子(水素ガス、ヘリウム、アルゴン)とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

(もっと読む)

磁気抵抗効果素子構造体、磁気ランダムアクセスメモリ、および、空間光変調器

【課題】素子作製時の加熱や、電流注入によって生じる熱等による磁気抵抗効果素子の特性劣化を防止することができる磁気抵抗効果素子構造体、この磁気抵抗効果素子構造体を用いた磁気ランダムアクセスメモリ、この磁気抵抗効果素子構造体を用いた空間光変調器を提供する。

【解決手段】固定層101と、中間層102と、反転層103とが積層された磁気抵抗効果素子10を有し、固定層101に、遷移金属と希土類金属との磁性合金、Mnを含む磁性合金、または、磁性多層膜のうちのいずれかを用いた磁気抵抗効果素子構造体1であって、磁気抵抗効果素子10の上面に設けられた上部電極11および磁気抵抗効果素子10の下面に設けられた下部電極12の間に、当該電極間を絶縁するための絶縁材13を備え、絶縁材13は、MgF2誘電体材料13aであり、MgF2誘電体材料13aは、固定層101の側面に当接して設けられていることを特徴とする。

(もっと読む)

半導体記憶装置

【課題】2つの選択トランジスタと1つの抵抗性記憶素子から成るメモリセルのレイアウト面積を縮小する。

【解決手段】半導体記憶装置は、それぞれが第1および第2のビット線から成り、且つカラム方向に延びる複数のビット線対と、各ビット線対に接続され、且つ複数のメモリセルから成るメモリセル群とを含む。各メモリセルは、第1のトランジスタT1、第2のトランジスタT2および抵抗性記憶素子10から成る。ロウ方向に隣接する2つのビット線対は、第1のビット線同士が共通接続され、もしくは第2のビット線同士が共通接続されて第1のカラムユニットを構成する。少なくとも片側の端部に配置される第1のビット線もしくは第2のビット線は、それと下層との接続部分よりも、第1のカラムユニットの中央寄りに配置される。

(もっと読む)

半導体装置

【課題】 スピン注入磁化反転を用いたメモリセルの読み出しディスターブを防ぎ、大電流で高速に読み出す。

【解決手段】 複数のワード線WLと、複数のビット線BLと、複数のメモリセルMCと、選択されたメモリセルから情報を読み出す読み出し回路SA,LAと、読み出し回路SA,LAが読み出した情報に基づいて、選択されたメモリセルに書き換えを行う書き換え回路WD1,WD2とを有し、読み出し回路SA,LAが選択されたメモリセルから情報を読み出す期間は、書き換え回路WD1,WD2が読み出し回路SA,LAが読み出した情報に基づいて選択されたメモリセルに情報を書き込む期間より短い。

(もっと読む)

201 - 220 / 536

[ Back to top ]