Fターム[4M119FF19]の内容

MRAM・スピンメモリ技術 (17,699) | コンタクト (2,004) | コンタクトの場所 (1,215) | 複数の配線間 (58)

Fターム[4M119FF19]に分類される特許

1 - 20 / 58

半導体磁気記憶装置

【課題】磁気記憶素子を構成する層を、周辺回路部内で有効に活用する。

【解決手段】実施形態によれば、半導体磁気記憶装置は、セルトランジスタを含むセル部と、周辺トランジスタを含む周辺回路部とが形成された半導体基板を備える。さらに、前記装置は、前記セル部内に配置され、下部電極と、前記下部電極上に形成された電極間層と、前記電極間層上に形成された上部電極とを含む磁気記憶素子を備える。さらに、前記装置は、前記周辺回路部内に配置され、前記下部電極を形成している第1の層と、前記電極間層を形成している第2の層と、前記上部電極を形成している第3の層とを含む構造体を備える。さらに、前記装置は、前記第1の層に電気的に接続された第1及び第2のプラグを備える。さらに、前記第1の層は、前記第1のプラグと前記第2のプラグを電気的に接続する配線として機能する。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】素子特性の劣化なしにリデポ現象による電気的ショートを防止する。

【解決手段】実施形態に係わる磁気抵抗効果素子は、磁化方向が可変の記憶層11と、記憶層11上のトンネルバリア層12と、トンネルバリア層12上の磁化方向が不変の参照層13と、参照層13上のハードマスク層14と、参照層13及びハードマスク層14の側壁上の側壁スペーサ層17とを備える。記憶層11及び参照層13は、垂直磁化を有し、参照層13の平面サイズは、記憶層11の平面サイズよりも小さい。記憶層11及び参照層13のサイズ差は、2nm以下であり、側壁スペーサ層17は、ダイアモンド、DLC、BN、SiC、B4C、Al2O3及びAlNのうちの1つを備える。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

磁気メモリ

【課題】書き込み時に固定層が安定化された、垂直磁化型トンネル磁気抵抗効果素子を用いたスピントルク磁化反転応用の磁気メモリを提供する。

【解決手段】膜面に垂直な方向の磁化を有する自由層62と、膜面に垂直な一方向に磁化が固定された固定層64と、固定層と自由層の間に形成された非磁性障壁層63を有する磁気抵抗効果素子において、互いに隣接したメモリセルの固定層を一列方向に接続する。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 セル面積を縮小させつつ、コストの増大を抑制する。

【解決手段】 実施形態による磁気ランダムアクセスメモリは、第1の方向Xに所定のピッチ2Fを有して配置され、第1の方向と直交する第2の方向Yに延在された第1及び第2のゲート電極GC1、GC2と、第1及び第2のゲート電極間の上方に配置された磁気抵抗素子MTJaと、磁気抵抗素子より高い位置に配置され、磁気抵抗素子と第1の方向にピッチの半分の距離Fを有して配置された電極層UE2と、電極層より高い位置に配置され、第1の方向に延在された配線M1と、磁気抵抗素子と配線との接続及び電極層と配線との接続を1つの導電層で行うビアV1Yと、を具備する。

(もっと読む)

集積回路装置及びその製造方法

【課題】ビアの形成が容易で抵抗が低い集積回路装置及びその製造方法を提供する。

【解決手段】相互に平行に配列された複数本の配線14a、14bと、各配線に接続されたビア16とを備える。配線におけるビアが接続された部分には、配列の方向に延出した凸部31が形成されており、配線における凸部が形成された部分から離隔した部分には、配列の方向に後退した凹部32が形成されている。隣り合う2本の配線において、一方の配線に形成された凸部と他方の配線に形成された凹部とは相互に対向している。各配線において、凹部が形成された部分はその両側の部分から切込33で分断されており、凸部が形成された部分からも分断されている。

(もっと読む)

磁気記憶素子および磁気記憶装置

【課題】半選択状態になった磁気記憶素子のデータの誤反転を抑制することにより信頼性の高い書き込み動作を行うことができる磁気記憶素子、およびこれを用いた磁気記憶装置を提供する。

【解決手段】磁化容易軸91と磁化困難軸92とを有する記録層3は、平面視においてすべての領域が第1導電層WTまたは第2導電層BLの少なくとも一方と重なる。磁化容易軸91に沿い、記録層3と平面視において重なる寸法が最大となる第1の線分の第1の端点TP,BPは、第2導電層BLと平面視において重ならない。上記第1の線分の中点を通り、平面視において第1の線分に直交し、記録層3と平面視において重なる第2の線分の1対の端点である第2の端点LP,RPのうち少なくとも一方は、第1導電層WTと平面視において重ならない。

(もっと読む)

磁気記憶装置

【課題】集積度が高い磁気記憶装置を提供する。

【解決手段】実施形態に係る磁気記憶装置は、基板と、前記基板上に設けられた複数個の磁気抵抗効果素子と、を備える。そして、前記複数個の磁気抵抗効果素子のうち、上方から見て互いに最も近い位置にある2個の磁気抵抗効果素子は、前記基板からの距離が相互に異なる。

(もっと読む)

磁気メモリ及びその製造方法

【課題】磁気抵抗素子間での電気的特性のバラツキを低減する。

【解決手段】磁気メモリの製造方法は、半導体基板20上のセルアレイ部に磁気抵抗素子37を形成する工程と、半導体基板20上の周辺回路部に、磁気抵抗素子37と同じ積層構造を有しかつ磁気抵抗素子37と同じレベルに配置されたダミー素子68を形成する工程と、磁気抵抗素子37及びダミー素子68を一括して平坦化する工程と、ダミー素子68にレーザー光線を照射し、ダミー素子68を非磁性体化する工程と、平坦化された磁気抵抗素子37上に上部電極41を形成する工程とを含む。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 界面磁性層が十分に結晶化された磁気ランダムアクセスメモリ及びその製造方法を提供する。

【解決手段】 実施形態に係る磁気ランダムアクセスメモリは、第1の磁性層、第1の界面磁性層、非磁性層、第2の界面磁性層、及び第2の磁性層が順に積層された磁気抵抗効果素子を有する。前記第1の磁性層の下層、前記第1の磁性層と前記第1の界面磁性層との間、前記第2の界面磁性層と前記第2の磁性層との間、及び前記第2の磁性層上のいずれかに第1の金属原子、第2の金属原子、及びB原子を含む金属層が設けられる。

(もっと読む)

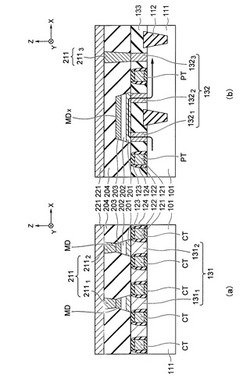

半導体装置及びその製造方法

【課題】積層ハードマスクを部分的に残存させつつ、配線層用のビアプラグのアスペクト比を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】基板上に第1の配線層102を形成し、第1の配線層102上に、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を順に形成し、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を含むピラー状の構造体を形成する。第1の配線層102上に、構造体の上面及び側面を覆うように、第3及び第4の絶縁膜109,106を形成し、第4の絶縁膜106を、第2の絶縁膜105が露出するように、部分的に除去する。第1及び第2の絶縁膜内に、半導体素子材料に接続された第1のビアプラグ107を形成し、第3及び第4の絶縁膜内に、第1の配線層102に接続された第2のビアプラグ108を形成し、第1及び第2のビアプラグ上に第2の配線層111を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ロジック混載MRAMにおいて、LSIの多層配線形成プロセスがMRAMの特性変動を引き起こす不都合、また、MRAMの形成プロセスが多層配線の特性変動を引き起こす不都合を軽減すること。

【解決手段】多層配線層に含まれる配線層Aの中に、配線層Bに形成された第1の配線104bに接し、互いに絶縁している少なくとも2つの第1の磁化固定層50a及び50bと、2つの第1の磁化固定層50a及び50bと平面視で重なり、かつ、第1の磁化固定層50a及び50bと接続している磁化自由層10と、磁化自由層10の上に位置する非磁性層40と、非磁性層40の上に位置する第2の磁化固定層104aと、を有するMRAMが形成されている半導体装置。

(もっと読む)

半導体記憶装置

【課題】 熱負荷によるTMR比の減少を抑制できる磁気抵抗効果を利用した半導体記憶装置を提供すること。

【解決手段】 実施形態の磁気抵抗素子は、非磁性元素を含む第1の垂直磁化磁性膜116と、第1の垂直磁化磁性膜上に設けられた絶縁膜119と、第1の垂直磁化磁性膜と絶縁膜との間に設けられた第1の中間磁性膜118と、絶縁膜上に設けられ、非磁性元素を含む第2の垂直磁化磁性膜123と、絶縁膜と第2の垂直磁化磁性膜との間に設けられた第2の中間磁性膜120と、第1の垂直磁化磁性膜と第1の中間磁性膜との間、および、第2の中間磁性膜と第2の垂直磁化磁性膜との間の少なくとも一方に設けられ、非磁性元素の拡散に対してバリア性を有する金属窒化物または金属炭化物で形成された拡散防止膜117,121を含む。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】データ消失温度が高く、かつ生産性の高い不揮発性記憶装置およびその製造方法を提供することである。

【解決手段】実施形態に係る不揮発性記憶装置の製造方法は、第1の記憶部と、第1の記憶部が有するデータ消失温度よりも高いデータ消失温度を有する第2の記憶部と、を有する不揮発性記憶装置の製造方法であって、第2の記憶部のメモリセルを形成するための第2の積層体を形成する工程と、第1の記憶部が形成される領域に形成された第2の積層体を除去する工程と、第1の記憶部のメモリセルを形成するための第1の積層体を形成する工程と、第2の記憶部が形成される領域に形成された第1の積層体を除去する工程と、第1の記憶部が形成される領域に形成された第1の積層体と、第2の記憶部が形成される領域に形成された第2の積層体と、を同時に処理して、第1の積層体から第1の記憶部のメモリセルを形成するとともに、第2の積層体から第2の記憶部のメモリセルを形成する工程と、を備えている。

(もっと読む)

半導体装置

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

半導体記憶装置

【課題】上部電極と第2のビット線との間のビアコンタクトの劣化を抑制し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板上に配置された複数の磁気トンネル接合素子と、複数の磁気トンネル接合素子の一端に電気的に接続された複数の選択トランジスタとを備える。第1のビット線が、各磁気トンネル接合素子の一端に1つまたは複数の選択トランジスタを介して接続されている。複数の上部電極は、複数の磁気トンネル接合素子の他端に接続されえいる。第2のビット線は、各磁気トンネル接合素子の他端に上部電極を介して接続されている。上部電極は、第2のビット線に沿って延伸しており第2のビット線の延伸方向に配列された複数の磁気トンネル接合素子の各他端に共通に接続されている。

(もっと読む)

半導体記憶装置

【課題】 スピン注入磁化反転を用いた磁性体メモリにおいて、微細な磁気抵抗素子を用いると書き込み電流が低減できるが、読み出し時のデータ破壊を防止するために読み出し電流も小さくする必要があり、読み出し動作の遅延につながる。

【解決手段】 ワード線(WL)が選択された後に、センスアンプ(SA)が活性化されて第1ビット線(BLt0)が第1電位(VDD)に、第2ビット線(BLb0)が第2電位(VSS)に駆動され、その後、ソース線(SL0)が第1電位から第2電位に駆動されることにより、時分割で反平行状態と平行状態の再書き込み動作を行う。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】不揮発性記憶装置およびその製造方法に関し、抵抗変化材料を利用したメモリの信頼性の向上を実現する。

【解決手段】積半導体素子を形成する基板の上方に、第1方向に延伸するように複数の金属配線層2を設け、金属配線層2のさら上方に、前記第1方向に直交する第2方向に延伸するように複数の金属配線層3を設ける。また、金属配線層2と金属配線層3とが交差する空間のそれぞれにメモリセルを設ける。前記メモリセルは、選択素子と相変化材料層7とが並列接続された構成とする。ここで、前記選択素子の前記第1方向の寸法が、相変化材料層7の前記第1方向の寸法よりも大きくなるように加工する。

(もっと読む)

半導体装置

【課題】 スピン注入磁化反転を用いたメモリにおいて、高速動作時の低電流書き換え動作を実現し、メモリセル毎のばらつきを抑え、読み出しディスターブを抑える。

【解決手段】 書き換え前に弱いパルスを与えてスピンの状態を不安定にし、書き換え電流を低減する。書き換え電流がパルス幅により非線形に大きくなる領域で読み出しを行い

、ディスターブを抑える。更に、ビット線電荷で注入スピン量を一定とした駆動方法によりばらつきを抑える。

(もっと読む)

1 - 20 / 58

[ Back to top ]