Fターム[4M119GG02]の内容

MRAM・スピンメモリ技術 (17,699) | レイアウト (382) | メモリセルアレイレイアウト (41)

Fターム[4M119GG02]に分類される特許

1 - 20 / 41

3次元半導体装置

【課題】増加された集積度を有し且つ高密度で高速の3次元(抵抗性)半導体(メモリ)装置を、最小限のマスク工程数で提供する。

【解決手段】チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時,前記選択ラインは平面形状及び平面位置において、前記水平電極の各々と実質的に同一であり得る。

(もっと読む)

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセル部及び周辺回路部を微細化する。

【解決手段】半導体基板20に設けられたメモリセル部11及び周辺回路部12を有する半導体記憶装置の製造方法であって、メモリセル部11及び周辺回路部12にそれぞれ層間絶縁層37及び47を形成する工程と、層間絶縁層37及び47上にそれぞれ、心材50を形成する工程と、心材50をスリミングする工程と、メモリセル部11及び周辺回路部12の心材50の側面にそれぞれ、側壁38及び48を形成する工程と、側壁38及び48をマスクとして、層間絶縁層37及び47を加工する工程と、加工された層間絶縁層37及び47内にそれぞれビット線BL及び配線層44を形成する工程とを含む。

(もっと読む)

集積磁気薄膜増強回路素子を有する磁気抵抗ランダムアクセスメモリ(MRAM)

不揮発性記憶装置およびその製造方法

【課題】不揮発性記憶装置およびその製造方法に関し、抵抗変化材料を利用したメモリの信頼性の向上を実現する。

【解決手段】積半導体素子を形成する基板の上方に、第1方向に延伸するように複数の金属配線層2を設け、金属配線層2のさら上方に、前記第1方向に直交する第2方向に延伸するように複数の金属配線層3を設ける。また、金属配線層2と金属配線層3とが交差する空間のそれぞれにメモリセルを設ける。前記メモリセルは、選択素子と相変化材料層7とが並列接続された構成とする。ここで、前記選択素子の前記第1方向の寸法が、相変化材料層7の前記第1方向の寸法よりも大きくなるように加工する。

(もっと読む)

薄膜磁性体記憶装置

【課題】製造時ばらつきに対応して、データ読出時における高い信号マージンを確保可能な薄膜磁性体記憶装置を提供する。

【解決手段】ダミーメモリセルDCPは、2個のセルユニットCU0およびCU1を含む。各セルユニットCU0,CU1は、メモリセルと同様の構成を有し、ビット線BLと接地電圧Vssとの間に直列に結合された、トンネル磁気抵抗素子TMRおよびアクセストランジスタATRを有する。セルユニットCU0,CU1に対しては、異なる記憶データ“0”および“1”がそれぞれ書込まれる。データ読出時において、2個のセルユニットCU0,CU1が、読出参照電圧Vrefを伝達するためのビット線BLと接地電圧Vssとの間に並列に接続される。さらに、ダミーメモリセルDCPに対して、電流供給回路52からメモリセルに供給されるセンス電流Isの2倍、すなわち2・Isの一定電流が供給される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板SSと、半導体基板SS上に形成され、周辺配線P1および配線L2が形成された配線層LL1,LL2と、配線層LL2に形成され、配線L3を含む配線層LL3と、配線層LL3上に形成され、磁気記憶素子MRを含む配線層LL4とを備え、配線L1,L2上に形成された拡散防止膜NF1,NF2は、SiCN膜またはSiC膜から形成され、配線L3上に形成された拡散防止膜NF3は、SiNから形成される。

(もっと読む)

半導体記憶装置

【課題】MRAMのメモリセル面積を縮小化する。

【解決手段】メモリセル80は、四角柱形状の素子形成領域100にメモリトランジスタTR1乃至3とTMR素子TMR1が設けられた3T1J型の3次元構造のメモリセルである。メモリトランジスタTR1のゲート電極5aが素子形成領域100の側面のA面及びB面に形成される。メモリトランジスタTR2はメモリトランジスタTR1の上部に設けられ、ゲート電極5bが素子形成領域100の側面のB面及びC面に形成される。メモリトランジスタTR3はメモリトランジスタTR2の上部に設けられ、ゲート電極5cが素子形成領域100の側面のC面に形成される。TMR素子TMR1は素子形成領域100上部に設けられる。B面のゲート電極5a及びゲート電極5bによりチャネル形成領域CH1が形成され、C面のゲート電極5b及びゲート電極5cによりチャネル形成領域CH2が形成される。

(もっと読む)

垂直ナノワイヤを備える情報保存装置

【課題】情報保存装置を提供する。

【解決手段】基板、基板上に垂直に配列された複数のナノワイヤを備え、複数のナノワイヤそれぞれは、情報を保存するための複数のドメインを有するメモリセルアレイ部、基板上に形成され、複数のナノワイヤのうち少なくとも一つを選択するナノワイヤ選択部、基板上に形成され、複数のナノワイヤのうち少なくとも一つに対してドメイン移動動作を制御するドメイン移動制御部、及び基板上に形成され、複数のナノワイヤのうち少なくとも一つに対する読み取り動作及び書き込み動作のうち少なくとも一つを制御する読み取り/書き込み制御部を備えるメモリセルである。

(もっと読む)

半導体記憶装置

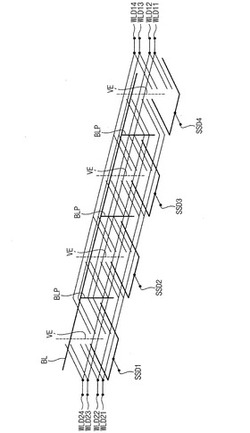

【課題】配線間の抵抗値を低減させる、クロスポイント型メモリセルを積層した多層構造の半導体記憶装置を提供する。

【解決手段】半導体基板1と、互いに交差する第1の配線WL及び第2の配線BL並びにこれら第1及び第2の配線の交差部で両配線間に接続されたメモリセルMCを有する1または複数のセルアレイ層MAと、セルアレイ層MAよりも下層の第1配線層M1に形成された第3の配線11と、セルアレイ層MAよりも上層の第2配線層M2に形成された第4の配線12と、第3の配線11及び第4の配線14を接続する積層方向に延びるコンタクト141〜144とを有する。第1配線層M1と第2配線層M2の間には、冗長配線層が形成される。冗長配線層には冗長配線131〜133が形成され、第3の配線11と冗長配線131〜133との間及び第4の配線12と冗長配線131〜133との間は、複数のコンタクト141〜144により接続される。

(もっと読む)

不揮発性記憶装置、集積回路装置及び電子機器

【課題】加工精度の向上等が可能な不揮発性記憶装置、集積回路装置及び電子機器を提供すること。

【解決手段】不揮発性記憶装置は、電気的に書き換え可能な不揮発性の複数のメモリーセル及び複数のビット線が配置される主記憶回路10と、電気的に書き換え可能な不揮発性の複数の情報メモリーセル及び複数のビット線が配置され、少なくとも主記憶回路10の不良メモリーセルのアドレス情報を記憶する情報記憶回路20と、主記憶回路10の複数のビット線のうちの対応ビット線と情報記憶回路20の複数のビット線のうちの対応ビット線との電気的接続をオン状態又はオフ状態にするための選択トランジスターが配置される選択回路30とを含み、情報記憶回路20は主記憶回路10と選択回路30との間に配置される。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】コストを抑えた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、ビット線BL0i〜BL2i、ビット線BL0i〜BL2iと交差するワード線WL0i、WL1i、及びビット線BL0i〜BL2i及びワード線WL0i、WL1iの交差部で両配線間に接続されたメモリセルMC0〜MC3を有する単位セルアレイMAT00を備える。さらに、不揮発性半導体記憶装置は、第1位置に設けられたビット線BL0iの側部に接し、第1位置よりも上方の第2位置に設けられたビット線BL1iまで積層方向に延びるコンタクトプラグCL1〜CL3と、第1位置と第2位置の間の第3位置に設けられたワード線WL0iの側部に接し、第2位置よりも上方の第4位置に設けられたワード線WL1iまで積層方向に延びるコンタクトプラグCL5、CL6とを備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】磁気ランダム・アクセス・メモリの書込に関連する回路のレイアウト面積を低減する。

【解決手段】可変磁気抵抗素子(VR)の磁化容易軸(EX)と直交する方向に書込ビット線(WBL0,WBL1)を配置し、書込データに応じて双方向に書込ビット線に電流を流す。一方、書込ビット線と交差するようにビット線(BL0−BL3)を配置し、書込データの論理値にかかわらず一定方向に電流を流す。書込ビット線へは、セルトランジスタ(CT)の耐圧よりも高い高電圧(VCC)から電流を供給する。

(もっと読む)

記憶装置

【課題】スピン注入メモリ等の抵抗変化素子を用いた記憶装置において、抵抗変化素子の高集積化を可能とした記憶装置を提供する。

【解決手段】供給される電流の向きにより抵抗値が変化する複数の抵抗変化素子と、各抵抗変化素子への電流供給をオン−オフ制御する複数のアクセス用トランジスタと、複数の抵抗変化素子の一方端に接続したビット線と、複数の抵抗変化素子の他方端にそれぞれアクセス用トランジスタを介して接続したソース線と、各アクセス用トランジスタのゲートにそれぞれ接続した複数のワード線と、接地電位が印加されるグランド線と、オン状態となることによりビット線またはソース線とグランド線とを接続するスイッチ用トランジスタとを備えた記憶装置とし、抵抗変化素子へ電流供給する際に、スイッチ用トランジスタをオン状態にして、ビット線またはソース線を接地電位にする。

(もっと読む)

抵抗変化型メモリ

【課題】セル面積の増加を抑制しつつ、書き込み電流を増大する。

【解決手段】抵抗変化型メモリは、第1の素子領域10と、第1の素子領域の上方に配置され、第1の方向Xにそれぞれ延在された第1及び第2のビット線BL1,BL2と、第1及び第2のビット線にそれぞれ接続された第1及び第2の抵抗変化素子MTJ1,MTJ2と、第1及び第2の抵抗変化素子の両方に直列接続され、第1の素子領域内に形成され、第1の方向と交差する第2の方向Yに延在された第1のゲート電極G1を有し、第1のゲート電極のゲート幅は第1の素子領域の第2の方向の幅と等しい第1のトランジスタTr1とを具備する。

(もっと読む)

不揮発性半導体記憶装置の読出回路

【課題】読出動作の高速化を図ることが可能な不揮発性半導体記憶装置を提供する。

【解決手段】このMRAMの比較回路10は、それぞれ電源電圧VDDのラインとノードN27,N28の間に接続されたトランジスタ27,28と、トンネル磁気抵抗素子TMRに電流を流すトランジスタ29と、参照電流を流すトランジスタ30と、ノードN27,N28の電圧を比較してデータ信号Q0を生成する差動増幅回路41と、電源電圧VDDを降圧してトランジスタ27,28のゲート電圧VGを生成するゲート電圧発生回路26とを備える。したがって、電源電圧VDDの上昇に伴うトランジスタ27,28の抵抗値の低下を抑制でき、ノードN27の電圧V27の振幅ΔVの低下を抑制できる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】ビット線とソース線の両方を同じ方向に延在するように形成する場合であっても、メモリセルの小型化を実現し得る半導体記憶装置及びその製造方法を提供する。

【解決手段】第1の方向延在する第1のワード線18a及び第2のワード線18bと、第1の方向に交差する第2の方向に延在し、ソース領域22bと平面視で重なり合い、第1の導体プラグ30を介してソース領域に接続されたソース線32と、第1のドレイン領域22aの上方に形成された第1の磁気抵抗効果素子40aと、第2のドレイン領域22cの上方に形成された第2の磁気抵抗効果素子40bと、ソース線よりも上層に形成され、第2の方向に延在し、第1の磁気抵抗効果素子及び第2の磁気抵抗効果素子に接続されたビット線70とを有している。

(もっと読む)

磁気記憶素子及び磁気記憶装置

【課題】反転電流の非対称性を解消し、素子破壊の可能性を低減した磁気記憶素子を実現し、高信頼性で低コストの磁気記憶装置を提供する。

【解決手段】第1固着層と第1中間層と記憶層と第2中間層と第2固着層が積層されてなり、第1固着層と第2固着層の磁化方向は層面に対し垂直で、第1固着層は、第2固着層から記憶層への漏洩磁界より大きな磁界を記憶層に及ぼすことを特徴とする磁気記憶素子が提供される。記憶層の第1中間層と面する膜の磁化方向と第1固着層の磁化方向との関係と、記憶層の第2中間層と面する膜の磁化方向と第2固着層との磁化方向との関係と、の一方が平行で他方が反平行となる。また、第1固着層と第2固着層の間に電流を双方向に流すことが可能で、電流の方向と値により記憶層の磁化の方向が変わる。また、磁気記憶素子をアレイ状に並べた磁気記憶装置が提供される。

(もっと読む)

半導体装置

【課題】レイアウト面積のさらなる削減を図ることが可能な半導体装置を提供する。

【解決手段】半導体装置は、主表面S1を有する基板SUBと、基板SUBの主表面S1から離間して配置され、データを記憶する記憶素子M1と、書き込み電流線DL<0>と、記憶素子M1にデータを書き込むためのデータ書き込み電流を書き込み電流線DL<0>に流し、基板SUBの主表面S1において形成される導通電極を有し、かつ記憶素子M1の下方に配置されるドライブトランジスタDLDTR0とを備える。

(もっと読む)

磁気半導体メモリ

【課題】高速動作が可能で、データ保持の信頼性が高い磁気半導体メモリを提供する。

【解決手段】本発明の磁気半導体メモリは、MTJ素子2を含むメモリセル1と、Y軸方向に延設された配線11、12とを具備する。配線11の中心線11aは、MTJ素子2から+X方向にずれており、且つ、配線12の中心線12aは、MTJ素子2から前記−X方向にずれている。

(もっと読む)

1 - 20 / 41

[ Back to top ]