Fターム[4M119HH02]の内容

MRAM・スピンメモリ技術 (17,699) | 回路技術 (628) | 書込回路 (191) | ドライバ (79)

Fターム[4M119HH02]に分類される特許

1 - 20 / 79

半導体装置の製造方法

半導体記憶装置

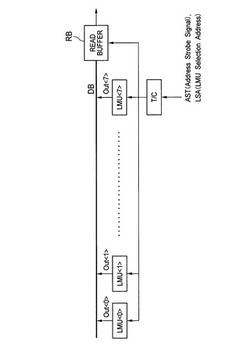

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を劣化させることなく、半導体材料または絶縁膜の結晶特性を改善することができる低温アニールを用いた半導体装置の製造方法、並びに、このような低温アニールに適した半導体装置を提供する。

【解決手段】本実施形態による半導体装置は、半導体基板の上方に設けられた金属からなる下部電極と、下部電極の上方に設けられた金属からなる上部電極と、下部電極と上部電極との間に設けられた結晶層とを備える。下部電極および上部電極の各膜厚は、結晶層の結晶化に用いられるマイクロ波の周波数に対応する表皮効果における表皮層よりも薄い。

(もっと読む)

半導体記憶装置

【課題】4個のトランジスタと2個のMTJ素子からなり、電源を印加しないでも不揮発性メモリとして動作するSRAMからなる半導体記憶装置を提供する。

【解決手段】第1及び第2のインバータ2,4と第1及び第2の転送用MOSFET3,5とを含むメモリセル1からなるSRAMにおいて、第1及び第2のインバータ2,4はスピン注入型のMTJ素子6,8と駆動用MOSFET7,9とからなり、これらのインバータ2,4からフリップフロップ回路が構成され、第1及び第2のインバータ2,4の出力端子は、それぞれ第1及び第2の転送用MOSFET3,5を介してビットライン及びビットラインバーに接続され、第1及び第2の転送用MOSFET3,5のゲートは、同一のワードラインに接続される。従来のSRAMに比較してメモリセルの面積が小さく、高速で低消費電力の不揮発性メモリが得られる。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

磁気メモリ

【課題】書き込み時に固定層が安定化された、垂直磁化型トンネル磁気抵抗効果素子を用いたスピントルク磁化反転応用の磁気メモリを提供する。

【解決手段】膜面に垂直な方向の磁化を有する自由層62と、膜面に垂直な一方向に磁化が固定された固定層64と、固定層と自由層の間に形成された非磁性障壁層63を有する磁気抵抗効果素子において、互いに隣接したメモリセルの固定層を一列方向に接続する。

(もっと読む)

磁気メモリ装置のためのライトドライバー回路、磁気メモリ装置及びそのレイアウト構造

【課題】本発明の技術的な課題は、共通ソースラインを含む磁気メモリ装置に対してビットラインへ記録電流を供給することができるライトドライバー回路を提供すること、集積度が向上された磁気メモリ装置を提供すること、及び、共通ソースラインを有する磁気メモリ装置のレイアウト構造を提供することにある。

【解決手段】ビットラインとソースラインとの間に接続され、前記ビットライン方向に隣接する一対の磁気メモリセルが前記ソースラインを共有する複数の磁気メモリセルよりなるメモリセルアレイを有する磁気メモリ装置のためのライトドライバー回路であり、正の記録電圧の供給端子と副の記録電圧の供給端子との間に接続されて、ライトイネーブル信号及びデータ信号によって前記正の記録電圧または前記副の記録電圧による電流を前記ビットラインに選択的に供給するスイチング部を備える磁気メモリ装置を提供する。

(もっと読む)

メモリセルおよび方法

【課題】マルチビット磁気ランダムアクセスメモリセルの不揮発性メモリセルのための装置およびプログラム方法を提供する。

【解決手段】第1の磁気トンネル接合(MTJ)192は、磁気フィルタ208を有する第2のMTJ192に隣接する。第2のMTJ192がプログラムされることを防ぐために第1の磁束212を磁気フィルタ208が吸収しつつ、第1の磁束212を用いて第1のMTJ192が第1の論理状態にプログラムされる。

(もっと読む)

半導体装置

【課題】正常な書込動作が実現できるセグメント書込み手法を用いた半導体装置を提供する。

【解決手段】第1および第2DLドライバ12a,12bは、それぞれ選択された1つのブロックのディジット線に磁化電流を流す。BLドライバ6は、データ信号の論理に応じた方向の書込電流を選択されたセグメント内の全ビット線に流して、選択されたブロックのメモリセルにデータ信号を書込む。セグメントデコーダ14は、外部から1個のセグメントのアドレスが入力されたときに、アドレスに対応する1個のセグメントを選択し、選択したセグメント第1DLドライバ12aへ接続し、外部から2個以上のセグメントのアドレスが入力されたときに、アドレスに対応する2個以上のセグメントを選択し、選択した2個のセグメントをそれぞれ第1DLドライバ12aと第2DLドライバ12bへ接続する。

(もっと読む)

薄膜磁性体記憶装置

【課題】製造時ばらつきに対応して、データ読出時における高い信号マージンを確保可能な薄膜磁性体記憶装置を提供する。

【解決手段】ダミーメモリセルDCPは、2個のセルユニットCU0およびCU1を含む。各セルユニットCU0,CU1は、メモリセルと同様の構成を有し、ビット線BLと接地電圧Vssとの間に直列に結合された、トンネル磁気抵抗素子TMRおよびアクセストランジスタATRを有する。セルユニットCU0,CU1に対しては、異なる記憶データ“0”および“1”がそれぞれ書込まれる。データ読出時において、2個のセルユニットCU0,CU1が、読出参照電圧Vrefを伝達するためのビット線BLと接地電圧Vssとの間に並列に接続される。さらに、ダミーメモリセルDCPに対して、電流供給回路52からメモリセルに供給されるセンス電流Isの2倍、すなわち2・Isの一定電流が供給される。

(もっと読む)

半導体装置

【課題】 スピン注入磁化反転を用いたメモリにおいて、高速動作時の低電流書き換え動作を実現し、メモリセル毎のばらつきを抑え、読み出しディスターブを抑える。

【解決手段】 書き換え前に弱いパルスを与えてスピンの状態を不安定にし、書き換え電流を低減する。書き換え電流がパルス幅により非線形に大きくなる領域で読み出しを行い

、ディスターブを抑える。更に、ビット線電荷で注入スピン量を一定とした駆動方法によりばらつきを抑える。

(もっと読む)

不揮発性記憶装置

【課題】電源投入後、高速なセットアップが可能な不揮発性記憶装置を提供する。

【解決手段】不揮発性記憶装置は、データを不揮発的に記憶するメモリセルを有する第1および第2のメモリモジュール16−1、16−2と、第1および第2のメモリモジュールとそれぞれ接続されて、前記第1および第2のメモリモジュールを駆動するための外部電源を供給する第1および第2の外部電源線VL11、VL12とを備え、第1の外部電源線の電源容量C1は、前記第2の外部電源線の電源容量C2よりも小さい。

(もっと読む)

不揮発性記憶装置、集積回路装置及び電子機器

【課題】過消去ビットの発生を抑制してエンデュランス特性等を向上させることができる不揮発性記憶装置、集積回路装置及び電子機器等を提供すること。

【解決手段】不揮発性記憶装置は、電気的に書き換え及び消去可能な複数の不揮発性メモリーセルM11〜M44を有するメモリーセルアレイと、複数の不揮発性メモリーセルのうちの消去対象メモリーセルに対する消去動作の制御を行う消去制御回路ERCNとを含む。消去制御回路ERCNは、消去対象メモリーセルが多い場合には、消去対象メモリーセルに対応するビット線BL1〜BL4がフローティング状態に設定される第1の消去動作制御を行う。消去対象メモリーセルが少ない場合には、消去対象メモリーセルに対応するビット線BL1〜BL4が低電位電源電圧VSSに設定される第2の消去動作制御を行う。

(もっと読む)

磁気抵抗効果素子、それを用いた磁気メモリセル及びランダムアクセスメモリ

【課題】垂直磁化材料を適用し、TMR比の高い磁気抵抗効果素子を提供する。

【解決手段】CoFeB層41/MgOバリア層10/CoFeB層42の外側に融点が1600℃以上の単体金属、もしくはその金属を含んだ合金からなる中間層31,32を挿入する。中間層31,32の挿入により、アニール時におけるCoFeB層の結晶化をMgO(001)結晶側から進行させ、CoFeB層をbcc(001)で結晶配向させる。

(もっと読む)

半導体装置

【課題】 スピン注入磁化反転を用いたメモリセルの読み出しディスターブを防ぎ、大電流で高速に読み出す。

【解決手段】 複数のワード線WLと、複数のビット線BLと、複数のメモリセルMCと、選択されたメモリセルから情報を読み出す読み出し回路SA,LAと、読み出し回路SA,LAが読み出した情報に基づいて、選択されたメモリセルに書き換えを行う書き換え回路WD1,WD2とを有し、読み出し回路SA,LAが選択されたメモリセルから情報を読み出す期間は、書き換え回路WD1,WD2が読み出し回路SA,LAが読み出した情報に基づいて選択されたメモリセルに情報を書き込む期間より短い。

(もっと読む)

半導体集積回路

【課題】リードワード線およびライトワード線のドライブ回路を分割配置してレイアウト面線を減少させる。

【解決手段】

磁性体メモリセルMCは、メモリアレイに行列状に配置される。リードワード線RWL1〜RWLnおよびライトビット線WBL1〜WBLnは、磁性体メモリセルの行に対応して配置される。ライトワード線WWL1〜WWLmおよびリードビット線RBL1〜RBLmは、磁性体メモリセルの列に対応して配置される。この結果、リードワード線ドライバ30rおよびリードワード線ドライバ30wは、メモリアレイに対して異なる方向に隣接するように分割配置することができる。

(もっと読む)

スピン移動トルクランダムアクセスメモリのための階層状データ経路を提供する方法およびシステム

磁気メモリを提供する方法およびシステムについて記載する。本方法およびシステムは、メモリアレイタイル(MAT)、中間回路要素、グローバルビット線、グローバルワード線、およびグローバル回路要素を提供することを含む。各MATは、磁気記憶セル、ビット線、およびワード線を含む。磁気記憶セルはそれぞれ、少なくとも1つの磁気素子および少なくとも1つの選択デバイスを含む。磁気素子は、磁気素子を通して駆動される書込み電流を使ってプログラム可能である。ビット線およびワード線は、磁気記憶セルに対応する。中間回路要素は、MAT内の読取りおよび書込み動作を制御する。各グローバルビット線は、複数のMATの第1の部分に対応する。各グローバルワード線は、MATの第2の部分に対応する。グローバル回路要素は、読取りおよび書込み動作のために、グローバルビット線の一部およびグローバルワード線の一部を選択し駆動する。  (もっと読む)

(もっと読む)

薄膜磁性体記憶装置

【課題】磁気トンネル接合部(MTJ)を有するメモリセルを用いてデータ記憶を行なう薄膜磁性体記憶装置において、データ読出動作を高速化する。

【解決手段】MTJメモリセルに対しては、データ書込およびデータ読出にそれぞれ用いられるライトワード線WWLおよびリードワード線RWLが独立して設けられる。メモリアレイ10を列方向に分割して形成される領域AR1,AR2ごとにリードワード線RWLを分割配置することによって、リードワード線RWLにおける信号伝搬遅延を低減して、データ読出動作を高速化できる。各リードワード線RWLの活性化は、行選択結果に応じてライトワード線WWLと階層的に制御される。ワード線電流制御回路40は、データ書込時およびデータ読出時のそれぞれに対応して、ライトワード線WWLにおける電流経路を形成および遮断する。

(もっと読む)

半導体装置

【課題】MTJメモリセルを有するMRAMデバイスにおいて、データ読出動作の高速化および、配線層数の減少による製造コスト低減を図る。

【解決手段】MTJメモリセルは、記憶データのデータレベルに応じて抵抗値が変化する磁気トンネル接合部MTJと、アクセストランジスタATRとを備える。アクセストランジスタATRのゲートはリードワード線RWLと結合される。ビット線BLは、磁気トンネル接合部MTJと直接結合されず、アクセストランジスタATRを介して磁気トンネル接合部MTJと電気的に結合される。磁気トンネル接合部MTJは、ライトワード線WWLおよびアクセストランジスタATRの間に結合される。データ読出時において、ライトワード線WWLの電圧は接地電圧Vssに設定されて、データ読出のための電流経路が形成される。さらに、ライトワード線WWLは、ビット線BLよりも上層側に形成される。

(もっと読む)

メモリ及び情報処理方法

【課題】不良が発生した記憶素子から情報を読み出す場合に、書き込まれるべき情報を正しく読み出すこと。

【解決手段】SpRAM1は、1ビットの情報を記憶する記憶素子2と、記憶素子2に書き込まれた情報を読み出すセンスアンプ10を備える。センスアンプ10は、所定の単位数の記憶素子2を有する記憶ブロックの内、特定の1個の記憶素子2を反転フラッグ素子として定める。そして、センスアンプ10は、反転フラッグ素子に書き込まれた1ビットの情報が、“0”又は“1”の内、いずれかを示す第1の値である場合に、他の記憶素子2に書き込まれた所定の単位数−1ビットの情報をビット反転して読み出す。一方、反転フラッグ素子に書き込まれた1ビットの情報が、第1の値とは異なる第2の値である場合に、他の記憶素子2に書き込まれた所定の単位数−1ビットの情報をそのまま読み出す。

(もっと読む)

1 - 20 / 79

[ Back to top ]