Fターム[5B001AA03]の内容

Fターム[5B001AA03]の下位に属するFターム

CRC (48)

SECDED (15)

ブロック符号 (8)

Hマトリックス (4)

多項式 (6)

エラーポインタ (1)

たたみ込み符号 (37)

BCH、リードソロモン (44)

ファイア符号

特殊符号 (55)

Fターム[5B001AA03]に分類される特許

1 - 20 / 54

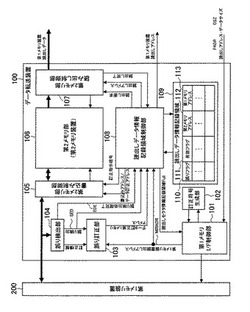

データ転送装置、メモリ制御装置、およびメモリシステム

【課題】誤り訂正が発生したとしてもデータ伝送が待たされる時間を少なくし、データ転送に要する時間を短縮することが可能なデータ転送装置、メモリ制御装置、およびメモリシステムを提供する。

【解決手段】データ転送元の第1メモリ装置200の第1メモリアドレスと、データ転送先の第2メモリ装置の第2メモリアドレスと、転送データに誤りが検出されたか否かを示す誤り信号と、誤り訂正が完了して第2メモリ装置106に格納しているデータが有効であるか否かを示す有効信号を記憶する領域を複数含むデータ情報記憶領域109と、第2メモリ装置に格納しているデータのうち、データが有効であるメモリのアドレスである第2メモリ有効アドレスを出力し、第2メモリ装置の第2メモリ有効アドレスからデータを読出し、読出したデータと共に、第2メモリ有効アドレスに対応する第1メモリ装置のアドレスを転送する制御部108とを有する。

(もっと読む)

エラー訂正回路及びエラー訂正方法

【課題】固定的に生じているエラーを含む場合は、訂正能力を超えて訂正を行う。

【解決手段】エラー訂正回路は、入力データに含まれるエラーの種別を判別する第1のエラー検出回路1と、エラー種別が1バイトエラーか、2バイトエラーである場合に、当該エラーが特定のバイトに固定的に発生している固定エラーであるか否かを判定する固定エラー検出回路2と、2バイトエラーに固定エラーが含まれる場合に、固定エラーが発生しているバイトの代わりとなる代替バイトを繰り返し発生するデータ発生回路4と、2バイトエラーに固定エラーが含まれる場合に、代替バイトで固定エラーが発生しているバイトを置き換えて、2バイトエラーが1バイトエラーとなるまで誤り検出を繰り返す第2のエラー検出回路3と、第2のエラー検出回路3で入力データが1バイトエラーとなったことを検出したら、当該入力データのエラー訂正を実行するエラー訂正回路5とを有する。

(もっと読む)

NANDフラッシュ・メモリにおける確率論的多層エラー訂正のためのシステム、方法、およびコンピュータ・プログラム

【課題】メモリからデータを検索するためのシステム、方法、およびコンピュータ・プログラムを提供する。

【解決手段】メモリからデータを検索するためのシステムを含むNANDフラッシュ・メモリにおけるエラー訂正。このシステムは、メモリと通信するデコーダを含む。デコーダは、メモリにおけるページ上に記憶されたコードワードを受信することを含む方法を実行するためのものであり、コードワードは、データおよびこのデータに応じて発生された第1の層のチェック・シンボルを含む。この方法は更に、コードワードが第1の層のチェック・シンボルを用いて訂正することができないエラーを含むと判定することを含み、これに応じて、第2の層のチェック・シンボルを受信する。第2の層のチェック・シンボルは、データの受信に応じて、更にコードワードを含むページよりも前に書き込まれたメモリにおける他のページの内容に応じて発生させる。第2の層のチェック・シンボルに応じてコードワードを訂正する。訂正したコードワードを出力する。

(もっと読む)

データ障害処理装置、及びデータ障害処理方法

【課題】繰り返しの障害発生を回避してプロセッサリリーフを実現するデータ障害処理装置、及びデータ障害処理方法を提供すること

【解決手段】データ障害処理装置は、誤り訂正機能を持つ記憶装置に格納されたデータにアクセスするプロセッサ3を備える。記憶装置は、データ供給時にデータに対して誤り訂正符号を付与する。障害識別部302は、誤り訂正符号に基づいて、前記記憶装置から供給されたデータに障害が発生しているか否かを識別する。事前評価部305は、訂正不可能障害が生じたデータが格納されたアドレスに再度アクセスする事前評価リクエストを発行する。救済可否判定部306は、前記事前評価リクエストの発行結果に応じてプロセッサリリーフが実行可能かを判定する。障害処理部307は、救済可否判定部の判定に応じて障害対応処理を行う。

(もっと読む)

データ処理回路及びデータ処理方法

【課題】データの処理時間を短縮するデータ処理回路及びデータ処理方法を提供する。

【解決手段】制御用ビットを含むデータを受信する受信回路211と、受信回路211から出力されたデータを保持する保持回路215と、受信回路211から出力されたデータのエラーを検出するエラー検出回路212と、エラー検出回路212により検出された制御用ビットのエラーである第1エラーを訂正する第1訂正回路と、エラー検出回路212で第1エラーが検出されないときは、保持回路215を経由したデータを出力し、エラー検出回路212で第1エラーが検出されたときは第1エラーが訂正されたデータを出力する出力選択回路と、を有する。

(もっと読む)

障害処理方法および計算機

【課題】障害データが読み出しされることによってシステムを停止させるCPUを備える計算機システムにおいて、障害データに対するユーザソフトウェアのアクセス状況に基づいて障害範囲を限定する。

【解決手段】プロセッサと、プロセッサに接続されるメモリとを備える計算機における障害処理方法であって、プロセッサは、メモリ保護機能を備え、第1のソフトウェアと第1のソフトウェアの実行を監視する第2のソフトウェアとを実行し、第2のソフトウェアはアドレス情報とアクセス関連情報とを含む障害情報を保持し、方法は、第2のソフトウェアが、メモリにおける障害の発生を検出するステップと、障害が発生したメモリのアドレスへのアクセスを禁止し、アクセス状況を監視するステップと、障害が発生したメモリのアドレスに対する第1のソフトウェアからのアクセスを検出した場合に障害処理を実行するステップと、を含むことを特徴とする。

(もっと読む)

情報処理装置および情報処理方法

【課題】動作に重要なプログラムが書き込まれているフラッシュROM上の物理的な記憶領域のデータが不良になっている場合にもプログラムを実行できるようにする。

【解決手段】この情報処理装置は、複数のカラムを一単位とするブロック単位にデータを記憶可能な物理的な記憶領域を有するフラッシュメモリと、プログラムデータを複数のブロックに分けて前記物理的な記憶領域に書き込み、各ブロックに付与した第1のエラー訂正符号を前記物理的な記憶領域に書き込み、前記プログラムデータに付与した第2のエラー訂正符号を前記フラッシュメモリに書き込む書き込み装置とを備える。

(もっと読む)

メタデータタグを介した不規則なパリティ分布の検出

情報処理装置、情報送信方法および情報受信方法

【課題】通常の情報伝送動作中にバスの故障診断を実行できるようにする。

【解決手段】送信側デバイス10と受信側デバイス20とは、送信データとこの送信データに基づくエラー訂正符号とがパラレル送信されるパラレルバス30を通じて接続されている。送信側デバイス10は、パラレルバス30に送信する信号を反転する信号反転部11を有する。受信側デバイス20は、パラレルバス30からの受信信号を反転する信号反転部21と、信号反転部21から出力された信号を基にエラー検出処理とエラー訂正処理とを実行するエラー検出部22とを有する。信号反転部11によってすべてのバスに送信する信号が反転され、信号反転部21によってすべてのバスから受信した信号が反転されることで、エラー検出部22においてパラレルバス30の故障診断が行われる。

(もっと読む)

演算処理装置、情報処理装置および演算処理装置の制御方法

【課題】演算処理装置において、読み出されたデータのエラーを検出してからエラーを訂正して通常の動作状態に復帰するまでの時間を短縮すること。ハードウェアの量を減らすこと。

【解決手段】チェック部43が記憶部33の出力データのエラーを検出すると、演算制御部31はエラー検出信号EU_PDを出力する。演算制御部31は、記憶部33にエラーが発生したことを示すエラー識別信号GPR_DATA_ERRORを出力する。命令制御部36は、エラー検出信号およびエラー識別信号に基づいてキャンセル信号CANCELおよび訂正開始信号CORRECT_STARTを出力する。演算処理装置12は、キャンセル信号によって演算部32の動作を停止し、エラーの報告処理を開始する。演算処理装置12は、訂正開始信号によってエラー訂正部34でのエラーの訂正処理を開始する。エラーの訂正処理はエラーの報告処理と並行して行われる。

(もっと読む)

プロセッサ

【課題】アドレス比較回路等を不要にしてフォワーディング回路の規模を小さくして、半導体チップ上のフォワーディング回路の占める面積の小さいプロセッサを提供する。

【解決手段】プロセッサ1は、ALU11と、ロード/ストアユニット13と、タイマ13aと、ECC計算器13bと、複数のECCレジスタ13cと、を有する。ロード/ストアユニット13は、主メモリ14にデータを書き込む時に、書き込みデータとタイマ13aのカウント値とを主メモリ14に書き込むと共に、その書き込みデータについてのECCが正しくないことを示すECC状態フラグデータを主メモリ14にセットし、そのセット後、ECC計算器13bに書き込みデータについてのECCを計算させ、ECCが計算して得られた後、その計算して得られたECC主メモリ14に書き込むと共に、ECC状態フラグデータをリセットする。

(もっと読む)

情報伝送装置

【課題】安全性が要求される鉄道保安システムにおいても安全性を維持して誤り訂正符号を導入して情報を伝送してシステムの稼働率は向上させる。

【解決手段】地上装置1の送信機5は、入力した送信データに誤り訂正符号を付加して送信語を生成して通信路8に送信する。車上装置3の受信機6は、通信路8から受信した受信語に対してシンドロームを計算し、計算したシンドロームを用いて受信語の誤り訂正処理を行う。また、計算したシンドロームを用いて誤り訂正の状況を評価し、誤り訂正の状況があらかじめ設定された基準状態より良好な場合に誤り訂正処理をした受信データの出力を許可し、誤り訂正の状況があらかじめ設定された基準状態より悪くなっているとき誤り訂正処理をした受信データの出力を禁止する。

(もっと読む)

DRAMバッファ管理装置および方法

【課題】別途のデバイスを追加することなく、DRAMバッファにエラー訂正コードを適用することのできるDRAMバッファ管理装置および方法を提供すること。

【解決手段】DRAMバッファ管理装置およびDRAMバッファ管理方法が開示される。当該DRAMバッファ管理装置およびDRAMバッファ管理方法においては、DRAMバッファに記録されるデータに対するエラー訂正コードを生成し、前記データおよび前記ECCを前記DRAMバッファに記録する。  (もっと読む)

(もっと読む)

データ保護回路及び方法、並びにデータ処理装置

【課題】誤り検出符号の変換過程において十分なデータ保護を行う。

【解決手段】データ保護回路4内の生成部100_1は、入力データD1inを、これを出力データD1outとして出力するための経路(P2→P4→P10→P13)上の一の箇所(例えば、P2とP4の接続ノード)から取得し、第2の誤り検出符号(例えば、ECC C1)を生成する。検査部200_1は、入力データD1inを、前記経路上の生成部100_1の取得箇所よりも出力側に近い他の箇所(例えば、P10とP13の接続ノード)から取得し、第1の誤り検出符号(例えば、パリティC2)を用いて入力データD1inの検査を行う。また、接続部300_1は、入力データD1inが生成部100_1に次いで検査部200_1により取得されるよう、生成部100_1の取得箇所(P2とP4の接続ノード)と検査部200_1の取得箇所(P10とP13の接続ノード)とを接続する。

(もっと読む)

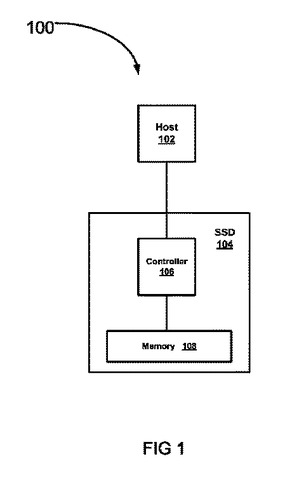

ソリッドステートディスクにおける改良された誤り訂正

いくつかの実施例では、ソリッドステートディスクは、不揮発性メモリとコントローラとを有する。コントローラは、不揮発性メモリに格納されているデータに対してECCを実行し、ECCがデータを訂正できない場合、データに対してパリティ処理を実行する。他の実施例が開示及び請求される。  (もっと読む)

(もっと読む)

ポイズン・ビット・エラー検査コード手法

一実施例では、方法は、イベントの生起及び非生起の何れかを判定する工程であって、生起及び非生起の何れかがイベント判定をもたらす工程と、イベント・ビットを有するコードを処理する工程であって、上記処理は、イベント・ビットがイベント判定に対応するかを判定することにより、判定及びコードに応じる工程と、イベント・ビットがイベント判定に対応しない場合、イベント判定に対応するポイズン・ビットを生成するようコードをコード化する工程とを提供する。  (もっと読む)

(もっと読む)

情報処理装置

【課題】フラッシュメモリのプログラムをRAMに展開して使用する場合、エラーの原因がいずれのメモリにあるのか特定できない。

【解決手段】情報処理装置10は、プログラムコードとこのプログラムコードの読み出し誤りを訂正するための第1の誤り訂正符号とを記憶するフラッシュメモリ25と、このメモリ25から読み出されたプログラムコード及び第1の誤り訂正符号を記憶するRAM26と、このRAM26に記憶されたプログラムコードを実行するCPU21とを備えている。CPU21は、RAM26に記憶されたプログラムコードに基づいて第2の誤り訂正符号を算出する誤り訂正符号算出機能と、RAM26に記憶された第1の誤り訂正符号と前記誤り訂正符号算出部により算出された第2の誤り訂正符号とに基づいてメモリ25及びRAM26の記憶不良の有無を判定する判定機能とを有している。

(もっと読む)

エラー訂正方式及びエラー訂正方法

【課題】データに対するチェックデータの比率を大きくすることなく、ソフトエラーに起因するデータの2ビットエラーを訂正できるようにする。

【解決手段】チェックデータ生成部31は、データDに対するチェックデータCを生成し、チェックデータメモリ2に格納する。また、データDは、チェックデータメモリ2とは別のデータメモリ1に格納する。このように、データDとチェックデータCと物理的に異なるメモリ1、2に格納することにより、ソフトエラーに起因してデータDとチェックデータCとの両方に同時に1ビットエラーが発生する確率を無視できるほど小さくすることができる。この結果、上記パターンのビットエラーを訂正するためのエラー訂正機能をチェックデータに組み込まなくとも良くなるので、チェックデータCのビット数を少なくすることができる。

(もっと読む)

情報処理装置、エラー訂正方法及びプログラム

【課題】ECCによる訂正可能なビット数以上のエラー訂正を行うことを可能にする。

【解決手段】本発明によるエラー訂正方法は、記憶領域からデータを読み込んだ際、誤り訂正符号を用いてビットエラーの検出を行い、また、前記ビットエラー検出ステップにより検出されたビットエラーの場所及び正しい値の情報を含むビットエラー情報を所定の代替領域に書き込む。次に前記記憶領域からデータを読み込んだ際(ステップS101)、前記代替領域を検索して前記ビットエラー情報があると判断する場合に(ステップS102/ある)前記ビットエラー情報に基づきデータを修正する(ステップS104)。

(もっと読む)

仮想化ECC−NAND

単一の仮想化ECC-NANDコントローラが、ECCアルゴリズムを実行し、NANDフラッシュ・メモリのスタックを管理する。この仮想化ECC-NANDコントローラは、スタック内の選択されたNANDメモリ・デバイスにデータをリダイレクトし、その一方で、ホスト・プロセッサがフラッシュ・メモリ・デバイスのスタックを単一のNANDチップとして駆動することを可能にする。  (もっと読む)

(もっと読む)

1 - 20 / 54

[ Back to top ]