Fターム[5B001AA04]の内容

Fターム[5B001AA04]に分類される特許

1 - 20 / 48

ICカード及びプログラムコードの診断方法

【課題】 プログラムコードの自己診断によって特定のコマンド処理に不具合が発生すること、あるいはプログラムコード自己診断の実行が不十分となることを回避することのできるICカード及びプログラムコードの診断方法を提供する。

【解決手段】 外部からのコマンドを解釈実行し、その結果を応答するICカード(1)において、ICカードで実行されるプログラムを格納するプログラム領域(104)と、外部からコマンドを受信する受信部(13)と、コマンドに対応した処理、及びプログラム領域内のプログラムについてプログラムコードの良否診断処理を実行する制御部(101)とを有し、制御部は、プログラムコードの良否診断を、受信部が所定のコマンドを受信する毎の複数回に分割して実行し、分割された良否診断を実行した後で当該所定のコマンドの処理を実行するICカードである。

(もっと読む)

CRC演算回路及びプロセッサ

【課題】少ない処理段数でCRC演算を行うことができるCRC演算回路を提供することを課題とする。

【解決手段】CRC演算回路は、第3のデータのうちの最上位ビットのデータと、第4のデータとの排他的論理和を演算する第1の排他的論理和回路(1403)と、第3のデータのうちの最上位ビットのデータと、第1のデータとの論理積を演算する複数の第1の論理積回路(1401)と、複数の第1の論理積回路の出力データと、第3のデータのうちの最上位ビット以外のデータとの排他的論理和を演算する複数の第2の排他的論理和回路(1402)と、第1の排他的論理和回路の出力データと、第2のデータとの論理積を演算する複数の第2の論理積回路(1404)と、複数の第2の排他的論理和回路のうちの一部の出力データと、複数の第2の論理積回路のうちの一部の出力データとの論理和を演算する複数の論理和回路(1405)とを有する。

(もっと読む)

アドレス変換検査装置、中央処理演算装置、及びアドレス変換検査方法

【課題】メモリ管理装置に設けられたバッファに読み込まれた変換テーブルを用いて、中央処理演算装置が物理メモリへ正常にアクセスできるか否かを他のプログラムを実行したままで検査する。

【解決手段】情報処理装置10は、物理メモリのアドレスである物理アドレスと仮想メモリのアドレスである仮想アドレスとを変換するための変換テーブルに基づいて、前記仮想アドレスと前記物理アドレスとを変換するMMU20を備えている。そして、RAM14には、ページテーブルを示すページテーブル情報、及びページテーブル情報に付加され、MMU20による仮想アドレスと物理アドレスとの変換の異常の有無を検出するための異常検出情報が記憶されている。そして、CPU12は、異常検出情報に基づいて、MMU20による仮想アドレスと物理アドレスとの変換の異常の有無を検出する。

(もっと読む)

冗長化制御システム、及びその演算データの伝送方法

【課題】受信側で伝送誤り検出と、冗長系毎の演算データの誤りと故障診断とを可能とした冗長化制御システムの演算データの伝送方法を提供することを目的とする。

【解決手段】第1の演算データを生成し、返信時の誤り検出用の第1の生成アルゴリズムを使用して第1の生成データを生成するステップと、第2の演算データを生成し、誤り検出用の第2の生成アルゴリズムを使用して第2の生成データを生成するステップと、相互に第1/第2の演算データとを比較照合するステップと、一致した演算データと、第1/第2の生成データとを含む伝送データを送信するステップと、受信装置では、演算データと予め設定された第1/第2の生成アルゴリズムとから第3/第4の生成データとを生成するステップと、第1/第3の生成データとを、また、第1/第3の生成データとを比較照合して、受信した演算データの誤りを検出するステップとを備えた演算データの伝送方法。

(もっと読む)

判定装置及び判定方法

【課題】複数のデータ処理回路を備える半導体集積回路の不具合箇所を特定することができる判定装置を提供すること。

【解決手段】本発明の一態様に係る判定装置は、第1OSDプレーン23A及び第2OSDプレーン23B、ビデオプレーン23Cを備えるLSI20Aの良否判定を行うものである。入力されるテストパターンに応じて複数の画像処理回路が形成する1フレームの画像において、第1OSDプレーン23Aからの出力に対応する領域Aと、第2OSDプレーン23Bからの出力に対応する領域BとをCRC演算する領域として設定する。CRC演算回路15は、領域A、領域BのCRC演算を行ってそれぞれの演算結果を算出し、それぞれの領域に対応する期待値と演算結果とをそれぞれ比較して、複数のデータ処理回路の良否判定を行うCPU22に出力する。

(もっと読む)

エラー訂正装置、エラー訂正装置のメモリの制御方法および光ディスク記録再生装置

【課題】エラー訂正時に使用されるメモリ容量の増大を低減させる。

【解決手段】エラー訂正装置(35)は、メモリ(351)と、エラー訂正部(357)とを有する。メモリは、格納済みの第1ブロックデータが有する複数のフレームデータを行方向に順次読み出し、読み出しに連動して読み出し後の空き領域に第2ブロックデータが有する複数のフレームデータを行方向に順次格納する第1動作と、第1動作で格納した第2ブロックデータが有する複数のフレームデータを列方向に順次読み出し、読み出しに連動して読み出し後の空き領域に第1ブロックデータが有する複数のフレームデータを前記列方向に順次格納する第2動作とを交互に行う。

(もっと読む)

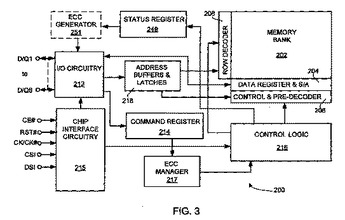

メモリコントローラ及び方法におけるデータ完全性

本開示は、メモリコントローラでのデータ完全性のための方法、装置、及びシステムを含む。1つのメモリコントローラの実施形態は、ホストインタフェース、及びホストインタフェースに結合される第1のエラー検出回路を含む。メモリコントローラは、メモリインタフェースと、メモリインタフェースに結合される第2のエラー検出回路を含むことができる。第1のエラー検出回路は、ホストインタフェースから受信されるデータに対してエラー検出データを計算し、ホストインタフェースに送信されるデータの完全性をチェックするように構成できる。第2のエラー検出回路は、メモリインタフェースに送信されるデータ及び第1のエラー訂正データに対してエラー訂正データを計算し、メモリインタフェースから受信されるデータ及び第1のエラー訂正データの完全性をチェックするように構成できる。 (もっと読む)

冗長化制御装置

【課題】 冗長化されたコントローラ間の診断通信に失敗が発生した場合に、故障箇所を特定することを可能とする冗長化制御制御装置を実現する。

【解決手段】 第1コントローラ及び第2コントローラが、シリアルバスを介して相互に通信すると共に、通信バスを介して上位装置と通信し、各コントローラは診断フレームを自側より相手側コントローラに送信するトランシーバーと相手側から送信された診断フレームを受信するレシーバーを具備する冗長化制御装置において、

前記第1コントローラ及び第2コントローラは、

自側トランシーバーの送信データのフィードバックチェック手段と、

相手側からの受信データに対する1ビット誤りまたは多ビット誤りを検出する、誤り検出手段と、

を備える。

(もっと読む)

エラー検出方法および1つまたは複数のメモリデバイスを含むシステム

1つまたは複数のメモリデバイスを含むシステムと、エラーの検出および訂正の方法とが開示される。システムのメモリデバイスが、パケットを受信するための入力を含む。パケットの第1の部分は、少なくとも1つのコマンドバイトを含むことが可能であり、パケットの第2の部分は、コマンドエラー検出を容易にするパリティビットを含むことが可能である。メモリデバイスは、パリティビットに基づいて、エラーが少なくとも1つのコマンドバイト内に存在するかどうかを検出するように構成されているエラーマネージャと、パケットをエラーマネージャに供給するように構成されている回路とを含むことが可能である。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の制御方法および半導体装置の制御プログラム

【課題】本発明は、レーザー攻撃による誤動作を回避するコトが可能な半導体装置、半導体装置の制御方法および半導体装置の制御プログラムを提供することを目的とする。

【解決手段】データ情報を処理する半導体装置(101)において、データ情報読み込みコマンドを処理するデータ情報読み込みコマンド処理手段(102a)と、前記データ情報を前記半導体装置(101)から読み込む、データ情報読み込み手段(102b)と、を備え、前記データ情報読み込みコマンド処理手段(102a)は、前記データ情報読み込みコマンドの引数を前記半導体装置(101)の前記データ情報のアドレス情報に変換する引数変換手段(S2、S20)と、前記アドレス情報と同じ値を少なくとも二つ以上の引数として、前記データ情報読み込み手段(102b)に入力する引数入力手段(S3)とを備えることを特徴とする構成である。

(もっと読む)

符号化装置および方法

【課題】符号化に係る処理を高速化する。

【解決手段】組み合わせ回路253では、(NK)段レジスタ251の上位2pシンボルから逐次qj(x2p)の係数を得て、これらの2p個の係数と生成多項式を乗算した値を、レジスタ出力および新たな2p個の情報シンボルからなる値より減算することによって、次のレジスタ入力値に用いる。レジスタから得られる2pシンボル分の係数qj(x2p)は同時に得られるため、係数と生成多項式の乗算は同時に行なうことができる。本発明は、符号化を行う装置のパリティを生成する回路に適用することができる。

(もっと読む)

共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置

【課題】共有されたエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するシステム、方法および装置を提供する。

【解決手段】メモリ・システムは、ホストとメモリ・デバイスとの間でデータを転送するためにデータ・フレームを使用する。システムは(別個のビット・レーンを介してではなく)データ・フレーム内で一つまたは複数のデータ・マスク・ビットも転送してもよい。システムは、データ・ビットおよびデータ・マスク・ビットをカバーするエラー・ビット・チェックサム(巡回冗長符号すなわちCRCのような)を生成してもよい。データ・ビット、データ・マスク・ビットおよびチェックサム・ビットは共通フレームにおいて転送される。

(もっと読む)

仮想計算機システム

【課題】

PCI-Expressバスに代表される汎用のIOバスを有するサーバにおいて、32bitアドレッシングモードのI/Oアクセスを可能とするLPAR環境を提供する。

【解決手段】

(1) LPAR上のOSで発行されたIOトランザクションが32bitフォーマットであった場合で、かつ変換後の絶対アドレスが32bit空間を超えている場合に、IOトランザクションのパケットフォーマットを変換する。

(2) LPAR上のOSで発行されたIOトランザクションにECRCが付与されていた場合に、ECRCを再計算して最終受領先で正常に受信できるようにする。

(3) ECRCが既にエラーになっていた場合には、同じエラーを再現するようなECRCパターンを生成してパケットに付与する。

(4) 前記のECRC生成について、32bitと64bitのCRC演算器を搭載して同時に計算し、パケット生成時にバス上のデータ長を元に正しいCRC演算結果を選択する。

(もっと読む)

マイクロプロセッサおよびシグネチャ生成方法ならびに多重化システムおよび多重化実行検証方法

【課題】命令実行がプログラム順序に関係なく行われるマイクロプロセッサを用いた多重化システムにおいて、容易にシグネチャ生成できるようにする。

【解決手段】命令実行がプログラム順序に関係なく行われるマイクロプロセッサにおいて、命令が実行され、実行終了した命令の結果がプログラム順に並べ直されて命令実行が確定された、ということを示す完了命令情報を用いてシグネチャを生成する。

(もっと読む)

演算処理装置

【課題】受信データのデータ長によらず高速に演算処理ができる演算処理装置を提供。

【解決手段】受信データ長30に基づいてパラレル演算回数およびシリアル演算回数が演算回数生成部32にて生成され、これら演算回数を制御するためにパラレルイネーブル信号20またはシリアルイネーブル信号16が演算イネーブル生成部40から入力制御部14に与えられると、パラレルイネーブル信号20の入力期間に受信データ12がパラレルにて演算処理部24に入力され、シリアルイネーブル信号16の入力期間に受信データ12がシリアルにて演算処理部24に入力され、演算処理部24ではそれぞれ入力データをパラレル演算処理およびシリアル演算処理をしてその処理結果を出力26に出力する。

(もっと読む)

半導体記憶装置およびその制御方法

【課題】誤り訂正能力を損なうことなく消費電力および回路規模が抑制された半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数の第1データ内の誤りをそれぞれ検出するための複数の検出符号を生成する複数の検出符号生成部41乃至48と、各第1データとこれに対応する検出符号とから第1単位データが構成され、複数の第1単位データ内の誤りをそれぞれ訂正するための複数の第1訂正符号を生成する複数の第1訂正符号生成部61乃至68と、前記複数の第1単位データから第2単位データが構成され、この第2単位データ内の誤りを訂正するための第2訂正符号を生成する第2訂正符号生成部8と、第2単位データ、複数の第1訂正符号、及び第2訂正符号を不揮発に格納する半導体メモリ2とを含む。

(もっと読む)

エラー検出コード生成装置および方法

【課題】エラー検出コードの生成に必要な時間を短縮できるようにしたエラー検出コード生成装置および方法を提供する。

【解決手段】仮想DBI(Data Bus Inversion)情報とデータを用いて仮想エラー検出コードを生成するエラー検出コード生成部と、およびエラー検出コードの生成に関わるデータ数の偶数又は奇数のうちのいずれか1つを定義する偶数/奇数情報、前記偶数/奇数情報と連関するDBI情報、および前記仮想エラー検出コードを用いて前記エラー検出コードを生成するエラー検出コード再生成部を備える。

(もっと読む)

読み書き処理方法、読み書き処理装置およびRFIDタグ

【課題】メモリ化けが生じたときに、ユーザがそれを認識できるとともに、正しいデータを得られるようにする。

【解決手段】RFIDタグへのデータの書き込み時には、データおよび対応するチェックコードを書き込んでおき、データの読み出し時には、チェックコードを用いて、読み出したデータの誤りをCRCによって検出し、誤りが検出されると、ECCによる誤り訂正を行い、更に、訂正後のデータの誤りをCRCによって検出し、訂正後のデータの誤りが検出されたときには、データが異常であることを通知し、誤りが検出されなかったときには、データの誤りを訂正したことを通知するようにしている。

(もっと読む)

データ転送装置及びヘルスチェックデータ処理方法

【課題】データ転送装置及びヘルスチェックデータ処理方法に関し、データ転送のトラフィック量により影響されるヘルスチェック応答遅延を少なくし、ヘルスチェックの監視タイマのタイムアウト最適値を容易に決定可能にする。

【解決手段】ヘルスチェックデータを送信する側で、ヘルスチェックデータに付与するエラーチェック符号として、ユーザ通信データ用のCRC符号と異なるヘルスチェックデータ固有のCRC符号を付与し、受信側では、受信データに対して、ユーザ通信データ用のCRC符号でエラーチェック(7−5)し、エラーが検出された場合に、ヘルスチェックデータ固有のCRC符号で二重CRCチェック(1−1)を行い、チェック結果が正常であれば、受信データがヘルスチェックデータであると判定してヘルスチェックを検出(1−2)し、ヘルスチェック応答を処理待ちキューの先頭又は優先的な順序位置に配置(1−4)して格納する。

(もっと読む)

誤り訂正確率を減らすエラー訂正回路、その方法及び前記回路を備える半導体メモリ装置

【課題】誤り訂正確率を減らすエラー訂正回路、その方法及び前記回路を備える半導体メモリ装置を提供する。

【解決手段】本発明によるエラー訂正回路は、ECCエンコーダ及びECCデコーダを備える。ECCエンコーダは、情報データ及び生成多項式に基づいて、h(2以上の整数)ビットエラー訂正が可能なシンドロームデータを発生させる。ECCデコーダは、情報データとシンドロームデータを含む符号データとに基づいて、情報データから最大(h−j)ビットのエラー位置を算出する単一モードで動作できる。ECCデコーダは、情報データとシンドロームデータを含む符号データとに基づいて、情報データから最大hビットのエラー位置を算出する第1動作モードまたは情報データから最大(h−j)ビットのエラー位置を算出する第2動作モードで動作できる。

(もっと読む)

1 - 20 / 48

[ Back to top ]