Fターム[5B005NN71]の内容

階層構造のメモリシステム (9,317) | W/R制御 (1,413) | アクセス競合、同時処理、逐次制御 (174)

Fターム[5B005NN71]の下位に属するFターム

階層メモリ間の転送中のアクセス (21)

要求元からのW/R (47)

W/Rとタグ処理 (7)

複数の要求元からのアクセス (52)

アクセスと一致制御 (18)

Fターム[5B005NN71]に分類される特許

1 - 20 / 29

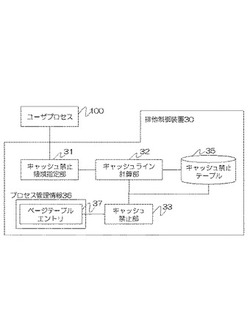

排他制御装置、方法及びプログラム

【課題】コア同士がキャッシュメモリを用いて通信を行っている場合に、コア間の通信速度の低下を防ぐこと。

【解決手段】排他制御装置は、プロセスによってコア間の通信に用いられるメインメモリの論理アドレスを物理ページ番号に変換し、プロセスと物理ページ番号とを対応付けてキャッシュ禁止テーブルに格納するキャッシュ禁止領域指定部と、物理ページ番号に対応するキャッシュラインを計算し、キャッシュラインを使用する物理ブロック番号をキャッシュ禁止テーブルに格納するキャッシュライン計算部と、キャッシュ禁止テーブルに格納された物理ページ番号が、キャッシュ禁止テーブルにおいて物理ページ番号に対応付けられたプロセス以外のプロセスに対するプロセス管理情報のページテーブルエントリに存在する場合には、キャッシュを禁止するためのフラグを当該エントリに設定するキャッシュ禁止部を有する。

(もっと読む)

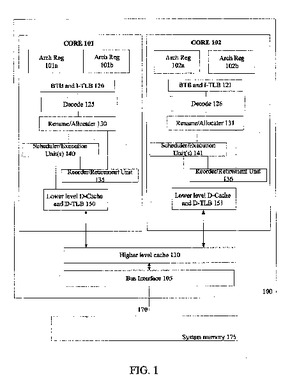

同時保留中データアクセスリクエストのためのデータハザード処理

【課題】イニシエータデバイスではなく、コヒーレンシコントローラでデータハザードを管理する、データ処理システムを提供する。

【解決手段】2つの部分形式で書き込みリクエストを処理する。同じアドレスに対し同時保留の読み出しおよび書き込みが存在する時、書き込みの第1の部分に応答しないことでコヒーレンシコントローラにより延期され、イニシエータデバイス10は、書き込みが保留中に関係なく、書き込みのアドレスに受信されたいずれのスヌープリクエストも処理するように進行する。保留中の読み出しが完了すると、コヒーレンシコントローラは、書き込みの第1の部分に応答し、イニシエータデバイスは、データおよびスヌープ後のデータの状態のインジケータを送信することによって、書き込みを完了する。コヒーレンシコントローラは、必要に応じてメモリを更新するためにこの情報を使用して潜在的なデータハザードも回避することができる。

(もっと読む)

演算制御装置及び演算制御方法並びにプログラム、並列プロセッサ

【課題】並列プロセッサに対して、並列演算に伴う複数のメモリ間でのデータ移動について、ユーザコードの開発者の負担を減らすと共に、ユーザコードの可搬性を高める。

【解決手段】属性群格納部132は、各データブロックに対して夫々設定された属性群を取得して保持する。シナリオ決定部134は、これらの属性群と、並列プロセッサである演算ユニット140の構成を示す構成パラメータとに基づいて、最下位階層のメモリと、他の階層のメモリとの間での各データブロックの転送方式を決定し、決定した転送方式に応じて各データブロックの転送、及び該転送に対応する並列演算の制御を行う。属性群は、転送方式を決定するために必要である一方、並列プロセッサの構成に依存しない属性を1つ以上含む。ライトブロックの属性群は、該ライトブロックが既に他の階層のメモリに存在し、かつ、前記最下位階層のメモリに転送されると仮定して設定されたものである。

(もっと読む)

並列コンピュータ・システムの性能を改良するための装置、方法及びコンピュータ・プログラム

【課題】並列コンピュータ・システムの性能を改良するための装置、方法及びコンピュータ・プログラムを提供する。

【解決手段】第1プロセッサの第1ローカル・キャッシュに関連する第1ローカル・キャッシュ・コントローラは、プログラム・コードを実行中の第2プロセッサによる第1キャッシュ・ラインの偽共有(false sharing)の発生を検出し且つ第2プロセッサによる第1キャッシュ・ラインの偽共有を許可する。第1キャッシュ・ラインの偽共有が発生するのは、第1ローカル・キャッシュ・コントローラによって第1ローカル・キャッシュ内の第1キャッシュ・ラインの第1部分を更新し、その後に、第2ローカル・キャッシュ・コントローラによって第2ローカル・キャッシュ内の第1キャッシュ・ラインの第2部分を更新する場合である。

(もっと読む)

ハードディスクドライブ

【課題】メディアへの書き込み完了後にコマンド完了通知を送信するコマンドの実行順序を効果的に決定する。

【解決手段】本発明の一実施の形態に係るHDD1は、複数のライト・コマンドWR1−WR5をキャッシュしている状態において、FUAコマンドを受信した場合、FUAコマンドを、他のライト・コマンドに対して優先した実行順序を決定する。ライト・バッファはリング・バッファ方式である。予め定められた基準を満たす場合は、FUAコマンド、もしくは、FUAコマンドを含み互いに関連付けられた一連のライト・コマンドの実行順序を、最初の実行順序に設定する。上記基準を満たさない場合は、キャッシュされているライト・コマンドの中で、最古のライト・コマンドを最初の実行順序に設定し、FUAコマンド、もしくは、FUAコマンドを含み互いに関連付けられた一連のライト・コマンドの実行順序を最古のライト・コマンドの後の実行順序に設定する。

(もっと読む)

ディスクアレイ装置間のリモートコピー処理システム、処理方法、及び処理用プログラム

【課題】少ないバッファで非同期順序保証コピーを実現できるディスクアレイ装置間のリモートコピー処理システムを提供する。

【解決手段】更新データを格納する送信用データバッファ26Dを設ける。ホスト10からディスクアレイ装置20に更新データ(Z1)の書き込み要求があった場合、更新データ(Z1)が前回に書き込み要求があってキャッシュ22に書き込まれている更新データ(Z0)と重複していない時は、その更新データ(Z1)をキャッシュ22に書き込む。これに対して、更新データ(Z1)が前回の更新データ(Z0)と重複している時は、キャッシュ22に格納されていた前回の更新データ(Z0)を送信用データバッファ26Dにコピーした後に、その更新データ(Z1)をキャッシュ22に書き込む。このように同じ領域に書き込みがあった場合のみ送信用データバッファ26Dにデータを書き込む。

(もっと読む)

バッファリングストアを利用してトランザクションを高速化するための機構

一実施例では、本発明は、第1スレッドにおいてトランザクショナルメモリ(TM)トランザクションを実行し、プロセッサのキャッシュメモリの第1バッファにデータのブロックをバッファリングし、第1バッファのブロックの位置におけるデータが更新されるエンカウンタタイムにブロックのオーナシップを取得するため、ブロックに対してライトモニタを取得する方法を含む。他の実施例が、開示及び請求される。  (もっと読む)

(もっと読む)

投機的バージョニング・キャッシュにおけるチェックポインティングのための方法、コンピュータ・プログラム、およびデータ処理システム(投機的バージョニング・キャッシュにおけるチェックポインティング)

【課題】 データ処理システム(100)の投機的バージョニング・キャッシュ(310、1210)内にチェックポイント(1030)を生成するための機構を提供する。

【解決手段】 機構は、データ処理システム(100)内でコードを実行し、コードは、投機的バージョニング・キャッシュ(310、1210)内のキャッシュ・ラインにアクセスする。さらに機構は、投機的バージョニング・キャッシュ(310、1210)内にチェックポイント(1030)を生成する必要性を示す第1の条件が発生するかどうかを決定する(1350)。チェックポイント(1310)は、投機的キャッシュ・ラインに対応するキャッシュ・ラインへの変更のロールバックを必要とする第2の条件の発生に応答して、非投機的となる、投機的キャッシュ・ラインである。機構は、第1の条件が発生した旨の決定に応答して、投機的バージョニング・キャッシュ(310、1210)内にチェックポイント(1310)も生成する。

(もっと読む)

トランザクショナルメモリシステム内でのハードウェア属性のメモリモデル

【解決手段】 ハードウェア属性がトランザクション実行をサポートするためのメモリモデルを提供する方法および装置を説明する。読出監視属性、書込監視属性、または、バッファリング属性をロードする監視試験処理等、ハードウェア属性のロードが発生すると、ハードウェア属性が失われたことを損失フィールドが示している場合には、エラーが発行される。また、アドレスの依存関係およびアクセスの種類の依存関係に基づき、属性アクセス処理についてはブロックおよび転送等の依存関係処理が行なわれる。この結果、メモリモデルでは、属性が失われている場合、および、属性を試験する場合には、別の処理が可能となり、制限される。

(もっと読む)

ハードウェアフィールドにロッシーなメタデータを保持するためのメタフィジカルアドレス空間

ロッシーなメタデータを保持するためもメタフィジカルアドレス空間のための方法及び装置について記載する。データ項目のデータアドレスを参照する明示的又は非明示的メタデータアクセスオペレーションが発生する。ハードウェアは、データアドレスを、メタフィジカル拡張を含むメタデータアドレスに修正する。メタフィジカル拡張は、1以上のメタフィジカルアドレス空間を、メータアドレス空間に、重複させる。メタフィジカル拡張を含むメタデータアドレスの一部は、データ項目を保持するキャッシュメモリのタグアレイを検索するのに使用される。その結果、メタデータアクセスオペレーションは、メタデータアドレス拡張に基づいて、キャッシュのメタデータエントリのみをヒットする。メタデータは、キャッシュ内に保持されることから、メタデータは、データと、キャッシュ内のスペースについて競合する場合がある。 (もっと読む)

メモリ管理システム及びメモリ管理プログラム

【課題】獲得メモリ領域が特定の位置にアラインメントされることのないメモリ領域獲得機能を容易な方法で提供する。

【解決手段】メモリ管理システムは、獲得メモリ領域の先頭アドレスが所定のアドレス位置にアラインメントされるようにメモリ領域を獲得する第1のメモリ領域獲得手段と、メモリ獲得要求に応じて前記第1のメモリ領域獲得手段を用いて獲得した獲得メモリ領域において前記先頭アドレスから始まる先頭部分にサイズが変動する第1の領域を割り当て、前記第1の領域を除いた前記獲得メモリ領域の残りの第2の領域を獲得メモリ領域として提供する第2のメモリ領域獲得手段とを含む。

(もっと読む)

キャッシュメモリ装置

【課題】入力アドレスに対するキャッシュヒット判定と、入力アドレスの隣接アドレスに限定されないプリフェッチアドレスに対するキャッシュヒット判定とを並行して実行することが可能なキャッシュメモリを提供する。

【解決手段】アドレス生成部16は、上位装置から供給される入力アドレスに基づいて、プリフェッチアドレスに含まれるプリフェッチ・インデックスアドレスを生成する。タグメモリ11が有する各ウェイは、入力アドレス中の入力インデックスアドレス及びプリフェッチ・インデックスアドレスを並行して入力し、入力インデックスアドレスによるアクセスで得られる第1のタグアドレス及びプリフェッチ・インデックスアドレスによるアクセス得られる第2のタグアドレスを並行して出力することが可能なメモリ部品を有する。

(もっと読む)

バスアクセス要求の選択的除外

バスアクセス要求を選択的に除外するシステムおよび方法が開示される。実施形態では、方法はプロセッサの論理回路でバスユニット・アクセス設定を判定することを含む。この方法はバスユニット・アクセス設定に基づいてバスユニット・アクセス要求を選択的に除外することをさらに含む。  (もっと読む)

(もっと読む)

キャッシュメモリ、キャッシュメモリ装置及び割当て方法

【課題】データメモリマクロが占める面積を小さくし、配線遅延等を防止し、性能向上を図る。

【解決手段】各データメモリマクロユニットの格納位置は、ウェイ番号と、インデックス番号と、ワード番号とによって指定され、複数のデータメモリマクロユニットに対しN個のキャッシュデータを同時書き込み許可すべく、複数のデータメモリマクロユニットのいずれか1つのデータ入力端子にそれぞれ接続されている複数のマルチプレクサを備え、同一のインデックス番号及び相違するワード番号によって指定された前記それぞれのキャッシュデータは、各データメモリマクロユニットに共通に格納され、同一のインデックス番号及び相違するウェイ番号によって指定された前記それぞれのキャッシュデータは、相違するデータメモリマクロユニットに格納される。

(もっと読む)

半導体記憶装置

【課題】SRAMと置き換え可能とし、使い勝手のよい半導体記憶装置を提供する。

【解決手段】第1と第2メモリ回路と制御回路とを有する。上記第1と第2メモリ回路は、複数のダイナミック型メモリセルより構成された同じアドレス空間を持ち、同じデータを記憶するようにされた記憶部を備え、それぞれが独立して書き込み/読み出しが可能とされる。前記制御回路は、第1状態では、前記第1のメモリ回路に対してリフレッシュ動作を行い、前記第2のメモリ回路に対して書き込み/読み出し動作を行い、第2状態では、前記第2のメモリ回路に対してリフレッシュ動作を行い、前記 第1のメモリ回路に対して書き込み/読み出し動作を行う。前記制御回路は、前記第1状態と前記第2状態の切り替えの周期を変化させることが可能である。

(もっと読む)

マルチプロセッサシステム

【課題】共有メモリへの違反アクセスを検出する。

【解決手段】マルチプロセッサシステムは、複数のプロセッサコア11に対応して設けられ、かつ有効情報と、更新情報と、アドレス情報とを格納するタグ格納部22を含む複数のキャッシュメモリ21と、複数のプロセッサコア11に共有される共有メモリ14と、複数のプロセッサコア11から共有メモリ14へのアクセス要求を調停し、かつ調停されたアクセス要求を共有メモリ14及び複数のキャッシュメモリ21に送るアービタ回路13とを具備する。アクセス要求は、キャッシュラインのデータが書き換えられた旨を示す識別信号を含む。複数のキャッシュメモリ21はそれぞれ、タグ格納部22の情報と、アービタ回路13からのアクセス要求とを比較して、違反アクセスを検出する違反検出回路24を含む。

(もっと読む)

集中キャッシュメモリのアトミックな更新方法

【課題】 ロックのオーバヘッドなしに更新される集中キャッシュを提供すること。

【解決手段】 更新は、途中で割り込むことができない点で「アトミック」である。アプリケーションは、参照テーブルを介してデータにアクセスして、常に自由に集中キャッシュ内のデータを読み込む。アプリケーションは直接キャッシュを更新せず、その代わりに更新要求をサービスルーチンに送る。キャッシュを更新するために、サービスルーチンは、2つの段階で進行する。第1の段階で、サービスルーチンは、参照テーブルを更新することなしに、新しいデータを準備し、それらをキャッシュに追加する。第1段階の間、キャッシュにアクセスするアプリケーションは、参照テーブルがまだ更新されていないため、新しいデータを「見る」ことができない。第1段階が完了した後で、サービスルーチンは、更新プロセスの第2段階、すなわち参照テーブルの自動更新を実行する。この2段階更新プロセスは、キャッシュを常に一貫した状態にしておく。

(もっと読む)

キャッシュメモリシステム

【課題】統合キャッシュにおいて、アクセスの競合を減らすことができるキャッシュメモリシステムを提供する。

【解決手段】キャッシュメモリシステムであって、メモリのデータを格納するデータ部と、前記データ部に格納されているデータが命令処理用又はデータ処理用のいずれであるかを示す識別情報を格納するライン種別部とをそれぞれが有する複数のキャッシュラインと、前記複数のキャッシュラインを更新すべきか否かを、各キャッシュラインについての前記識別情報を用いて判定するキャッシュヒット判定部と、前記判定の結果に従って、前記複数のキャッシュラインのうち更新すべきであると判定されたキャッシュラインを更新するキャッシュ更新部とを備える。

(もっと読む)

有限トランザクションメモリシステム

有限トランザクションメモリシステムを提供する方法及び装置が記載される。一実施例では、ソフトウェアトランザクションメモリ(STM)アクセスに対応する処理は、先行するハードウェアトランザクションメモリ(HTM)アクセス処理が失敗する場合に実行される。  (もっと読む)

(もっと読む)

データ転送システムにおける送信装置及び受信装置,データ転送システム並びにデータ転送システムのバス制御方法

【課題】受信バッファとしての受信キューの容量を大きくすることなくバス使用効率を向上させる。

【解決手段】該送信装置が、複数の送信側コマンドキュー17と、複数の送信側データキュー18と、送信側コマンドキュー及び送信側データキューに対してコマンド又はデータを格納制御するキュー制御部19と、送信側コマンドキュー17からのコマンド又は送信側データキュー18からのデータのうちのいずれかをバスへ選択的に出力する送信側セレクタ20と、キュー制御部19の制御により送信側コマンドキュー17及び送信側データキュー18に該コマンド及び該コマンドに対応したデータが格納されると、送信側セレクタ20において出力されるコマンドを選択するためのセレクト信号を出力する送信側セレクタ制御部21と、をそなえる。

(もっと読む)

1 - 20 / 29

[ Back to top ]