Fターム[5B005QQ05]の内容

階層構造のメモリシステム (9,317) | 置換制御 (233) | データの優先度に基づくもの (113) | 常駐データ (39)

Fターム[5B005QQ05]に分類される特許

1 - 20 / 39

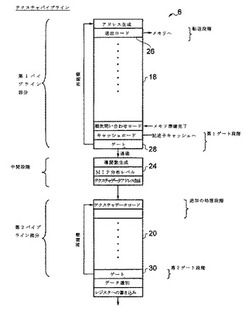

処理パイプラインの制御

【課題】処理パイプライン内の処理バブルの低減が可能なデータ処理装置を提供する。

【解決手段】グラフィクス処理ユニットは、第1パイプライン部分18と第2パイプライン部分20とを有するテクスチャパイプライン6を含む。第1パイプライン部分18内の主題命令は、その主題命令によりメモリからロードされる記述子データが、共有記述子キャッシュ内に貯えられるまで、第1パイプライン部分18内で再循環される。記述子が、共有キャッシュ内に保存されている場合、主題命令は、追加の処理操作が実行される第2パイプライン部分20に渡され、それらの追加の処理操作が完了するまで再循環される。記述子データは、その記述子データを利用するのに必要とされるテクスチャパイプライン6内の係属中の主題命令がなくなるまで、共有記述キャッシュ内に固定される。

(もっと読む)

ノーマル割り当てからの干渉がないキャッシュロッキング

【課題】キャッシュエントリの割り当てを制限するキャッシュロックの方法を提供する。

【解決手段】ブロック・ノーマル・キャッシュ割り当て(BNCA)が定義される。BNCAモードにおいて、キャッシュエントリは予め決められた命令によってのみ割り当てられる。ノーマルメモリアクセス命令(例えば、割込コードの部分として)が実行し、キャッシュミスの場合はメインメモリからデータを検索するが、キャッシュエントリの割り当てを許されない。予め決められた命令(例えば、ロックされるキャッシュエントリの確立のために使用される命令)だけがキャッシュエントリを割り当てることができる。ロックされるエントリが確立されると、プロセッサはBNCAモードを抜け、いかなるメモリアクセス命令もキャッシュエントリを割り当てることができる。BNCAモードは、構成レジスタ中の1ビットをセットすることによって指示できる。

(もっと読む)

データ値の多次元アレイへのパラレルなアクセスを提供するデータ処理装置

【課題】より効率的なキャッシュの使用をサポートする2次元アレイとして構成されるデータを処理する装置を提供する。

【解決手段】メインメモリに格納される画素値を利用して、位置の多次元領域の移動の時点を規定する処理のため、画素値がキャッシュされる。画素値に対してキャッシュミスが発生すると、キャッシュ位置におけるデータのキャッシュ置換が実行され、領域外の画像における位置に対する画素データを格納する位置が、領域内部の画像における画素データ位置を格納する置換キャッシュ位置から選択的に免除する置換のために選択される。実施例では、領域内部及び外部のデータ値をキャッシュするため異なるタイプのキャッシュ構成が利用され、キャッシュ位置に関してはキャッシュ位置より高いレベルの出力並列化をサポートし、内部の位置のキャッシュでは画像からの各ラインに対するデータはバンク上で循環的に繰り返すようにして分散される。

(もっと読む)

メモリアクセス制御装置

【課題】 動画デコーダに出力する画像データの生成に必要な画像データがキャッシュメモリにおいて追い出し対象となるのを回避し、外部メモリから動画デコーダ等へのキャッシュ制御による画像データの転送を効率的に実行する。

【解決手段】 データ要求処理部121は、動画デコーダ25に供給する画像データを生成するのに必要な画像データを1マクロブロック単位でキャッシュエリアCA(k)(k=0〜N−1)に記憶させるキャッシュ制御を行う。その際、キャッシュエリアCA(k)(k=0〜N−1)の各々についてアクセス予定カウンタACC(k)(k=0〜N−1)によりアクセス予定回数をカウントし、キャッシュエリアの画像データの追い出しが必要な場合に、アクセス予定回数が「1」以上であるキャッシュエリアを追い出し対象から除外する。

(もっと読む)

メモリアクセス制御装置

【課題】 画像データの読み出し要求を重複して発生することなく、外部メモリから動画デコーダへ画像データを効率的に供給する。

【解決手段】 データ要求処理部121は、データ要求が要求する画像データを得るのに必要な取得対象画像データのフレーム内アドレスと有効を示す有効性フラグを格納しているテーブルアリアがキャッシュテーブル122にない場合に、テーブルエリアの1つを更新対象テーブルエリアTA(k)として選択し、当該取得対象画像データのフレーム内アドレスXB(k)、YB(k)と無効を示す有効性フラグVALID(k)を更新対象テーブルエリアTA(k)に格納するとともに、当該取得対象画像データの外部メモリモジュール102からキャッシュメモリへ11の転送を指令する読み出し要求を出力する。取得対象画像データが読み出されてキャッシュエリアCA(k)に格納された場合、有効性フラグVALID(k)は有効とされる。

(もっと読む)

情報処理装置及び情報処理装置のデータキャッシング方法並びにマルチプロセッサシステム

【課題】メモリ装置を共有する複数プロセッサからなるシステムで、プリフェッチ命令によるキャッシュ機構の効果が、メモリ装置への競合アクセスに起因して無効となることを、簡単な回路構成で防止すること。

【解決手段】通常必要とするキャッシュ22以外に、メモリ装置から返却されたリプライデータを一定期間保持するためのプリキャッシュ23をキャッシュ22の前段に設け、Snoop命令は、既成の情報処理装置と同じく、キャッシュ22に対してのみ実行可能とし、プリキャッシュ23は該命令の実行対象外とする。キャッシュのエントリフルによるSwap-out処理も、キャッシュ22からのみ実行されるものとする。プロセッサ2のCore21から発行される命令に対しては、プリキャッシュ23もキャッシュ22の一部としてリード及びライトを可能とする。プリキャッシュ23内に保存したデータは、一定期間保持した後、キャッシュ22に移動させる。

(もっと読む)

データ処理装置および方法

【課題】データをキャッシュメモリのキャッシュラインにプレロードし、キャッシュラインを再利用するためのキャッシュ維持動作を制御するためのデータ処理装置および方法を提供する。

【解決手段】一連の命令を実行するように動作可能なプロセッサと、該一連の命令を実行する際の該プロセッサによるアクセスのためのデータ値を格納するように動作可能な複数のキャッシュラインを有するキャッシュメモリと、を備える。キャッシュコントローラもまた提供され、主メモリから該キャッシュメモリの1つ以上のキャッシュラインにデータ値を格納するように、該プロセッサで受信されるストリーミングプレロード命令に応じて動作可能なプレロード回路を備える。該キャッシュコントローラはまた、優先的な再利用のために、該キャッシュメモリの1つ以上のキャッシュラインを識別するように、該ストリーミングプレロード命令に応じて動作可能な識別回路を備える。

(もっと読む)

複数クラスデータキャッシュポリシー

【課題】L2キャッシュなどの中間キャッシュからどのデータをまずエビクトすべきかを判定する機構を提供する。

【解決手段】データキャッシュ内のキャッシュラインに格納されたデータ414は、そのデータの再利用可能性を反映するデータクラスに基づいて分類される。データクラスは、タグストア412に格納され、タグストア内の各タグは、データキャッシュ内の単一のキャッシュラインに対応する。コマンドに関連するデータのためにキャッシュラインを予約する時に、タグルックアップユニットは、エビクトすべきデータを判定するために、タグストア内のデータクラスを調べる。低い再利用可能性を有するデータは、高い再利用可能性を有するデータより高い優先順位でエビクトされる。有利なことに、より低い再利用可能性を有するデータクラスに属するデータをエビクトすることは、システム内のキャッシュミスの回数を減らす。

(もっと読む)

データ処理システムに於けるメモリ制御

【課題】データ処理システムに於ける効率的なメモリシステムの管理並びに制御を実現する。

【解決手段】メモリアクセス要求が発生してキャッシュミスが生じた場合に、キャッシュを入れ替えるために取り除くべきキャッシュ(ビクティムキャッシュ)を選ぶ必要がある。その際、特定の機器で占有されていないキャッシュか否か、キャッシュ存在中に書き換えられたために主メモリに書き戻す必要があるか否か、書き戻し先の主メモリがビジーであるか否かを判定して最も処理に要する時間が短くかつ最近最も使用されていないキャッシュの中から、ビクティムキャッシュを選んで効率化を図る。

(もっと読む)

情報処理装置およびメモリ管理方法

【課題】 より一般的なデマンドページング方式のメモリ管理技術を提供する。

【解決手段】 関数ポインタテーブル経由で関数呼び出しを行うプログラムを実行し、デマンドページングのメモリ管理方式を採用したシステムにおいて、関数が配置されるメモリと、プログラムの関数呼び出し時に呼び出し回数をカウントし、この呼び出し回数を定期的に監視し、この呼び出し回数に合わせて前記関数の前記メモリ配置を変更する制御部を備え、前記制御部は前記呼び出し回数の相対的に少ない前記関数がデマンドページングにより前記メモリより追い出されるよう働くことを特徴とする情報処理装置。

(もっと読む)

セクタ機能付きキャッシュメモリ

【課題】ハード・ソフトの変更コストが小さく、性能オーバヘッドも小さく、ロックによるシステム停止のおそれもなく、かつローカルメモリ的な機能と最弱ウェイ方式を同時に実現可能な、プログラムから置換制御が行えるキャッシュメモリを実現する。

【解決手段】メモリアクセス要求308により特定されるキャッシュブロックの各キャッシュウェイに対応させてセクタIDを記憶するセクタID・RAM203を追加することと、401、303〜307等の単純な判定回路とによって、メモリアクセス要求308に1ビット程度のセクタIDを指定するだけで、どのキャッシュブロックを置換するかという制御を実現することができる。これにより、少ないハードウェアコストでキャッシュメモリ上にローカルメモリ機能(高速メモリ領域)や最弱ウェイ方式と同等の機能を実現することができ、プログラムの最適化を行い、プログラムの実効速度を向上することが可能となる。

(もっと読む)

ロックインジケータを有するマルチスレッドプロセッサ

ロックインジケータを有するマルチスレッドプロセッサを含むシステムと方法が開示される。実施形態において、システムは、マルチスレッドプロセッサ内の共有リソースのロック状態を示す手段を含む。システムは共有リソースに関連する例外処理命令を処理する前に、共有リソースを自動的にロックする手段を含む。システムは、共有リソースをアンロックする手段をさらに含む。 (もっと読む)

計算機システム

【課題】1回あたりのコンテキストスイッチ、特にリストアの処理時間を短縮し、システム全体のパフォーマンスを効率よく引き出すことができる計算機システムを提供することである。

【解決手段】コンテキストリストア時に正しい実行コードをリストアする部分とトラップを発生する部分を決定する機能と、コンテキストリストア処理時に前記決定機能に基づいて一部の実行コードを正しくリストアし,他の部分はトラップを発生する命令を埋める機能と、サブプロセッサ実行中にトラップが発生したときに,コンテキストリストア時に埋めたトラップであることを識別し,該当する部分を主メモリからローカルメモリにリストアし実行を継続する機能とを備える。

(もっと読む)

キャッシュロック装置及びその方法

キャッシュのキャッシュラインをロックする方法及び装置。本方法は、キャッシュ(104)の外部にあり該キャッシュラインに対応するメモリ位置(134)が、プロセッサ(120)又は他のデータアクセスモジュールによるアクセス要求と関連付けられているという表示の受信に応じて、そのキャッシュラインの状態を有効ロック状態から無効ロック状態(508)に自動的に変更する段階を含む。従って、そのキャッシュラインのロック状態は、ロックしたキャッシュラインのデータが無効になった後も維持される。無効ロック状態を維持することで、そのキャッシュラインは、キャッシュによる再割当に利用できない。これにより、ロックされ無効になったキャッシュラインをロック状態のままにできる。これは、キャッシュラインの無効化によってそのロックが外れたかどうかを定期的に判断する追加のソフトウェアを不要にする。 (もっと読む)

データ記憶方法

【課題】コンピューティングデバイスにデータを記憶する方法を提供する。

【解決手段】本方法は、コンピューティングデバイスのページング不能カーネルメモリにメモリファイルシステムを作成するステップと、メモリファイルシステムにデータを書き込むステップと、書き込まれたデータを、コンピューティングデバイス上で実行されているユーザプロセスにアロケートされているページング可能メモリ空間へ転送するステップとを含む。このような設計の利点は、まず、メモリベースのファイルシステムのデータをページング不能カーネルメモリに保持することができ、コンテキストスイッチを実行する必要が最小にされることである。一方、ファイルシステムによって使用されるカーネルメモリの量を最小にすることができるように、必要なときにページング可能メモリへデータを転送することができる。

(もっと読む)

キャッシュ装置

【課題】意図したデータを意図した期間、演算器の近傍に置き、メモリデータのアクセス要求発生時に、低コストで意図したデータにアクセスできるキャッシュ装置を提供する。

【解決手段】多段構造のキャッシュにおいて、演算器10の近傍に置かれた小容量で高速のStatic RAM(スタテックRAM)などで構成され、通常1次キャッシュ20と呼ばれるRAMの、一部をキャッシュ領域21に、他をローカルメモリ領域22とに分割して使用可能としたものである。そして分割使用可能とされたローカルメモリのRAS機能を担保するため、ローカルメモリ領域22を2分割しそれぞれのメモリ領域に同じデータを記憶させてデータを二重化する。さらにローカルメモリ領域22では、使われないキャッシュタグの機構をエラー管理に流用し、二重化したデータから、常に正しい情報が得られるように制御する。

(もっと読む)

ストレージシステム及びストレージシステムにおけるキャッシュ常駐化の制御方法

【課題】本発明の課題は、外部ストレージ接続構成のストレージシステムにおいて、第1ストレージ装置が外部ストレージ装置である第2ストレージ装置におけるキャッシュ常駐化設定を一元的に管理できるようにすることである。

【解決手段】第1ストレージ装置は、外部ストレージ装置である第2ストレージ装置におけるキャッシュ常駐化情報を共有メモリに保持しておく。管理装置等からのキャッシュ常駐化設定要求があると、第1ストレージ装置は、当該常駐化情報を参照して、第2ストレージ装置に対するキャッシュ常駐化設定を指示する。第2ストレージ装置は、当該設定指示に従い、自身のキャッシュメモリ上にキャッシュ常駐化領域を設定する。

(もっと読む)

マルチウェイ群連想方式キャッシュ・メモリのロックダウン制御

【課題】マルチウェイ群連想方式キャッシュ・メモリ内のロックダウン動作の制御。

【解決手段】マルチウェイ群連想方式キャッシュ・メモリ6には、キャッシュ・メモリ6内にロックされている(すなわち、追い立てを受けない)データを記憶するよう当該キャッシュ・メモリの部分を制御するためのロックダウン制御回路26、48が設けられる。プログラム可能なロックダウン・データ38、40、42、44、46は、どのウェイが任意のロックされた部分を含むかを特定し、また、ロックされた部分の各ウェイ内のサイズをも特定する。このように、個々のキャッシュ・ウェイは部分的にロックされ得る。

(もっと読む)

情報処理装置、命令制御機構及び命令制御方法

【課題】ロード命令のキャッシュミスによるメインメモリへのアクセスから発生するメモリレイテンシの影響を軽減する。

【解決手段】本発明の情報処理装置は、Delinquent Loadがデータをロードする際には、Delinquent Load専用キャッシュメモリからデータをロードすることによって、キャッシュミスが発生せず、必ずキャッシュヒットすることになる。このようにすることによって、Delinquent Loadに対するデータロードに際してメインメモリへのアクセスを全く必要とせず、メモリレイテンシの発生を回避することが可能となる。

(もっと読む)

割込禁止区間処理装置および方法とページ固定装置および方法

【課題】割込禁止区間処理装置および方法とページ固定装置および方法を提供する。

【解決手段】所定プログラムが動作するためにデマンドページングが発生し得る割込禁止区間に対するリストを生成する生成部と、プログラムが割込禁止要請時生成されたリストを検索して、割込禁止要請に対応する情報がリストに含まれているかを調べる調査部と、割込禁止要請に対応する情報がリストに含まれている場合、プログラムが動作するにあたって必要とするページを補助格納装置から読込んで物理メモリにロードさせるロード部とを含む。

(もっと読む)

1 - 20 / 39

[ Back to top ]