Fターム[5B011EB01]の内容

Fターム[5B011EB01]に分類される特許

1 - 20 / 308

電圧制御

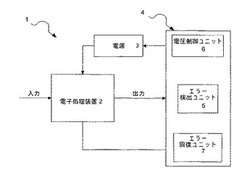

【課題】電子処理装置への電源電圧を最も効率の良い電力点で動作し、処理装置の出力の正確性を犠牲にすることなく、発生するエラーを修正することが可能な電圧制御方法を提供する。

【解決手段】プロセッサ又はメモリ要素を有する電子処理装置2への電源電圧を制御し電子処理装置の出力を受信する装置であって、当該装置は、電子処理装置の出力におけるエラーを検出するエラー検出手段5と、電子処理装置の出力において検出されたエラーの分析に基づいて、電子処理装置への電源電圧を適応的に変化させる手段6とを備える。装置は更に、電子処理装置の出力における検出されたエラーを修正する手段7を備える。

(もっと読む)

制御装置、記憶装置、及び表示装置

【課題】長い充電時間及び電池交換が不要であり、電源遮断時に、蓄電容量の少ない蓄電部により不揮発記憶部へのアクセスを正常に終了することができる制御装置、記憶装置を提供する。

【解決手段】制御装置及び記憶装置1は、第1の電力供給部101と、第1の蓄電部102と、第2の電力供給部105と、コンデンサを含む第2の蓄電部106と、第1のスイッチと、第1のスイッチを通して不揮発記憶部107にアクセスする中央制御部109と、第3の電力供給部110と、第1の電圧の測定値を出力する電圧検出部103と、第1の電圧の測定値に基づいて、中央制御部109、第1のスイッチ108、及び第3の電力供給部110を制御する電源制御部104とを備え、電源制御部104は、第1の電圧の測定値の低下に応じて、中央制御部109によるアクセスを停止させ、第1のスイッチ108をオフにし、第3の電力供給部110による電力供給を停止させる。

(もっと読む)

情報処理装置、及びプログラム

【課題】情報処理装置の省電力化と、情報処理装置の性能維持の双方を実現できる。

対象物の三次元位置を高精度で算出する。

【解決手段】実施形態の情報処理装置は、第1記憶部、第2記憶部、及び制御部を備える。第2記憶部は、第1記憶部と消費電力が異なる。制御部は、第1記憶部または第2記憶部に記憶する情報の優先度を判別し、判別した前記優先度に基づいて、前記第1記憶部または前記第2記憶部に前記情報を記憶する制御を行う。

(もっと読む)

記録装置及び記録装置の制御方法

【課題】装置を消費電力の少ないスリープモードに移行する際に、不要電磁雑音の影響を抑制しつつ、不要電磁雑音のピークを低減する効果があるがスペクトル拡散しない場合に比べ消費電力が大きくなるSSCGの消費電力を低減して装置全体を省電力にする。

【解決手段】スリープモードに移行する際にSDRAMをセルフリフレッシュ状態に遷移させた後、SSCGをスペクトル拡散されていないクロック信号を出力するモードに移行させる。

(もっと読む)

電子機器

【課題】 電子機器において、省エネモードから通常モードへの復帰に要する時間を短くする。

【解決手段】 電子機器において、通常モードから省エネモードへの移行時に、RAM13,23内のデータおよび/またはプログラムは、RAM14内に記憶され、サブCPU21は、省エネモードから通常モードへの復帰時に、RAM14からRAM13,23へデータおよび/またはプログラムを戻しRAM13,23内に記憶されているデータおよび/またはプログラムを読み出して使用するか、RAM14内に記憶されているデータおよび/またはプログラムを読み出して使用するか、を選択する。

(もっと読む)

情報処理装置及びメモリ管理方法

【課題】ハイバネーション機能における再開の高速化を実現することを可能とする。

【解決手段】実施形態の情報処理装置は、制御手段と、その制御手段がアクセス可能な記憶領域が割り当てられる揮発性の第1の記憶手段と、電源オフ状態への移行時に、第1の記憶手段の記憶領域に記憶されたデータが退避される不揮発性の第2の記憶手段と、電源オフ状態へ移行する直前の状態を再開する際に、複数のメモリセルで構成されるページ単位で第2の記憶手段に記憶されたデータを読み出して、読み出したデータを第1の記憶手段の記憶領域に展開する読出手段とを備える。

(もっと読む)

電子機器

【課題】副処理装置に異常が生じたとしても、適切に保護対象データを退避させることが出来る。

【解決手段】保護対象データを記憶している主処理装置と、当該主処理装置と通信が可能な複数の副処理装置と、を含む電子機器であって、主処理装置および複数の副処理装置それぞれが正常か異常かを判断する判断手段と、判断手段により、主処理装置および1以上の副処理装置が異常であり、1以上の副処理装置が正常であると判断された場合に、異常であると判断された1以上の副処理装置と主処理装置との通信を遮断する通信遮断手段と、正常であると判断された1以上の副処理装置のうち何れか1つを選択する選択手段と、通信遮断手段により通信が遮断されると、選択手段により選択された副処理装置に、主処理装置が記憶している保護対象データを記憶させる記憶制御手段と、を有する。

(もっと読む)

端末装置及び端末装置におけるメモリ制御方法

【課題】消費電力の削減を図るようにした端末装置及び端末装置におけるメモリ制御方法を提供すること。また、アプリケーションが継続して動作できるようにした端末装置及び端末装置におけるメモリ制御方法を提供すること。

【解決手段】アプリケーションプログラムを記憶部に記憶させて前記アプリケーションプログラムを実行することで前記アプリケーションプログラムに対応するアプリケーションを動作させる端末装置において、省電力状態に移行するとき、前記アプリケーションの動作状況と属性に基づいて、前記アプリケーションプログラムが使用される前記記憶部における記憶領域を第1の記憶領域から前記第1の記憶領域より消費電力の少ない第2の記憶領域に移動させるよう前記記憶部を制御するアプリケーション制御部を備える。

(もっと読む)

電子装置及びマイクロコントローラ並びにそれらの制御方法

【課題】省電力モードでコントローラ側のメモリインターフェース部をオフにして省電力モードを実現できる電子装置及びマイクロコントローラ並びにそれらの制御方法を提供する。

【解決手段】電子装置において、ノーマルモードから省電力モードへの切替時セルフリフレッシュモードで動作するメインメモリと、省電力モードからノーマルモードへの切替時セルフリフレッシュモードを解除するための予設定信号を出力するメモリコントローラ部と、メモリコントローラ部から出力された予設定信号をメインメモリに伝送するメモリインターフェース部と、予設定信号が出力されたか否かを検出する信号検出部とを有し、メモリコントローラ部はノーマルモードから省電力モードへの切替時メモリインターフェース部をパワーオフさせ、省電力モードからノーマルモードへの切替時信号検出部によりプリセット信号の出力が検出されるとメモリインターフェース部をパワーオンさせる。

(もっと読む)

通信装置及びその制御方法、並びに、コンピュータプログラム

【課題】メインシステムとサブシステムとから構成されるマルチプロセッサ/マルチコアシステムにおいて、省電力モード時にオフされるメモリが共有メモリである場合にも、安全に省電力/通常モードに移行する。

【解決手段】第1のプロセッサと、第2のプロセッサと、前記第1のプロセッサと前記第2のプロセッサとがアクセスする第1のメモリと、前記第2のプロセッサがアクセスする第2のメモリとを有し、前記第2のプロセッサは、前記第1のプロセッサからの指示に従って前記第1のメモリから前記第2のメモリにアクセス先を切替えると共に、省電力状態に移行する。

(もっと読む)

データ処理装置、画像処理装置およびプログラム

【課題】省電力状態にあるときの消費電力を低減しつつ、省電力状態への移行を高速化する。

【解決手段】CPUは、ミラーリング実行中かどうかを示すミラーリングフラグを「オフ」に設定し(ステップ101)、処理要求があると(ステップ102でYes)、ミラーリングフラグを「オン」に設定して省電力モードへの移行が行われないようにし(ステップ103)、共通レジスタ情報および固有レジスタ情報をミラーリングするときの記録領域を決定する(ステップ104)。そして、共通レジスタ情報を不揮発性RAMにミラーリングして完了すると完了情報を記録し(ステップ105〜108)、固有レジスタ情報を不揮発性RAMにミラーリングして完了すると完了情報を記録し(ステップ109〜112)、最後に、ミラーリングフラグを「オフ」に設定して省電力モードへの移行が行われるようにする(ステップ113)。

(もっと読む)

マイクロコンピュータおよびフィールド機器

【課題】マイクロコンピュータの回路規模の単純化を図りつつ、消費電力を低減させることを目的とする。

【解決手段】本発明のマイクロコンピュータは、信号処理を行う複数の機能ブロック4を有するマイクロコンピュータ1であって、クロックCLKを生成するクロック生成部3と、機能ブロック4のうち1つの機能ブロック4−1に備えられ、他の機能ブロック4が使用可能な共通レジスタ13に入力または出力されるデータをクロックCLKの供給が停止されたときにも保持する出力データ保持部14および入力データ保持部15と、各機能ブロック4のうち動作を行う機能ブロック4のみにクロックCLKを供給するようにスイッチ制御を行うコントロールブロック2と、を備えている。

(もっと読む)

メモリ管理装置及びメモリ管理方法及びプログラム

【課題】入力したデータをDRAMバッファに書き込む際にデータの欠損を生じさせずに消費電力の低減を図る。

【解決手段】データ書込み部102によるDRAMバッファのチップAへの入力データの書込みに並行して、書込み残量導出部103が、チップAに入力データを書き込める残量である書込み残量を導出する。電源ON判定部104は、チップ(A+1)の電源をオフにするとともに、書込み残量が、チップ(A+1)の起動時間に基づく判定基準値105と一致した際に、チップ(A+1)の電源をオンにして、チップAへの入力データの書き込みが完了した際にはチップ(A+1)への入力データの書き込みが可能となっているようにする。

(もっと読む)

電子機器、電子機器の制御方法、及びプログラム

【課題】機器本体からの電力の供給が遮断した場合におけるデータの消失に対処する仕組みを提供する。

【解決手段】画像形成装置は、ステップS203で強制メモリ受信設定がされている場合に、機器本体からRAMに電力が供給されている状態で、ステップS204でバックアップ用電池の検知電圧が規定値を下回ると判断されたときは、ステップS205でRAMに保持されたデータを印刷部に出力し、ステップS204でバックアップ用電池の検知電圧が規定値を超えると判断されたときは、ステップS208でユーザ操作により前記強制メモリ受信設定が解除されてからRAMに保持されたデータを印刷部に出力する。

(もっと読む)

電力制御方法、電子装置、プログラム及びプログラムの生成方法

【課題】メモリによる消費電力を削減する。

【解決手段】プロセッサ2で実行されるプログラム中の関数が割り当てられ、通常状態と省電力状態の電力制御状態をもつ複数のメモリ領域3a,3bのうち、メモリ領域3aに配置される関数faの実行時、メモリ領域3bに配置される関数fbが呼び出される直前に、メモリ領域3aを省電力状態、メモリ領域3bを通常状態とするように、プロセッサ2が複数のメモリ領域3a,3bの電力制御状態を制御する。

(もっと読む)

車載電子制御装置

【課題】スタンバイ開路スイッチを内蔵したマイクロプロセッサに対する簡易な定電圧電源回路を提供する。

【解決手段】電源リレーの出力接点102aを介して車載バッテリ101から給電される第2の

定電圧電源回路20Sに対し、車載バッテリ101から直接給電される第4の定電圧電源回路40Dを直列抵抗41を介して並列接続してマイクロプロセッサ120Aの駆動電源端子に接続する。出力接点102aが閉路している時は、マイクロプロセッサは第2の定電圧電源回路20Sの出力電圧によって動作し、第4の定電圧電源回路の出力電流は、直列抵抗41によって所定値以下に制限される。電源スイッチ103が開路された運転停止時には、マイクロプロセッサには第4の定電圧電源回路40Dから微小なスタンバイ電流が供給される。

(もっと読む)

メモリの電源制御を行う情報処理装置およびメモリ電源制御プログラム

【課題】仮想マシンを有する情報処理装置のメモリの消費電力を削減すること。

【解決手段】複数の仮想メモリバンクのうちの第1の仮想メモリバンクに有効なデータが無い場合に、前記複数の仮想メモリバンクの各々が前記物理メモリの複数の物理メモリバンクのいずれに属するかを示す情報を格納する仮想メモリバンクプール管理部を参照し、前記第1の仮想メモリバンクに割り当てられた物理メモリバンクが電源オフ可能か判定し、可能であれば電源オフ対象として前記第1の仮想メモリバンクに割り当てられた物理メモリバンクを指定し、前記指定された物理メモリバンクの電源をオフとする。

(もっと読む)

情報処理装置

【課題】主記憶メモリの起動時のエラーを回避しつつ、低消費電力化を実現する。

【解決手段】情報処理装置は、プロセッサと、不揮発性の記憶部と、受信部と、判定部と、送信部と、を備える。受信部は、記憶部にアクセス可能か否かの問い合わせをプロセッサから受信する。判定部は、問い合わせを受信したときに、記憶部に対する電力の供給が開始されてから記憶部が起動するまでの起動時間に基づいて、記憶部がアクセス可能か否かを判定する。送信部は、判定部による判定結果をプロセッサに送信する。

(もっと読む)

情報処理装置、通信制御装置、処理実行方法および処理実行プログラム

【課題】さらなる低消費電力化を実現すること。

【解決手段】情報処理装置100は、各部に電力供給を行うハードウェアブロック電力供給部107と、複数のRAMからなる分散RAM110と、複数の実行コードを記憶するROM102と、通常モードと省電力モードの切替えを行うとともに、通常モードと省電力モードのいずれにおいても分散RAM110のうちRAM_1には電力供給し、省電力モードの場合には、RAM_2,RAM_Nには電力供給を行わない制御を行うハードウェア電力制御部201と、ROM102から、常駐プログラムの実行コード読み出してRAM_1に配置し、常駐プログラム以外のプログラムの実行コードを読み出してRAM_2,RAM_Nに配置する実行コード展開部203と、分散RAM110に配置された実行コードを実行する分散RAM実行コード制御部204とを備えた。

(もっと読む)

計算機、消費電力低減方法およびプログラム

【課題】メモリを省電力状態にすることによる省電力効果を最大限に得る。

【解決手段】メモリを備えた計算機であって、メモリを、当該メモリに対するアクセスが可能な通常状態と、当該メモリにおける消費電力が通常状態よりも低減され、当該メモリに対するアクセスが不可能な省電力状態とのいずれかの状態にするメモリ電源制御部と、メモリに対するメモリアクセスエラーを検出する検出部とを有し、メモリ電源制御部は、メモリが省電力状態である場合に、当該メモリに対するメモリアクセスエラーが検出部にて検出されると、当該メモリを通常状態に変更する。

(もっと読む)

1 - 20 / 308

[ Back to top ]