Fターム[5B011JA08]の内容

電源 (19,167) | 電源異常対策 (704) | 停電、復電時の誤動作防止 (545) | 瞬断対策 (29)

Fターム[5B011JA08]に分類される特許

1 - 20 / 29

電子回路

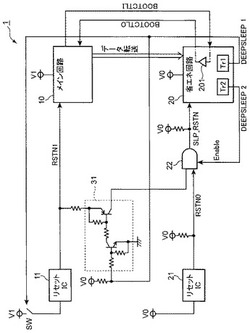

【課題】複数の電源のうち何れかの電源が瞬断したときに、確実に回路全体をリセットすること。

【解決手段】電源V1に瞬断が発生すると、リセット信号RSTN1がローレベルになりメイン回路10は動作が停止する。AND回路22はローレベルの信号SLP_RSTNを出力する。信号SLP_RSTNがローレベルになると、省エネ回路20は動作を停止し、記憶部201の記憶内容もリセットする。電源V1が復帰すると、リセット信号RSTN1はハイレベルになり、メイン回路10は信号BOOTCTLIを出力する。省エネ回路20は記憶部201の記憶内容が初期状態であるため、信号BOOTCTLOをループバックすると共に、記憶部201の記憶内容を起動処理済みであることを示す内容に書き換える。メイン回路10は、この信号BOOTCTLOを受け取ると、省エネ回路20に対して起動処理を実行する。

(もっと読む)

情報処理装置および情報処理装置の制御方法

【課題】バッテリ交換時にシステムが瞬断されることを抑制できる情報処理装置および情報処理装置の制御方法を提供する。

【解決手段】第1のバッテリ102は、第1のバッテリ収納108に着脱可能に収納され、第2のバッテリ103は、第2のバッテリ収納部110に着脱可能に収納され、システム制御部113,114は、第1のバッテリ102または第2のバッテリ103を交換する場合に使用される蓋107,109が開放状態であることが検出された場合に、情報処理装置100の消費電力が低下するように情報処理装置100の動作を制限する制限モードを開始させる。

(もっと読む)

電子機器、制御方法

【課題】主電源の瞬断を適切に判断できる。

【解決手段】主電源から複数の電源を生成し、該主電源がオフにされたときの各該複数の電源の電圧の降下タイミングを異ならせる電源生成手段と、前記複数の電源のうち、前記主電源がオフにされたときに、前記降下タイミングが最も早い第1電源より、前記降下タイミングが遅い第2電源が供給されている第1制御部と、を有する電子機器であって、前記第1制御部は、前記電子機器内の全体の制御を行なうものであり、前記主電源がオフにされたときに、前記第1電源の電圧の降下を検知して、前記第2電源の供給を検知した後に、該第1電源の再供給を検知すると、前記主電源は瞬断されたと判断する検知手段を有することを特徴とする電子機器。

(もっと読む)

電子機器

【課題】瞬断等による従来見られた不具合発生を防止する。

【解決手段】リセット端子を備えるメインICと、リセット端子に接続された追加回路とを備え、追加回路は、メインICへ供給される電源電圧を入力する第1入力端子と、メインICが稼働状態にあるときにメインICから出力される制御信号を入力する第2入力端子と、第2入力端子からの制御信号の入力があり且つ第1入力端子における電源電圧のレベルが上記所定レベルより高い所定のしきい値を下回ったときにオン状態となるスイッチ素子とを備え、スイッチ素子がオン状態となったときにリセット端子にリセット信号を与え、メインICは、リセット端子にリセット信号が与えられたときにリセット状態へ移行する。

(もっと読む)

電源瞬断対応装置

【課題】瞬断時間を正確に設定することができる電源瞬断対応装置を提供する。

【解決手段】携帯電話1は、電池パック2と、電源瞬断対応装置10と、を備え、電源瞬断対応装置10は、電池パック2からの電力の供給が停止したときにRTC12及び瞬断対応部13に電力を供給するバックアップ電源11と、クロックパルスを出力するRTC12と、瞬断を検出する電圧設定回路16を有する瞬断対応部13と、を備え、電圧設定回路16は、クロックパルスのパルス数により瞬断時間を求め、瞬断時間が閾値よりも小さいときは電源を再度立ち上げ、瞬断時間が閾値と一致したときは電源オフ状態を維持する構成を有する。

(もっと読む)

電子機器装置

【課題】電子機器装置において、電源供給が瞬間的に断たれたときに、マイコンが異常状態にならないようにする。

【解決手段】電子機器装置1は、マイコン6と、リセットIC7と、電圧低下回路8とを備える。マイコン6は、ハイレベルの信号が入力されている状態からローレベルの信号が入力される状態に変化すると、動作をリセットし、ローレベルの信号が入力されている状態からハイレベルの信号が入力される状態に変化すると、起動処理を実行し、その後、通常処理を実行する。リセットIC7は、所定電圧値未満の電圧が入力されているときには、マイコン6にローレベルの信号を入力し、所定電圧値以上の電圧が入力されているときには、マイコン6にハイレベルの信号を入力する。電圧低下回路8は、商用AC電源10から電子機器装置1への電源供給が瞬間的に断たれたときに、リセットIC7に入力される電圧を一時的に所定電圧値未満に低下させる。

(もっと読む)

情報処理システム、情報処理装置、シャットダウンタイミング決定方法およびプログラム

【課題】情報処理装置の状況によって当該情報処理装置のシャットダウン処理に必要な時間が異なる場合にも、適切にシャットダウン処理を行うことができるようにする。

【解決手段】停電が検出されると、シャットダウン時間取得部262が、サーバ装置21にて稼働中の仮想マシンの構成に基づいてサーバ装置21のシャットダウン処理に必要な時間を取得する。そして、タイミング決定部163が、サーバ装置21のシャットダウン処理に必要な時間に基づいてサーバ装置21のシャットダウン処理開始タイミングを決定する。シャットダウン信号出力部164は、シャットダウン処理開始タイミングが到来するとシャットダウン信号を出力し、サーバ装置21は、このシャットダウン信号に従ってシャットダウンを行う。

(もっと読む)

電圧検出システム及びその制御方法

【課題】電源電圧の降下が急峻な場合、システムが誤作動を起こす可能性があった。

【解決手段】割込みモードと、リセットモードとを有する電圧検出システムの制御方法であって、第1、第2の検出レベルを設定し、電源電圧が前記第1の検出レベルより高い場合、ラッチ回路を第1の状態として、前記割込みモードに設定し、前記電源電圧が前記第1の検出レベル以下となった場合、割込み信号を生成し、前記ラッチ回路を前記第1の状態から第2の状態とすることで、前記リセットモードに設定し、前記リセットモード時に、前記電源電圧が前記第2の検出レベル以下となった場合、システムリセットする電圧検出システムの制御方法

(もっと読む)

電子機器及び電子機器用プログラム

【課題】メモリ領域を圧迫することなく、しかも簡単な構成で、不意な停電等の障害に対応することができる技術の提供を課題とする。

【解決手段】画像形成装置は、画像形成装置としての動作に必要な電力の供給が断たれる電源断の発生を検出する検出部55と、検出部55が電源断の発生を検出した場合、その旨の情報をNVRAM(書き換え可能な不揮発性メモリ)に書き込む情報書き込み部56と、電源断の発生の後、画像形成装置としての動作に必要な電力の供給が再開された際に、情報書き込み部56によってNVRAMに書き込まれた電源断情報に基づいて、所定の修復処理を行う修復処理部57とを備える。修復処理は、NVRAMを動作させる際に用いるファイルシステムの少なくとも一部を修復する処理や、HDD(ハードディスク)に退避させたRAMのデータを再度RAMに復帰させる処理である。

(もっと読む)

不揮発性メモリの電源瞬断対応回路

【課題】小型・低コストのメリットを阻害することのない、マイコンと共通の電源電圧で動作する不揮発性メモリの電源瞬断対応回路であって、電源瞬断があっても確実なデータ保証が可能な不揮発性メモリの電源瞬断対応回路を提供する。

【解決手段】マイコン100のパワーオンリセット電圧VPORより上にある不揮発性メモリ94の動作保証電圧範囲VDD_MIN〜VDD_MAXにおいて、瞬断による電源電圧VDDの低下を検出し、瞬断検出信号を出力する瞬断発生検出回路40と、瞬断検出信号により、不揮発性メモリ94の書換え情報設定レジスタ94aにある書換え情報を該不揮発性メモリ94の外部で保持する書換え情報保持手段(ラッチレジスタ41)と、瞬断検出信号を保持する瞬断検出信号保持手段(瞬断検出フラグ42)とを有してなる電源瞬断対応回路とする。

(もっと読む)

画像形成装置、画像形成装置におけるバスパワー電源供給制御方法、画像形成装置用バスパワー電源供給制御プログラム

【課題】外部I/Fを介して外部機器と接続して電源供給するときにメインスイッチでオフからオンへの切り替え動作が早く行われても常時安定して通信状態を維持できる画像形成装置を提供する。

【解決手段】この画像形成装置では、サブシステム制御部7においてコンパレータ部11、12の比較結果として、バスパワー電源の電圧降下時間Δtが基準電圧VREF1、VREF2の所望の電圧降下時間Δt'よりも大きい比較結果信号comp1、comp2が入力されたとき、放電制御信号a、b、cの出力により異なる抵抗値の放電抵抗を放電制御部10において現行で設定している抵抗値のものよりも電圧降下時間Δtが早まる抵抗値のものに切り替え設定する制御を行う。放電制御部10では、バスパワー電源のオフ動作時に放電制御信号a、b、cに応じてバスパワー電源の立下り時間を早めるためにバスパワー電源に対する放電制御を行う。

(もっと読む)

サーバーとサーバーに収納される無停電電源装置

【課題】停電時と非停電時の両方において無停電電源装置から安定してサーバーに電力を供給する。

【解決手段】サーバーは、サーバーケース21に複数のブレードサーバ30を収納してなるサーバー本体20に、停電時と非停電時の両方において、サーバー本体20の入力電源ライン23に150V〜400Vの直流の動作電力を供給する無停電電源装置10を収納している。無停電電源装置10は、定格電圧を60V以下とする二次電池1と、商用電源50を直流に変換して入力電源ライン23に供給するAC/DCコンバータ2と、AC/DCコンバータ2の出力電圧を二次電池1の充電電圧に降圧する降圧用のDC/DCコンバータ3と、停電時に二次電池1の電圧を昇圧して入力電源ライン23に供給する昇圧用のDC/DCコンバータ4と、商用電源50の停電を検出して昇圧用のDC/DCコンバータ4を動作状態に切り換える充放電制御回路5とを備えている。

(もっと読む)

電源制御装置

【課題】本発明は、着脱可能なバッテリにより供給される電力で駆動される装置において、その装置の始動を図る電源制御装置に関し、構成が大幅に変更されることなく、瞬断後における始動が自動的にかつ確度高く実現されることを目的とする。

【解決手段】着脱可能なバッテリが供給する電力で駆動される装置を既定の時間に亘って閉回路が形成されたときに起動する起動制御手段と、前記バッテリによる前記電力の供給が瞬断した時点から前記既定の時間以上の時間に亘って前記閉回路の代替の回路を形成する代替回路形成手段とを備える。

(もっと読む)

データ処理装置、情報処理装置、画像形成装置、およびデータ処理プログラム

【課題】所定の処理の実行中に意図しない異常が発生した場合に当該異常の発生原因の究明に寄与する情報を得ることのできるデータ処理装置を提供する。

【解決手段】データ処理装置は、所定の処理が実行されるときに参照されるプログラムカウンタの値に関する進行履歴を示す履歴情報を記憶する記憶手段と、電源がオンの状態からオフに変化しその後オンに変化した場合の当該電源がオフになっているオフ時間を求めるオフ時間求め手段と、前記オフ時間求め手段が求めたオフ時間が予め設定される所定の時間以下の場合は、前記記憶手段に記憶されている履歴情報と予め設定される異常判定基準とを比較し、当該履歴情報が当該異常判定基準に適合するときは、前記プログラムカウンタの値に関する進行履歴が異常であると判定する判定手段と、を備える。

(もっと読む)

電源瞬停記憶装置、AC−DCコンバータ及び電源瞬停記憶方法

【課題】外部から入力電源に瞬時停止が発生したときに、瞬時停止が発生したことを確実に記録する。

【解決手段】外部電力が供給される入力端1の電圧レベルが、予め定められた閾値Vxよりも下回っているときに、その下回っている期間持続する検出信号を生成する検出手段2と、この検出信号を受信し、検出信号の持続期間が所定期間tを下回ることを検出したときに、瞬停情報を生成する判定手段3と、瞬停情報を記憶する記憶手段5と、瞬停情報を検証するための検証情報を生成し、瞬停情報及び検証情報を記憶手段5の異なる記憶領域に順次繰り返して格納する制御手段4と、を備える。

(もっと読む)

電子装置及び該電子装置の制御方法

【課題】それぞれがCPUを有する複数の制御部により構成される電子装置に対する主電源の瞬断発生時、電子装置内に存在する複数のCPUへの電源の通電状態が異なる場合であっても、ハングアップすることなく正常動作に復帰できるようにすること。

【解決手段】主電源の瞬断発生時、コントローラボードの電源が完全にOFFになり、エンジンボードの電源はONのままになる、という状態になったとしても、コントローラボードのCPUが再度初期化完了した時点で、割り込み信号発生回路が、エンジンボードとコントローラボードとの双方のCPUに割り込み信号を出力する。これにより、エンジンボードとコントローラボードとの双方のCPUが割り込み処理に入り、CPUボード間の通信の初期化を行うことができ、装置をハングアップさせることなく、確実に正常動作して立ち上げることができる。

(もっと読む)

データバックアップ方法、データバックアッププログラム、およびデータバックアップ装置

【課題】 バッテリを補助電源として備えるRAID(Redundant Arrays of Inexpensive Disks )の制御装置において、電源切断時に、装置のメモリに残っているデータを保護するためのデータバックアップ制御の技術を提供する。

【解決手段】

本発明は、電源切断時にメモリ内のデータを保護するディスク制御システムのデータバックアップ方法であって、電源の状態を監視し、電源切断の原因が通常の電源切断あるいは停電かを判断し、通常の電源切断の場合に、前記バッテリの供給に切り替えてメモリ内に存在するデータを保持し、また、停電の場合は、前記メモリ内の残留データを専用のシステムディスクへ退避させることを特徴とするディスク制御システムのデータバックアップ方法に関する。

(もっと読む)

電源瞬停保護回路

【課題】少量のデータを電源瞬停に備えて記憶する簡単な回路構成の電源瞬停保護回路を提供する。

【解決手段】電源VDDの遮断で、キャパシタ2の電荷はFF5とバッファ6に供給されると共に抵抗1を介して放電され、ノードN1の電位V1は徐々に低下する。また、キャパシタ4の電荷は抵抗3を介して放電されるが、抵抗3とキャパシタ4の時定数は、抵抗1とキャパシタ2の時定数よりも小さく設定されているので、ノードN2の電位低下はノードN1の電位低下よりも速い。電位V1がFF5とバッファ6の動作可能な電圧で、かつ電位V2がバッファ6の閾値電圧を下回らない間に電源電位VDDが復旧すると、FF5に保持されているデータ信号DIはそのままデータ信号DOとして出力される。電源瞬停時間が長くなると、電位V2がバッファ6の閾値以下に低下してFF5がリセットされ、データ信号DOは“L”となる。

(もっと読む)

電子回路

【課題】大容量のコンデンサを使用することなく、電源の瞬断が発生した場合に制御回路の誤動作を防止できる電子回路を提供する。

【解決手段】シーケンサ8の動作用電源を、主電源VDDからダイオード6を介して充電されているコンデンサ7より供給し、クロック生成回路1には、主電源VDDを供給して動作させ、シーケンサ8に対してはレベルシフト回路2によりクロック信号のレベルをシフトさせて出力する。そして、低電圧検出回路5が主電源電圧が検出閾値VPOR1よりも低下したことを検出すると、レベルシフト回路2は、シーケンサ8に対するクロック信号の供給を停止する。

(もっと読む)

データ保持装置

【課題】本発明は、電源の瞬断に対して、メモリ内のデータ保護を適切に行うことができる、データ保持装置の提供を目的とする。

【解決手段】所定のデータを保持するRAM25を有するデータ保持装置であって、RAM25の電源30の電源電圧を検出するとともにその電源電圧の変動速度を検出し、所定速度以上の電源30の電源電圧の変動速度が検出されるとともに電源30の電源電圧が所定電圧以下の場合には電源30とその電源30から電力供給を受ける所定の電気負荷70との間の電力供給経路をトランジスタTr2によって遮断することを特徴とする、データ保持装置。

(もっと読む)

1 - 20 / 29

[ Back to top ]