Fターム[5B015HH04]の内容

S−RAM (6,838) | 目的、効果の対象となるタイミング (1,247) | 待機時の (141)

Fターム[5B015HH04]に分類される特許

1 - 20 / 141

半導体記憶装置

半導体記憶装置

【課題】1つの実施形態は、例えば、電源オフ時における消費電力を低減することを目的とする。

【解決手段】1つの実施形態によれば、メモリセルは、第1の駆動トランジスタと第1の負荷トランジスタと第1の読み出し転送トランジスタと第1の書き込み転送トランジスタと第2の駆動トランジスタと第2の負荷トランジスタと第2の読み出し転送トランジスタと第2の書き込み転送トランジスタと1以上の抵抗変化素子とを有する。1以上の抵抗変化素子は、両端に印加されるバイアスの方向に依存して抵抗が変化する。1以上の抵抗変化素子は、第1の記憶ノード及び第1の書き込み転送トランジスタの間と第2の記憶ノード及び第2の書き込み転送トランジスタの間との少なくとも一方に配される。

(もっと読む)

半導体集積回路装置

【課題】先端プロセスではMOSのゲートトンネルリーク電流が増大し、低リーク電流での待機が必要となる半導体装置では問題となる。

【解決手段】電源線とソース線との電位差である複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路を具備する。負荷P型MOS及び駆動N型MOSのゲート絶縁膜厚は、4nm以下である。電源電圧制御回路は、動作状態から待機状態への変更に伴い、前記ソース線の電位を第1の電圧から当該第1の電位より高い第2の電位に変更する。前記電圧制御回路が前記ソース線の電位を前記第2の電位に変更したとき、前記スタティック型メモリセルの第1及び第2の記憶ノードのうちの一方は前記電源線の電位を保持し、前記第1及び第2の記憶ノードのうちの他方は前記第2の電位を保持する

【選択図】図5  (もっと読む)

(もっと読む)

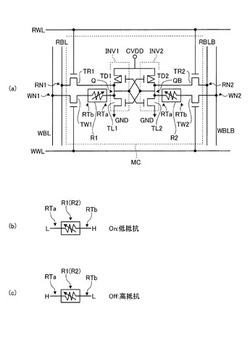

SRAMおよびその制御方法

【課題】

断熱的SRAM回路の回路構造と制御方法を改良し、さらなる低消費電力化を実現するためのSRAM回路を提供すること。

【解決手段】

従来の断熱的SRAMで記憶保持として用いられているインバータからなるフリップフロップ回路を抵抗負荷型のMOSトランジスタに置き換え、かつ読み込み・書き込み選択線の切り替えにCMOSトランスミッションゲートを配置することで、書き込み時における消費電力の増加を解決できる。

(もっと読む)

半導体集積回路装置

【課題】低電源電圧でもSNMと書き込みマージンを両立させたSRAMを備える。

【解決手段】SRAMは、複数列に対応して設けられた複数のセル電源線、電源電圧を供給する電源線、及び前記複数のセル電源線にそれぞれ対応して設けられ、各々はその対応するメモリセル電源線と前記電源線との間を電気的に接続する複数の電源回路を含む。メモリセルの各々は、第1及び第2のPチャネル型トランジスタと、第1ないし第4のNチャネル型トランジスタと第1及び第2の記憶ノードとを有するCMOSラッチ回路で構成される。電源回路は、第1の状態時にはその接続するセル電源線に第1の電圧を供給し、第2の状態時にはその接続するセル電源線に前記第1の電圧よりも低い第2の電圧を供給する、

(もっと読む)

不発揮性SRAM及びその操作方法

【課題】SRAMの読み書き機能と不揮発性メモリの不揮発記憶特性をあわせ持つ不発揮性SRAMセルを提供する。

【解決手段】二つの出力ノードを設けるラッチと、前記二つの出力ノードのうちの一つとビットラインペアのうちの一つとの間に接続されるアクセストランジスタからなるSRAMセルにおいて、前記二つの出力ノードのうちの一つと電圧ラインとの間に不揮発性メモリ素子を接続することにより、不揮発性SRAMセルを構成する。

(もっと読む)

半導体記憶装置

【課題】SRAM面積の増加を抑制しつつ、サブスレッショルド電流を削減しながらデータ保持が可能となる技術を提供する。

【解決手段】上記の課題を解決するために、メモリセル(3)と、メモリセル(3)のデータを伝達するディジット線(DT0、DB0)と、メモリセル(3)にデータを書き込む書込み回路(17、18)と、書込み回路(17、18)の動作を制御する制御回路(9、11)と、メモリセル(3)のドライバトランジスタのソースに接続されるソース線(SL)と、ディジット線(DT0、DB0)とソース線(SL)との間に設けられたスイッチ回路(21、22)とを具備する半導体記憶装置を構成する。そして、書込み回路(17、18)を、GND電圧を供給する接地線とソース線(SL)と間のダイオードとして機能させる。

(もっと読む)

半導体装置

【課題】消費電流を低減させる。

【解決手段】半導体装置は、外部端子から供給された外部電源電圧より低い第1内部電圧を第1出力端子から出力する第1降圧回路、外部電源電圧より低い第2内部電圧を第2出力端子から出力する第1モードと第2出力端子から第1及び第2内部電圧より低い第3内部電圧を出力する第2モードとが切替えられる第2降圧回路、第1出力端子に接続され接地電圧が供給される第1SRAMを含む第1内部回路、第2出力端子に接続され接地電圧が供給される第2SRAMを含む第2内部回路とを備え、スタンバイ時に第2降圧回路は第2モードに制御され、第1内部回路の高位電源電圧として第1降圧回路から第1内部電圧が供給されて第1SRAMの記憶内容は保持され、第2内部回路の高位電源電圧として第2降圧回路から第3内部電圧が供給されて第2SRAMの記憶内容は消失される。

(もっと読む)

半導体装置

【課題】複数のメモリモジュールに対する低消費電力モードの解除に際して突入電流の発生を緩和する。

【解決手段】制御信号により低消費電力モードの設定と解除が制御される複数個のメモリモジュール(MDLij)の全部または一部がメモリブロック(BLK0〜BLKm)に属し、同じメモリブロックに属する複数個のメモリモジュールに並列的に前記制御信号を入力してモジュール内経路を伝播させ、その一部のメモリモジュールが前記モジュール内経路から後段のモジュール外経路(EXR_0〜EXR_m)に前記制御信号を出力させるように、制御信号の伝播経路を構成する。このとき、前記一部のメモリモジュールは、これと同一メモリブロック内における他のメモリモジュールよりも大きな記憶容量を有するメモリモジュールとする。

(もっと読む)

半導体装置、それを用いた無線通信端末、及び電源制御方法

【課題】従来の半導体装置は、消費電力が大きくなる問題があった。

【解決手段】半導体装置1は、プログラムとプログラムによって利用されるデータとの少なくとも一方が格納される記憶領域部16と、プログラムを実行して記憶領域部16にバスを介してアクセス要求を発行する機能ブロック11と、バス23上に流れる、記憶領域部16に対するアクセス要求を示す第1の信号REQと、記憶領域部16によるバス23の占有状態を示す第2の信号GNTと、を監視して記憶領域部16へのアクセスが発生していない期間は記憶領域部16をスタンバイ状態に制御し、記憶領域部16へのアクセスが発生している期間は記憶領域部16を活性状態に制御するバス状態監視回路20と、を有し、記憶領域部16は、プログラム又はデータを記憶する記憶セルの低電位側電源電圧と高電位側電源電圧との電圧差を前記スタンバイ状態において活性状態よりも小さくする。

(もっと読む)

SRAM装置

【課題】低消費電力でより安定して動作することが可能なSRAM装置を提供する。

【解決手段】SRAM装置100は、非反転出力端子Qおよび反転出力端子/Qを有するフリップフロップ回路FFを備える。非反転出力端子と第1のビット線bitとの間に、非反転出力端子側から第1のビット線側への方向に電流が流れる第1のトンネルトランジスタT1を備える。非反転出力端子と第1のビット線との間で、第1のビット線側から非反転出力端子側への方向に電流が流れる第2のトンネルトランジスタT2を備える。反転出力端子と第2のビット線bitbとの間に、反転出力端子側から第2のビット線側への方向に電流が流れる第3のトンネルトランジスタt3を備える。反転出力端子と第2のビット線との間で、第2のビット線側から反転出力端子側への方向に電流が流れる第4のトンネルトランジスタt4を備える。

(もっと読む)

半導体装置

【課題】ロジックと揮発メモリが混載されたシステムLSIのスタンバイ状態の消費電力を低減する。

【解決手段】システムLSI中のロジック回路と第1電源線の間に第1スイッチを設けるとともに、揮発メモリの少なくとも一部と第1電源線の間に第2スイッチを設ける。スタンバイ時には該第1スイッチと第2スイッチをオフして電源を遮断する。同時に揮発メモリの少なくとも他の一部では、スタンバイ時の基板バイアスを制御してリーク電流を低減する。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を増加させることなく電源供給配線の電気抵抗を下降させることが可能な、TFTを有する半導体装置を提供することである。

【解決手段】表面を有する絶縁膜II4と、絶縁膜II4の表面上に形成され、かつチャネル領域TP2と、チャネル領域TP2を挟む1対のソース/ドレイン領域TP1,TP4とを含む半導体層と、ソース領域TP1に電源を供給するための電源供給配線TP1とを備えている。上記絶縁膜II4の表面には凹部TRが形成されている。上記電源供給配線TP1は、半導体層と同一の層から形成された層を含み、かつ絶縁膜II4の表面上に形成された第1の部分TP1Aと、凹部内に形成された第2の部分TP1Bとを有している。上記第2の部分TP1Bの底面全体が絶縁体II4で覆われている。

(もっと読む)

半導体記憶装置

【課題】パワーダウンモードから通常動作モードへの復帰時にメモリマクロに大電流が流れ込むのを抑制する。

【解決手段】SRAMマクロ100は、複数のメモリセルアレイブロックに対してアクセスが可能な通常動作モードと、複数のメモリセルアレイブロックのビットラインBL,/BLをフローティングにするパワーダウンモードを備える。パワーダウンモードから通常動作モードへの復帰時には、複数のメモリセルアレイブロックのうち、アクセスされるメモリセルアレイブロック11のビットラインBL,/BLのみを順次プリチャージする。それにより、SRAMマクロ100に流れ込む、プリチャージに要する電流のピークを分散させる。

(もっと読む)

半導体装置

【課題】待機時のリーク電流が少なく、かつ、データ保持特性に優れたSRAMセルを備えた半導体装置を提供する。

【解決手段】それぞれ負荷MOSトランジスタを備えた複数のSRAMセルがマトリクス状に配置されたメモリセルアレイ110と、メモリセルアレイの第1の電源端子VDDMと第2の電源端子VSSMとの間に電源を供給する電源回路130と、負荷MOSトランジスタに基板バイアス電圧を与える基板バイアス発生回路140と、動作時より待機時の方が、第1の電源端子と第2の電源端子との間の電位差が小さく、かつ、負荷MOSトランジスタの基板バイアス電圧が浅くなるように電源回路と基板バイアス発生回路とを制御する電圧制御回路200と、を備える。

(もっと読む)

半導体装置

【課題】先端プロセスでは、MOSのゲートトンネルリーク電流が増大し、低リーク電流での待機が必要となる半導体装置では問題となる。

【解決手段】電源線とソース線との電位差である複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路を具備する。負荷型P型MOS及び駆動型N型MOSのゲート絶縁膜厚は、4nm以下である。電源電圧制御回路は、動作状態では前記電源電圧を第1電圧とし、待機状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御して、オフ状態での負荷型P型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、駆動型N型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を動作状態に対し待機状態の方を小さくする。

(もっと読む)

半導体集積回路装置

【課題】低電圧でSRAM回路を動作させるために構成するトランジスタのしきい値電圧を下げると、トランジスタのリーク電流の増加により、データを記憶しながら動作していない状態での消費電力が増加するという問題がある。

【解決手段】SRAMメモリセルMC内の駆動MOSトランジスタのソース線sslの電位を制御することでメモリセル内のMOSトランジスタのリーク電流を低減する。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体集積回路装置

【課題】低電圧でSRAM回路を動作させるために構成するトランジスタのしきい値電圧を下げると、トランジスタのリーク電流の増加により、データを記憶しながら動作していない状態での消費電力が増加するという問題がある。

【解決手段】SRAMメモリセルMC内の駆動MOSトランジスタのソース線sslの電位を制御することでメモリセル内のMOSトランジスタのリーク電流を低減する。

(もっと読む)

センスアンプ回路

【課題】可能な限り消費電力を増加させずに高速化できるセンスアンプ回路を提供する。

【解決手段】2個のインバータを接続してなるラッチ回路と、ビット線とラッチ回路の各出力ノードとの間に挿入されセンスアンプ活性化信号に応答してプリチャージ動作する2個のプリチャージ用トランジスタとを備えたセンスアンプ回路において、各プリチャージ用トランジスタの基板−ソース間に所定の電圧を印加してトランジスタの基板バイアス効果を利用してしきい値電圧を低下させることによって、プリチャージ動作を高速化する。センスアンプ活性化信号又はその反転信号を反転して各プリチャージ用トランジスタの基板に印加するインバータ回路を備え、各インバータ回路のnMOSFETのソース端子はラッチ回路の出力ノードに接続され、プリチャージ時に各プリチャージ用トランジスタの基板からnMOSFETを介して出力ノードに流れる基板リーク電流を再利用する。

(もっと読む)

1 - 20 / 141

[ Back to top ]