Fターム[5B015NN09]の内容

Fターム[5B015NN09]に分類される特許

1 - 20 / 66

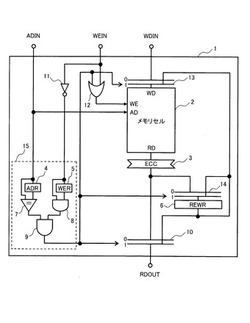

半導体記憶装置およびその制御方法

【課題】プログラム処理性能を損なうことなくデータの信頼性を向上させることが可能な半導体記憶装置を提供することである。

【解決手段】本発明にかかる半導体記憶装置は、アドレスに応じたデータの読み出しまたは書き込みを実施するメモリセル2と、メモリセル2に対して2サイクル以上同一アドレスで読み出しを行なっていることを検出する検出手段15と、メモリセル2から読み出されたデータのエラーを訂正するエラー訂正手段3と、エラー訂正後のデータを保持するデータ保持手段6と、を備える。メモリセル2は、検出手段15の検出結果に応じて、データ保持手段6に保持されているデータを前記アドレスに対応づけて書き込む。データ保持手段6は、前記アドレスに応じた読み出しデータとしてデータ保持手段6に保持されているデータを出力する。

(もっと読む)

メモリシステム

【課題】データを高速に読み出し可能なメモリシステムを提供する。

【解決手段】メモリシステムは、メモリセルアレイとセンスアンプを有する複数のバンクと、前記バンクにデータバスを介して電気的に接続されたバッファ回路と、複数の前記バンクそれぞれと前記バッファ回路との電気的な接続を切り替えるスイッチ回路と、前記バッファ回路に電気的に接続されたインターフェースと、前記バンク、前記バッファ回路、前記スイッチ回路、前記インターフェースを制御する制御部とを備え、前記メモリセルアレイに保持されたデータを5クロックで前記インターフェースに出力する場合において、前記バンクにクロックが入力されて1.5クロック経過後に、前記制御部は前記スイッチ回路を制御し、前記バンクとバッファ回路とを電気的な接続し、前記バーストバッファに前記バンクから読み出されたデータを出力する。

(もっと読む)

半導体記憶装置

【課題】2個の隣接する列ブロックのいずれにも欠陥がある場合でも、これらの列ブロックの救済が可能な半導体記憶装置を提供する。

【解決手段】データ線シフト回路58は、偶数番目の正規ブロックに欠陥がある場合に、偶数番目の正規ブロックおよび偶数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、偶数番目の内部正規データ線NIOXおよび偶数番目の内部スペアデータ線SIOXと偶数番目の外部データ線EIOXとの接続を行ない、奇数番目の正規ブロックに欠陥がある場合に、奇数番目の正規ブロックおよび奇数番目のスペアブロックを対象としたシフトリダンダンシ方式によって、奇数番目の内部正規データ線NIOXおよび奇数番目の内部スペアデータ線SIOXと奇数番目の外部データ線EIOXとの接続を行なう。

(もっと読む)

半導体記憶装置

【課題】低電源電圧下においても、安定にデータの書込/読出を行なうことのできるスタティック型半導体記憶装置を実現する。

【解決手段】メモリセル列毎に、セル電源線(APVL0−APVLn)を配設するとともに書込補助回路(BPCK0−BPCKn)を配設し、書込指示信号(WE)および列選択信号(CSL0−CSLn)に従ってセル電源線と電源ノードとを選択的に結合/分離を各列単位で実行する。データ書込時、選択列のセル電源線をフローティング状態として、その電圧レベルをビット線電位変化前に変更し、選択されたメモリセルのラッチ能力を低減して、高速でデータを書込む。

(もっと読む)

半導体回路装置及び誤り検出回路

【課題】データ書き込み時の方向と直交する方向に連続するメモリセルに記憶されたデータ列を該データ列単位で順次読み出すことが可能な半導体回路装置において、前記読み出したデータ列の誤り検出を行うのに好適な半導体回路装置を提供する。

【解決手段】半導体回路装置1の誤り検出回路43を、列誤り検出回路50_0〜50_nと、誤り検出用OR回路51とを含んだ構成とし、各列誤り検出回路において、LCDからのクロック信号LCD_CKに同期してメモリセルアレイ21から行単位に順に読み出される表示用データLCD_RDの、1ライン目の読み出し時において同じ1周期にパリティデータPTDを読み出し、行単位で順次読み出される各ラインにおける列方向に書き込まれた各ビットデータと1つ前の演算結果との排他的論理和演算を順次行い、表示用データCPU_WDに対する最終的な演算結果を誤り検出用OR回路51に出力する構成とした。

(もっと読む)

半導体記憶装置

【課題】 半導体記憶装置に面積の大きな冗長メモリセルアレイ、高感度冗長センス増幅器を設けることによる、半導体記憶装置の面積に与える影響を比較的小さくすることが課題である。

【解決手段】 メモリセルアレイは行方向および列方向に沿って2次元的に配置された複数のメモリセルを有し、複数のメモリセル中の少なくとも一列の複数のメモリセルが面積の大きな冗長メモリセルとして割り当てられる。行方向に沿って配置され、各々が前記メモリセルアレイの各列の列方向上に設けられた複数のセンス増幅器中、冗長メモリセルとして割り当てられた少なくとも一列の複数のメモリセルの列方向上に設けられた少なくとも1個のセンス増幅器が高感度冗長センス増幅器として割り当てられる。

(もっと読む)

半導体記憶装置

【課題】ビット幅の大きなメモリにおいて入出力回路の制御信号を高速に動作させる。

【解決手段】ダミーセルアレイ201をメモリセルアレイ101内に配置し、中間バッファ300を入出力回路400の間に配置することにより、ビット幅の大きなメモリにおいても面積増大効果を最小限に抑えつつ、入出力回路400の制御信号を高速かつ高周波で動作させることを可能にする。

(もっと読む)

半導体記憶装置

【課題】スタンバイ電流が小さく、ラッチアップに強い半導体記憶装置を提供する。

【解決手段】このSRAMは、各行に対応して設けられて対応の行のメモリセル電源配線MVLの一方端と電源電位VDD′のラインとの間に接続され、比較的高い導通抵抗値を有するPチャネルMOSトランジスタ1を備える。したがって、スタンバイ電流を低減化し、ラッチアップ現象の発生を抑制することができる。

(もっと読む)

半導体記憶装置

【課題】SRAM等のメモリにおける、微細化で顕著になるトランジスタ特性のランダムばらつきを抑制する。

【解決手段】メモリセル200と周辺回路201との両方がランダムばらつきによって特性が悪化し、ワースト特性に近い構成要素同士の組み合わせの際に、マクロレベルでの特性不良が発生する。その対策として、セレクタ203を介在させ、特性不良発生箇所にてビット線の正相と逆相とを交換する。あるいは、ビット線とセンスアンプとの組み合わせを隣接のデータ入出力部間で交換する等の施策を実施する。つまり、ワースト同士の組み合わせを解消するように、特性不良に対する救済を実施する。

(もっと読む)

スタック型デバイスの再マッピングおよび補修

多様な実施形態は、欠陥セルが同じダイまたは異なるダイ上の予備セルによって置換されてもよい、スタック内に配列される複数のダイを有する装置、システム、および方法を含む。  (もっと読む)

(もっと読む)

集積回路および試験方法

【課題】実際の動作速度でのFMB取得が可能な集積回路および試験方法の実現。

【解決手段】メモリ18と、メモリを試験するメモリ試験回路20,22-24,41と、入出力ポート11E,11Fと、を備え、メモリ試験回路の収集したメモリの出力を入出力ポートを介して出力する集積回路であって、メモリ試験回路は、メモリの出力をラッチするラッチ回路20を備え、第1クロックPLLに応じて全アドレスをアクセスするように変化させた時のメモリの出力を、第1クロックの整数倍の周期を有するラッチ信号に応じてラッチするスキャン・ラッチ動作を行い、ラッチ信号の1周期中にラッチしたデータを入出力ポートを介して出力する転送動作を行い、ラッチ回路がラッチするメモリセルのアドレス位置を変化させて、スキャン・ラッチ動作および転送動作を繰り返し、全メモリセルの出力を外部に出力する。

(もっと読む)

メモリの補修回路とそれを使用する疑似デュアルポートSRAM

【課題】メモリの補修回路及び補修可能な擬似デュアルポートSRAMを提供する。

【解決手段】複数のメモリセルブロックおよび予備ブロックを有し、不良ブロックを予備ブロックに選択回路で切り換えることで補修する。メモリの補修回路は、予備行の使用量が少量であり、且つ、少量の不良アドレスを保存することにより、予備行が必要な予備ブロックデコーディングの複雑度を減少させる。

(もっと読む)

半導体記憶装置

【課題】ECC回路を搭載する半導体記憶装置の動作速度を向上させる。

【解決手段】リードラッチ回路101の動作タイミングを制御する読み出し信号RYPAは、リードラッチ回路101に入力されるとともにECCレプリカ回路105にも入力され、ECC回路102における信号伝播の経路に対応する回路を経由して、上記信号伝播の時間に応じた時間だけ遅延したタイミングで、書き込み信号WYPAとしてライトバッファ回路104に入力される。

(もっと読む)

半導体装置

【課題】ECC回路を用いつつ面積、消費電力、アクセス時間の増大を改善する。

【解決手段】書き込み動作時において、複数のメモリセルから第1バスに読み出された通常データとパリティービットとを用いて通常データのエラー訂正をエラー訂正回路により行い、該エラー訂正がされた通常データを第2バスに出力する第1動作と、第1動作により訂正された通常データのうち第2バスに転送された書き込みデータに対応したデータ部分を書き込みデータ生成回路により入れ替えて第1バスの通常データ部に出力する第2動作と、第2動作により入れ替えられた書き込みデータを含む通常データを用いてパリティービット生成回路によりパリティービットを生成して第1バスのパリティービット部に出力する第3動作と、第2動作と第3動作とにより第1バスに出力された通常データとパリティービットを複数のメモリセルに書き込む第4動作とを行う。

(もっと読む)

アドレスエラー検出装置、アドレスエラー検出方法

【課題】メモリ回路のアドレスデコード部で発生する障害を高確率で検出できる小面積のアドレスエラー検出装置およびアドレスエラー検出方法を提供する。

【解決手段】Xデコーダ103の出力から複数ビットの冗長符号を生成するX符号化器105と、Yデコーダ104の出力から前記冗長符号と同じビット数の冗長符号を出力するY符号化器106と、X符号化器105の出力10とY符号化器106の出力11を各ビット排他的論理和するXOR回路107と、XOR回路107の出力12とアドレス信号1を入力し、誤り検出を行う誤り検出器108と、を備える。X符号化器105とY符号化器106、およびXOR回路107によって、アドレス信号をハミング符号化した冗長部12を生成する。誤り検出器108では、元のアドレス信号と生成された冗長符号に対して検査行列の掛け算を行い、エラーが発生したか否かを検出し、エラー出力3を得る。

(もっと読む)

半導体集積回路

【課題】RAM等の内部の少なくとも一つのメモリ回路の救済が可能であり、かつ集積度の向上を図った半導体集積回路を得る。

【解決手段】エンコード回路3は故障ビットデータfail[0]〜fail[7]を受け、これら8ビットの故障ビットデータfail[7:0]をエンコードして4ビット(圧縮ビット数)の符号化データef[3:0]を順次出力する。この符号化データef[3:0]によってRAM1についての種々の故障情報を示すことができる。キャプチャ回路4は所定のラッチ条件を満足する符号化データef[3:0]をラッチデータcf[3:0]としてラッチする。キャプチャ回路4はラッチデータcf[3:0]の直列シフト動作が可能であり、ラッチデータcf[3:0]をシリアルデータ出力Soとしてシリアルに出力することができる。

(もっと読む)

半導体記憶装置

【課題】アクセススピードを向上しつつ、面積低減を図る。

【解決手段】不良メモリセルのワード線を非活性化するためのワード線非活性化情報を格納する一時記憶回路91aと、前記ワード線非活性化情報と前記アドレス指定信号とに応じ、前記冗長メモリセルを使用するか否かを決定する非活性アドレス検知回路91bとを有したワード線活性化回路91を、各ワード線に対して設ける。そして、前記非活性アドレス検知回路91bが冗長メモリセルを使用すると決定した場合に、冗長ワード線活性化回路100によって冗長ワード線を活性化する。

(もっと読む)

半導体記憶装置

【課題】SRAMなどにおいて、従来のダイナミック・カラムシフト方式と同程度に面積ペナルティを削減でき、従来に比べて冗長数の拡張を簡単に行うことが可能にする。

【解決手段】アドレス入力が不良アドレスにヒットした時にダイナミック的にカラムシフトするカラムシフト冗長回路を有する半導体記憶装置であって、冗長カラムセルをN分割し、分割したセルに互いに異なるカラムアドレスを割り付けることを特徴とする。

(もっと読む)

半導体集積回路装置、リダンダンシシステム

【課題】ヒューズデータの転送は行うが、ヒューズボックスから外部へのヒューズデータの転送(データ出力)は行わないヒューズデータの迂回動作を行うことができ、利便性を向上できる半導体集積回路装置およびリダンダンシシステムを提供する。

【解決手段】半導体集積回路装置は、ヒューズデータをラッチするヒューズラッチ回路12と、ヒューズカウンタ回路13と、前記ヒューズデータを外部に転送する転送回路16と、前記ヒューズデータを転送しない場合に前記ヒューズデータを外部に転送せず自身の中で迂回させる迂回データパスを形成する迂回データパス回路17とを備える制御回路15とを具備するヒューズボックス11において、前記迂回データパス回路17は、前記ヒューズカウンタ回路から送信される制御信号を受信すると、前記ヒューズラッチ回路から次のヒューズデータを要求するリクエスト信号REQを前記ヒューズカウンタ回路13に動作させる。

(もっと読む)

エラー修正コード(ECC)回路テストモード

【課題】集積回路メモリ内に存在するエラー修正回路にテストモードを提供する。

【解決手段】テストモードに入り、完全に機能的なものかまたはただの一部機能的なものかどうか、既知のエラーを任意のメモリチップに強制するよう特定の位置を選択することを可能にする。付加回路は、強制されたデータエラーを実行するために要求されるいかなる付加的なスピードロスまたはエリアペナルティも最小化する、既存のバッファおよびドライバがすでにあるデータパスに配置されることができる。第1の一般的方法では、所定の時間に、論理0が選択されたデータラインに強制される。第2の一般的方法では、所定の時間に、論理1が選択されたデータラインに強制される。

(もっと読む)

1 - 20 / 66

[ Back to top ]