Fターム[5B018HA12]の内容

記憶装置の信頼性向上技術 (13,264) | 手段 (2,627) | 冗長符号 (791) | パリティ (86)

Fターム[5B018HA12]に分類される特許

1 - 20 / 86

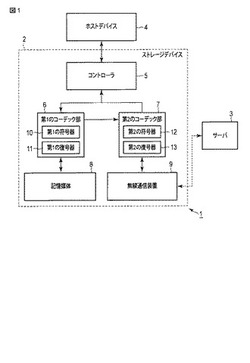

ストレージデバイス及び誤り訂正方法

【課題】ストレージデバイスにおいて、記憶媒体の記憶容量の低下を抑制しつつ、誤り訂正能力を向上させる。

【解決手段】実施形態に係るストレージデバイス2は、第1の符号器10と、記憶媒体8と、第2の符号器12と、無線通信部9とを含む。第1の符号器10は、書き込みデータの少なくとも一部に対応する第1の情報部と、第1の情報部の訂正に用いられる第1の冗長部とを含む第1の符号語を生成する。記憶媒体8は、第1の符号語を記憶する。第2の符号器12は、第1の符号語又は第1の情報部に対応する第2の情報部の訂正に用いられる第2の冗長部を生成する。無線通信部9は、第2の冗長部を、外部の記憶装置3へ無線通信する。

(もっと読む)

不揮発性メモリにおける書き込み欠陥からのデータ保護

【課題】メモリ装置の書き込み欠陥からデータを保護するための方法及びシステムを提供する。

【解決手段】この方法は、データアイテムのセットにわたる冗長情報を計算し、データアイテムを、メモリに記憶するために送信することを含む。冗長情報は、データアイテムがメモリに首尾良く書き込まれるまでの間のみ保持され、次いで、破棄される。データアイテムは、それをメモリに書き込むのに欠陥が生じたとき、冗長情報を使用して回復される。

(もっと読む)

描画サーバ、センタサーバ、符号化装置、制御方法、符号化方法、及びプログラム

【課題】符号化処理を利用した効率的なメモリ検査を行う。

【解決手段】検査対象のメモリについてパリティ情報を付加したデータをメモリに書き込んだ後、該データをメモリから読み出してランレングス符号化処理を行って符号化データを生成する。符号化装置は、書き込まれたデータについてビット列を参照して符号化データを生成する際に、該ビット列と付加されているパリティ情報とを比較してビット反転エラーを検出する。

(もっと読む)

メモリコントローラ、不揮発性記憶装置

【課題】不揮発性メモリにおいて第1の誤り訂正符号の訂正能力を超えるエラーが発生した場合でも、格納したデータを正しく読み出すことが可能で、かつ、小さいサイズの書き込みが効率的な不揮発性記憶装置、及びメモリコントローラを提供する。

【解決手段】不揮発性記憶装置1は、データを記憶する不揮発性メモリ12と、不揮発性メモリ12の制御を行うメモリコントローラ11とを備え、メモリコントローラ11は、データと同一ページに格納する第1の誤り訂正符号とは別に、第2の誤り訂正符号をも格納する。第2の誤り訂正符号の単位となるパリティグループよりもサイズの小さい書き込みにおいては、パリティグループとは別の領域に暫定的な第2の誤り訂正符号を格納する。データの読み出し時にはデータに付与された第1及び/または第2の誤り訂正符号を用いてエラー訂正を行う。

(もっと読む)

半導体装置

【課題】データの信頼性の向上を低コストで実現可能な半導体装置を提供する。

【解決手段】例えば、相補メモリを備えた半導体装置において、書き込み時に、(N+1)ビットの正極(Posi)データに対してパリティービットを生成し、(N+1)ビットの負極(Nega)データに対してパリティービットを生成する。読み出し時には、正極側および負極側のそれぞれに対してパリティーチェックを行うと共に、正極データと負極データを各ビット番号毎に比較する。ここで、正極データと負極データが同一データとなっているビット番号が存在した場合、正極側のパリティーチェック結果が異常であれば正極データの当該ビット番号を誤データとして特定でき、逆に負極側のパリティーチェック結果が異常であれば負極データの当該ビット番号を誤データとして特定できる。

(もっと読む)

記録媒体、光伝送モジュール、データ保存方法及びメモリ管理装置

【課題】不揮発メモリへ書き込み中に電源等が断たれた場合であっても、より最新のデータ情報を利用可能な記録媒体を提供する。

【解決手段】データ保存方法は、書込み要求されたデータと揮発性ユーザデータ領域のアドレスのデータとを比較し、データの変更があるか否かを判定するデータ変更判定ステップ(S11)と、データ変更判定ステップにおいて肯定的な判定の場合に、揮発性ユーザデータ領域の対応するアドレスに書込みを行う揮発性領域書込みステップ(S12)と、パリティビットを生成し、変更の内容を第1不揮発性バッファ領域にデータ毎に保存すると共に、保存先を示すアドレスを逐次変更する第1変更内容保存ステップ(S13,S14)と、第1不揮発性バッファ領域へ保存量が所定量に達した場合に、揮発性ユーザデータ領域のデータを第2不揮発性ユーザデータ領域にデータ毎に複製保存する第1複製保存ステップ(S16)と、を備える。

(もっと読む)

マイクロコンピュータ及び異常メモリアクセス検出方法

【課題】余計な命令コードを追加することなく、マイクロコンピュータにおける異常メモリアクセスの発生を検出すること。

【解決手段】メモリへのアクセス発生時、XOR処理器は、アクセス対象データのデータ幅に依存して異なる係数とアクセス対象データとのXOR演算を行う。パリティ生成回路は、XOR演算の演算結果に基づいて、アクセス対象データに関連するパリティビットを生成する。書き込みアクセス時、パリティ処理回路は、パリティ生成回路によって生成されたパリティビットをメモリに書き込む。読み出しアクセス時、パリティ処理回路は、パリティ生成回路によって生成されたパリティビットとメモリから読み出されるパリティビットとを比較し、それらが不一致である場合、割り込み信号をCPUに出力する。

(もっと読む)

データ記憶装置、メモリ制御装置及びメモリ制御方法

【課題】チャネル間誤り訂正処理の効率化を実現し、リード動作の効率を向上できるデータ記憶装置を提供することにある。

【解決手段】実施形態によれば、データ記憶装置は、チャネルコントローラと、誤り訂正コントローラと、追加訂正モジュールとを具備する。チャネルコントローラは、複数チャネルの各不揮発性メモリに対してデータの書き込み、読み出しを制御する。誤り訂正コントローラは、リード動作時に、前記チャネルコントローラにより読み出されるデータの中で指定の訂正対象に対して、チャネル間誤り訂正符号データを使用してチャネル間誤り訂正処理を実行する。追加訂正モジュールは、前記チャネルコントローラにより前記チャネル間誤り訂正処理に必要なデータを読み出す訂正読み出し動作中に、前記チャネルコントローラによるエラー検出に基づいて追加訂正対象を指定し、当該追加訂正対象を前記誤り訂正コントローラに通知する。

(もっと読む)

情報処理装置

【課題】メモリにエラーが発生する度に装置の再起動を行うと平均故障間隔が短くなってしまうこと。

【解決手段】情報処理装置1は、メモリと、このメモリに接続されたマイクロプロセッサとを備える。マイクロプロセッサは、アプリケーションプログラムの実行中に上記メモリにエラーが発生したとき、上記エラーが発生したメモリ領域の使用用途が予め定められた使用用途か否かを判定し、上記エラーが発生したメモリ領域が上記予め定められた使用用途であれば、上記エラーが発生したメモリアドレスのメモリ領域を初期化して上記アプリケーションプログラムの実行を再開する、ようにプログラムされている。

(もっと読む)

サーバ装置、メモリ装置

【課題】レジスタチップを搭載するためのコストを抑えつつ、メモリモジュールとメモリコントローラの間の通信を安定化させることのできる技術を提供する。

【解決手段】本発明に係るサーバ装置は、複数のメモリモジュールに対する命令を格納する共用レジスタを備える。メモリコントローラは、複数のメモリモジュールに対する命令を共用レジスタに格納し、共用レジスタは、メモリコントローラから受け取った命令を複数のメモリモジュールに対して並列出力する。

(もっと読む)

キャッシュメモリシステム

【課題】よりソフトエラーの影響を抑えることのできるキャッシュメモリシステムを提供する。

【解決手段】キャッシュメモリをライトスルー方式で動作させると共に、キャッシュミス発生時の動作を、キャッシュメモリに対応するデータが無い場合か、データがあってもエラーが発生している場合に行なうようにする。そして、キャッシュメモリに、以前にソフトエラーが発生したことを示すビットを立てておき、このビットが”1”のときに、再び、エラーが発生した場合には、ハードウェアのエラーが発生していると判断して、CPUに割り込みをかけるようにする。このビットは、ソフトエラーが発生すると考えられる頻度よりも十分短い時間間隔でリセットされるようにする

(もっと読む)

半導体記憶制御装置

【課題】ライトペナルティ及びパリティの更新頻度を低減して、半導体記憶装置の寿命の低下を防止可能な半導体記憶制御装置を提供する。

【解決手段】複数の半導体記憶ドライブが接続され、情報処理装置から論理アドレスが指定されて書き込みが要求されたデータを半導体記憶ドライブへ書き込む半導体記憶制御装置は、所定の単位毎の第1データと、所定の数の第1データを用いて計算され当該所定の数の第1データの誤りを訂正するために使われる冗長情報とを異なる半導体記憶ドライブに各々書き込む書き込み制御部と、半導体記憶ドライブの諸元の情報を用いて第1テーブルを記憶する第1テーブル記憶領域を構築する構築部と、所定の数の第1データ及び冗長情報を関連付けるための識別情報と、半導体記憶ドライブに書き込まれた所定の数の第1データの各物理アドレス及び論理アドレスと、冗長情報の物理アドレスとを対応付けられた第1テーブルを第1テーブル記憶領域に記憶させるテーブル制御部とを備える。

(もっと読む)

記憶装置、電子機器及び誤りデータの訂正方法

【課題】アドレス変換テーブルのエントリデータに誤り訂正符号を付与することなく、そのエントリデータに生じたビット異常の訂正を可能とする。

【解決手段】半導体記憶装置2は、論理アドレスに対応する物理アドレスへの変換にかかるアドレス変換テーブル31のエントリデータに付与された誤り検出符号をもとに、エントリデータに生じたビット異常を検出するアドレス変換テーブル異常検出部21と、ビット異常が検出されたエントリデータに含まれる所定のビットを反転させたデータが、正常なエントリデータであるか否かを検査するエントリデータ検査部22と、ビット異常が検出されたエントリデータを、検査された正常なエントリデータに置き換えるエントリデータ置換部23と、を備える。

(もっと読む)

コントローラ、記憶装置、およびプログラム

【課題】データ記憶装置単体の信頼性を向上する。

【解決手段】第1データ記憶部および第2データ記憶部を含む記憶装置に対するアクセスを制御するコントローラである。第2データ記憶部は、ユーザデータと、ユーザデータのパリティデータとを記憶する。第1データ記憶部は、パリティデータを記憶する。コントローラは、パリティ更新部と、パリティ書込部とを備える。パリティ更新部は、パリティデータが更新されたときに、更新されたパリティデータを第1データ記憶部に書き込む。パリティ書込部は、所定の条件が満たされたときに、第1データ記憶部に書き込まれたパリティデータを読み込み、読み込んだパリティデータを第2データ記憶部に書き込む。

(もっと読む)

記憶装置、回路基板、液体容器及びシステム

【課題】記憶されたデータにエラーが生じた場合でも、正しいデータを書き込むことができる記憶装置、回路基板、液体容器及びシステム等を提供すること。

【解決手段】記憶装置100は、ホスト装置400との通信処理を行う通信部110と、ホスト装置400からの受信データ及びメモリー領域選択情報を記憶する、第1、第2のメモリー領域MA1、MA2とを有する記憶部120と、第1、第2のメモリー領域MA1、MA2のいずれか一方を読み出し用メモリー領域として選択し、他方を書き込み用メモリー領域として選択して、読み出し及び書き込み制御を行うメモリー制御部130と、メモリー制御部130により読み出し用メモリー領域から読み出されたデータの値と受信データの値との大小関係を比較するインクリメント判断部140とを含む。

(もっと読む)

半導体回路装置及び誤り検出回路

【課題】データ書き込み時の方向と直交する方向に連続するメモリセルに記憶されたデータ列を該データ列単位で順次読み出すことが可能な半導体回路装置において、前記読み出したデータ列の誤り検出を行うのに好適な半導体回路装置を提供する。

【解決手段】半導体回路装置1の誤り検出回路43を、列誤り検出回路50_0〜50_nと、誤り検出用OR回路51とを含んだ構成とし、各列誤り検出回路において、LCDからのクロック信号LCD_CKに同期してメモリセルアレイ21から行単位に順に読み出される表示用データLCD_RDの、1ライン目の読み出し時において同じ1周期にパリティデータPTDを読み出し、行単位で順次読み出される各ラインにおける列方向に書き込まれた各ビットデータと1つ前の演算結果との排他的論理和演算を順次行い、表示用データCPU_WDに対する最終的な演算結果を誤り検出用OR回路51に出力する構成とした。

(もっと読む)

半導体記録再生装置

【課題】エラー耐性を改善しつつ、高速リード転送と低消費電力の双方を満足する半導体記録装置を提供する。

【解決手段】半導体記録再生装置10は、外部機器とユーザデータを送受信する外部インタフェイス部1と、ユーザデータに対するパリティデータを生成するとともに、パリティデータを用いてユーザデータのエラーを訂正する第1のECC処理部3と、ユーザデータを複数に分割し、分割したユーザデータおよびパリティデータを、フラッシュメモリ6a〜6eに記録するとともに、パリティデータを除くユーザデータを読み出す第1の再生モードと、パリティデータを含むユーザデータを読み出す第2の再生モードを有し、何れかのモードでフラッシュメモリ6a〜6eからユーザデータを読み出して再生するECC制御部2と、を備える。

(もっと読む)

記憶装置、基板、液体容器、データ記憶部に書き込むべきデータをホスト回路から受け付ける方法、ホスト回路に対し電気的に接続可能な記憶装置を含むシステム

【課題】記憶装置において、ホスト回路との通信の信頼性を向上する。

【解決手段】ホスト回路と電気的に接続される記憶装置は、不揮発性のデータ記憶部と、データ受信部と、判定部と、データ送信部とを備える。データ受信部は、ホスト回路からメモリアレイに書き込むべき第1のデータと、第1のデータに基づいて生成された第2のデータを受信する。判定部は、第1のデータと第2のデータとの整合性を判定する。データ送信部は、判定の結果をホスト回路に送信する。データ送信部は、判定部により肯定的な判定結果が得られた場合に、(1)データ記憶部へのデータの書き込みが完了した場合には肯定的な判定結果をホスト回路に送信し、(2)データ記憶部へのデータの書き込みが完了しなかった場合には肯定的な判定結果をホスト回路に送信しない。

(もっと読む)

誤り訂正符号復号装置及び誤り訂正符号復号方法

【課題】 硬判定復号と軟判定復号の併用により、NANDフラッシュメモリ等の読み出しデータの信頼性を向上させると共に、全体としての処理時間の短縮をはかる。

【解決手段】 ビット当り2値の信号を入力データとして硬判定復号を実行すると共に、該入力データに対してパリティ検査を実行する硬判定復号部11と、ビット当り多値数が2より大きい信号を入力データとして軟判定復号を実行する軟判定復号部13と、硬判定復号部11及び軟判定復号部13の起動を制御する起動制御部14と、硬判定復号部11と軟判定復号部13の各出力信号の一方を選択して出力する出力選択部15とを備え、パリティエラーの個数が許容値内の場合には、硬判定復号部11の復号結果を選択して出力し、パリティエラーの個数が許容値を超えた場合には、軟判定復号部13を起動すると共に軟判定復号結果を選択して出力する。

(もっと読む)

半導体記憶装置および半導体記憶装置の制御方法

【課題】読み出し速度を向上させることができる半導体記憶装置を得ること。

【解決手段】書き込みデータとセクタ単位で生成されたCRC符号およびL1ECC符号とクラスタ単位で生成されたL2ECC符号とを格納するためのNANDメモリ20と、NANDメモリ20から読みだされた、書き込みデータとCRC符号とL1ECC符号とを用いてL1ECC処理を実施し、残留する誤りがあるか否かを判定するCRC/L1デコーダ18と、残留する誤りがあると判定されたセクタを含むクラスタに対して、書き込みデータとCRC符号とL2ECC符号とを用いてL2ECC処理を実施するL2デコーダ50と、残留する誤りの有無に基づいてクラスタ内のL2ECC符号を読み出すか否かを判定する読み出し判定部17と、を備える。

(もっと読む)

1 - 20 / 86

[ Back to top ]