Fターム[5B018KA13]の内容

記憶装置の信頼性向上技術 (13,264) | エラー処理 (1,086) | 障害回復 (704) | 正常メモリへの置換 (91)

Fターム[5B018KA13]の下位に属するFターム

動的置換 (43)

Fターム[5B018KA13]に分類される特許

1 - 20 / 48

記録装置、読出装置、および、記録再生装置

【課題】フラッシュメモリに対してリアルタイムデータを記録する機器において、書き込みエラーが発生したときに、書き込みを継続するための手段が、ファイルシステムとは無関係な独自形式であるため、ファイルシステムによりデータを記録するシステムには適合できない。

【解決手段】複数のアクセスユニットで構成されるメモリを有する記録装置であって、前記メモリにデータをアクセスユニット単位で記録する記録手段と、前記記録手段で前記データを前記メモリに書き込んでいるときに、書き込みエラーを検出する書き込みエラー検出手段とを備え、前記記録手段は、前記書き込みエラー検出手段で書き込みエラーが検出されたときに、ファイルの書き込みを終了する。

(もっと読む)

ソリッド・ステート・ドライブ装置およびミラー構成再構成方法

【課題】可用性を向上させ、かつ、価格を抑制することが可能なミラー構成のSSD装置を提供する。

【解決手段】SSD装置1は、A系とB系とからなるミラー構成の不揮発データ記憶部20および不揮発データ記憶制御部10を備え、不揮発データ記憶制御部10は、ページ・リード・ライト制御部11、アドレス変換処理部13、物理アドレス選択処理部14、アドレス変換テーブル15を備える。ページ・リード・ライト制御部11は、NVMチップ21の故障を検出したとき、その故障したNVMチップ21とミラー関係にあるNVMチップ21からページデータを読み出し、その読み出したページデータを、故障したNVMチップ21およびそれとミラー関係にあるNVMチップ21以外の、A系およびB系の不揮発データ記憶部20のそれぞれに属し、互いにミラー関係にあるNVMチップ21へコピーする。

(もっと読む)

メモリシステム

【課題】全体の信頼性を確保しつつチップ単体に許容される不良率を緩和したメモリシステムを提供すること。

【解決手段】夫々所定サイズの単位領域毎に分割管理されるn個の不揮発性半導体メモリのチップを有し、前記n個のチップのうちの一つのチップの単位領域は前記単位領域に夫々対応付けられている他のn−1個のチップにおける単位領域を含む群に対する誤り訂正符号を記憶し、かつ前記誤り訂正符号を格納するチップが単位領域の位置毎に異なるメモリチップ群と、単位領域のデータを書き換えるとき、前記データの誤り訂正符号を格納している単位領域を書き換えデータの書き込み先に指定し、書き換え前のデータが格納されていた単位領域を新たな誤り訂正符号の格納先に指定するアクセス先算出部と、を備える。

(もっと読む)

携帯端末装置、ソフトウェア更新方法、動作制御方法及びプログラム

【課題】 ソフトウェアを格納する不揮発性メモリを有効利用することができる携帯端末装置を得る。

【解決手段】 不揮発性メモリ12は複数のブロックに分割され、各ブロックはメイン領域とスペア領域を含む。制御部11は、ソフトウェア更新用の差分データを基にブロック単位でソフトウェアの書き換えを行う際、メモリ12内の書き換え対象ブロックが不良ブロックである場合、メモリ12の代替領域のブロックに差分データを書き込むと共に、この代替ブロックのスペア領域に書き換え対象ブロックの論理ブロック番号を書き込む。

(もっと読む)

メモリシステムおよびコンピュータシステム

【課題】本発明は、メモリにおいて後発欠陥が発生したとしても、多くのブロックに渡って論物変換の対応関係を変更する必要がないメモリシステムを提供する。

【解決手段】本発明に係るメモリシステムは、ユーザ情報を記憶するために設けられ、互いに重複しない第1物理アドレスが個々に割り当てられる複数の第1ブロック42と、複数の第1ブロック42のうちの初期欠陥ブロックの第1物理アドレスを個々に記憶するために設けられる複数の第2ブロック52baと、複数の第1ブロック42のうちの後発欠陥ブロックの第1物理アドレスを個々に記憶するために設けられる複数の第3ブロック52bbとを備えている。さらに、論理アドレスと、第2ブロック52baに格納される情報と、第3ブロック52bbに格納される情報とに基づいて、論理アドレスに対応する第1物理アドレスを求める演算装置50を、備えている。

(もっと読む)

キャッシュメモリ制御回路、キャッシュメモリ装置、及びキャッシュメモリ制御方法

【課題】キャッシュメモリへの書込不良を正確に検出すると共に、データリカバリに伴うペナルティ期間を短縮することが可能なキャッシュメモリ制御回路を提供する。

【解決手段】キャシュメモリ制御回路33を、連続して入力され得るデータの最大個数(="4")分のキャッシュメモリ32_1〜32_4各々に対応して設けられ、各々が対応するキャッシュメモリに一のデータを書き込むと共に、前記対応するキャッシュメモリから読み出したデータが前記一のデータと一致するか否かを判定し、両データが一致しないと判定した場合に前記一のデータを前記対応するキャッシュメモリに再び書き込む4個のリカバリ部331_1〜331_4と、リカバリ部331_1〜331_4を順次制御し、連続して入力されたデータD0〜D3各々を互いに異なるキャッシュメモリに書き込ませる書込制御部332と、で構成する。

(もっと読む)

記憶装置及び記憶装置の制御方法

【課題】搭載した回路基板上の記憶装置の接合部における損傷を確実に推定することにより、記憶装置の信頼性を確保する。

【解決手段】半導体メモリ50が搭載された複数個の半導体メモリパッケージがプリント基板に接合部を介して実装された記憶装置100であって、記憶装置100の状態に関する物理量を計測するセンサ部10と、物理量から接合部の損傷を推定するための損傷推定用モデルベースを蓄積したデータベース20と、損傷推定用モデルベース20を利用して、物理量から接合部の損傷の推定値を演算する損傷推定部30と、前記推定値に応じて、前記接合部を介して実装されている前記半導体メモリパッケージに搭載された前記半導体メモリへの電子データの書き込み、読み取り、消去を選択的に制御する制御部40とを備える。

(もっと読む)

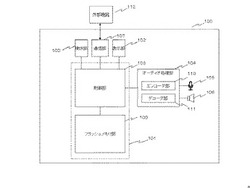

プログラマブル論理回路の起動保障方法及びそのプログラマブル論理回路装置

【課題】メモリの冗長化を行ってFPGAの起動を保障する

【解決手段】FPGA周辺回路は、論理回路データが格納されたメインメモリ21及びサブメモリ22と、FPGA10と、異常監視回路40と、メモリ切替回路30とを有している。FPGA10は、電源投入後の起動時に初期化を行った後、メインメモリ21に格納された論理回路データを読み出し、コンフィグレーションを行う。異常監視回路40は、FPGA10における初期化完了からコンフィグレーション完了までの経過時間を監視し、その経過時間が設定時間を超えると、メインメモリ21が異常であると判断して異常通知信号S40aを発生する。メモリ切替回路30は、異常通知信号S40aを受信すると、メインメモリ21をサブメモリ22に切り替え、再度FPGA10に対してコンフィグレーションを行わせる。

(もっと読む)

不揮発性メモリシステム内での使用不可能なブロック管理

【課題】欠陥ブロックとして識別される、潜在的に使用可能なブロックが予備ブロックとして用いられることを可能にする。

【解決手段】本発明は、不揮発性メモリ124内で欠陥があるとして識別された少なくとも1つの物理ブロックに試験を受けさせる工程であって、該試験は、欠陥がある物理ブロックが使用可能であるか否かを判定するように構成される、工程と、欠陥があるとして識別された該物理ブロックが該試験に合格した場合を判定する工程と、欠陥があるとして識別された該物理ブロックが該試験に合格したことが判定された場合、欠陥があるとして識別された該物理ブロックを使用可能な物理ブロックとして識別する工程とを包含する。

(もっと読む)

組込システム

【課題】回路構成用データを書き換える際に、何らかの理由で書き換え作業が中断するしたり、誤ったデータを書き換えてしまった場合には、次回電源起動時より、PLDがPCIバスに対応した制御回路として動作しなくなり、メインボード側からのソフトウェアによる記憶媒体上の回路構成データの更新手段が無くなり、再度動作させることが不可能となる。

【解決手段】PLDを用いた制御基板の回路構成用データを更新することを保証した回路構成用データを用意し、自動または手動で使用する回路構成用データを切り替えて、PLDの回路構成のデータにトラブルが発生した場合の復帰方法を備える。

(もっと読む)

フラッシュ消去可能なプログラマブル・リードオンリメモリを用いてファイルシステムをマネージする方法及びシステム

【課題】1以上の論理ブロックを有する一回書込み多数回読取りメモリデバイスを備えたコンピュータシステム内でエラーを回復する方法を提供する。

【解決手段】(a)各ブロックにデータ領域を画成し(データ領域はデータ領域エリアに論理的に分割)、(b)各ブロックにブロック構造体を画成し(ブロック構造体はヘッダと割当てテーブルを有し、ヘッダはブロックに特定情報を含み、割当てテーブルは、データ領域エリアに対応するエントリと、対応するデータ領域エリアに関連した情報を含む)、(c)割当てテーブルエントリを割当て、(d)データ領域エリアを割当て、(e)割当てられたデータ領域エリアに関連したデータを、割当てられた割当てテーブルエントリに書込み、(f)割当てられたデータ領域エリアにデータを書込み、(g)書込む間にエラーを検出し、(h)エラー検出時に割当てテーブルエントリを割当て解除状態にセットし、エラーが検出されなくなるまで上記段階(c)、(d)、(e)、(f)を繰り返す方法。

(もっと読む)

データ処理装置及びその制御方法

【課題】 制御要素であるメモリに異常が生じた場合でも、その後の迅速かつ確実な再起動が可能なデータ処理装置及びその制御方法を提供。

【解決手段】 少なくとも1つが制御要素として使用される複数のメモリを搭載する。起動時に、制御要素として使用されるメモリの異常を検出すると、各メモリのうち、異常が検出されたメモリを除く他のメモリを新たな制御要素として設定し、起動を継続する。

(もっと読む)

パリティエラー復旧回路

【課題】外部メモリからのデータの再書き込みを行うことなく、かつ回路規模を増大させることなくパリティエラーが発生したデータを復旧し得るデータ復旧回路を提供する。

【解決手段】記憶領域内の実使用領域RAM0に、実データを書き込み、コピー領域RAM3にバックアップデータを書き込み、実データとバックアップデータの書き込み処理を並行して行う書き込み処理回路と、実データとバックアップデータを並行して読み出して、パリティエラーとなった実データを復旧する読み出し処理回路とを備え、書き込み処理回路には、実データを偶パリティで書き込む第一のパリティ発生回路2と、バックアップデータを奇パリティで書き込み、実データを偶パリティで該コピー領域に上書きする第二のパリティ発生回路3とを備え、読み出し処理回路は、偶パリティチェッカーと、奇パリティチェッカーとを備えた。

(もっと読む)

メモリシステム、コンピュータシステム及びメモリ

【課題】アクセス速度を低下させることなく、論理アドレスと物理アドレスとの変換に用いられる予備的な記憶領域の必要容量を抑制する。

【解決手段】論理アドレスを昇順に、メモリの欠陥ブロックの物理アドレスをスキップさせながら、物理アドレスの昇順に対応づけるように、論理アドレスと物理アドレスとの相関関係を定める。そして、欠陥ブロックの物理アドレスを、当該物理アドレスの昇順に、第2ブロック56の物理アドレスの昇順に、連続して個々に格納する。論理アドレスから物理アドレスを求める場合は、論理アドレスに基づいて、複数の第2ブロック56からターゲットブロックを検索し、ターゲットブロックの物理アドレスを論理アドレスに加算することにより物理アドレスを求める。

(もっと読む)

リペア可能な半導体メモリ装置と該半導体メモリ装置のリペアリング方法

【課題】リペア可能な半導体メモリ装置を提供する。

【解決手段】半導体メモリ装置は、第1システムデータを保存する第1ブロックと第1システムデータと同一の第2システムデータを保存する第2ブロックとを有するメモリセルアレイを含む。コントローラは、ホストから出力されたリセット信号に応答して第1システムデータをメモリユニットに出力し、ECC検出ブロックによって発生したフェイル検出信号に基づいて第2システムデータをメモリユニットに伝送する。ECC検出ブロックは、第1システムデータが欠陥データであるか否かを判断する。半導体メモリ装置をリセットする間に第1システムデータで欠陷が発生する時、第1システムデータは、第2システムデータの提供によってリペアされる。

(もっと読む)

ストレージシステム及びその制御方法

【課題】記憶デバイスとして不揮発性メモリを用いたときに特有の問題について、性能劣化を防止しながら有効に対応し得るストレージシステム及びその制御方法を提案する。

【解決手段】ストレージシステムに、1又は複数の不揮発性メモリチップを有する複数のメモリモジュールと、各メモリモジュールに対するデータの読み書きを制御するコントローラとを設け、メモリモジュールが、自メモリモジュール内の不揮発性メモリチップに障害が発生したときに、当該不揮発性メモリに格納されているデータのコピー先とする不揮発性メモリチップを決定し、障害が発生した不揮発性メモリチップに格納されていたデータをコピー先として決定した不揮発性メモリチップにコピーするようにした。

(もっと読む)

情報記憶装置、情報記憶方法及びプログラム

【課題】記憶されたデータの信頼性を容易に向上する。

【解決手段】複数のバンクに分割されたフラッシュメモリ103に、バンクが使用可能かどうかを示す情報とバンクに予め付与されたバンク番号との対応付け情報が記憶され、CPU102によって、バンクに当該バンクに記憶するデータに対するECCが記憶され、ECCによりデータに訂正可能エラーがあると判断された場合、当該データが訂正され、使用可能な別のバンクに訂正されたデータがフラッシュメモリ103に書き込まれる。

(もっと読む)

多値フラッシュメモリ用ドライバ

【課題】組み込みシステムに使用するフラッシュメモリのドライバは、商用電源を使うことが少なく電池を使用することが多く耐電源障害性に強いことが要求される。更に多値のフラッシュメモリのドライバにおいては、書き込み中に電源断が生じれば、書き込んでいるページばかりではなく、同一セル内にある他のページの内容も壊してしまう可能性があり、さらに修復が不可能な課題がある。

【解決手段】そこで本発明は、あるブロックにデータを書き込むときは、別の他のブロックを用意して、交互にそれそれのブロックの相対するページに同一のデータを書き込むステップを持つことにより、電源断等、電源障害が生じたときでもデータを消滅することなく書き込むことが可能となる。

(もっと読む)

メモリ制御システム、メモリ制御装置、メモリ制御方法

【課題】 予備のメモリモジュールを設けず、ミラーリング構成のメモリモジュールに障害が発生したとき、ミラーリング動作を継続させ、信頼性を向上したメモリ制御システム、メモリ制御装置、メモリ制御方法を提供する。

【解決手段】 メモリ制御装置200は、メモリモジュール(#0)41に障害が発生したとき、障害発生のメモリ領域を縮退する手段と、障害発生のメモリモジュール(#0)41とペアになっているメモリモジュール(#2)51を、第1メモリ装置40と第2メモリ装置50とのミラーリングのペアとして再構築する手段とを備える。

(もっと読む)

メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】データの書き込みがフラッシュメモリの特定の領域に集中することを回避すると共に、各論理ゾーンに割り当てる記憶容量を適宜調整することができるメモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法を提供する。

【解決手段】複数セクタの領域で構成された論理ゾーンに対して複数の物理ブロックで構成された物理ゾーンを割り当て、この割り当てに従ってフラッシュメモリにアクセスするフラッシュメモリシステムにおいて、ホストシステムに対してアクセスを許容する論理アドレスの範囲を適宜設定し、設定した論理アドレスの範囲を、複数個の論理ゾーンに対して論理アドレスが連続する所定のセクタ数単位で順次割り振る。フラッシュメモリにアクセスするときは、各論理ゾーンに割り振られた論理アドレスを、その論理ゾーンに割り当てられている物理ゾーン内の物理アドレスに変換する。

(もっと読む)

1 - 20 / 48

[ Back to top ]