Fターム[5B018MA23]の内容

記憶装置の信頼性向上技術 (13,264) | 対象 (1,668) | ROMを組込んだメモリシステム (418)

Fターム[5B018MA23]に分類される特許

401 - 418 / 418

分散システム内のバックアップ・ファームウェア

【課題】 分散システム、分散システム用のプロセッサ・ノード、分散システム用のモジュール、自動データ・ストレージ・ライブラリ、およびコンピュータ・プログラムを提供することにある。

【解決手段】 ネットワーク内の複数モジュールからなる分散システムにおいて、各モジュールは、関連モジュールを操作するための処理装置を有する関連プロセッサ・ノードを有する。処理装置は、ネットワーク内で通信するためのプロセッサ・インターフェースと、関連モジュールを操作するための処理装置用のコードを保管し、ネットワーク内の他のプロセッサ・ノードの少なくとも1つの他の処理装置用のバックアップ・コードを保管するための不揮発性メモリであって、バックアップ・コードが当該他のプロセッサ・ノードの関連モジュールを操作するためのものである不揮発性メモリとを有する。要求に応答して、処理装置は、要求側プロセッサ・ノードに関連するモジュールを操作するためのコードを復元するために使用されるプロセッサ・ノードにそのバックアップ・コードを提供する。  (もっと読む)

(もっと読む)

フラッシュメモリ管理装置

【課題】 書き込み回数情報の正当性を確保すると共に、フラッシュメモリ内に設けた書き込み管理領域へのアクセスを高速化したフラッシュメモリ管理装置を実現する。

【解決手段】 フラッシュメモリの書き込み回数を監視するフラッシュメモリ管理装置において、

前記フラッシュメモリには、書き込みの発生毎にビット状態が変わるビット列情報が記憶され、

書き込みの発生毎にカウントする回数情報が記憶されるRAMと、

前記ビット列情報と前記回数情報とを照合するフラッシュメモリ管理手段と、

を備える。

(もっと読む)

携帯端末

【課題】 携帯端末のように小型で安価な装置にあって、初期化機能の実行進捗に合わせた画面表示を行う。また、プログラムを格納するNANDフラッシュメモリに余分な冗長性を持たせることなく限られた容量でエラーの信頼性を向上する。

【解決手段】 NANDフラッシュメモリに、同じ内容の第1ブート層と第2ブート層を格納する。そして、エラーのない方をRAMへコピーC2して(ステップS21)、RAM上でブート層プログラムを実行する(ステップS30)。そして、簡単なロゴなどの文字表示(第1画面表示)を行う(ステップS32)。次に、RAM上でシステム層プログラムを実行する(ステップS40)。そして、複数の画像の切り替えによる画面表示(第2画面表示)を行う(ステップS44)。

(もっと読む)

フラッシュメモリのデータ処理装置及び方法

本発明は、フラッシュメモリのデータ処理装置及び方法に関し、より詳しくはフラッシュメモリのデータに対する有効性を容易に判断し得るフラッシュメモリのデータ処理装置及び方法に関するものである。

本発明の実施形態によるフラッシュメモリのデータ処理装置は、所定の論理アドレスを用いてデータ演算を要請するユーザ要請部と、前記論理アドレスを物理アドレスに変換する変換部と、前記データから所定ビットの個数をカウントしたカウントデータを、前記データ演算実行時に前記データの有効性の可否を示すインデックス領域に記録する制御部とを含む。

(もっと読む)

(もっと読む)

情報処理装置

【課題】 情報処理装置に補助記憶手段であるメモリカードの使用状況を管理させることで、メモリカードの使用状況に起因する不具合を回避し、プログラム更新や最新データの管理を行う。

【解決手段】 情報処理装置は、情報管理部110により、補助記憶手段であるSDカード111(メモリカード107)の使用制限値の算出、および、使用状況の管理を行い、SDカード111の使用状況が使用制限値に近づいたときには、情報管理部110は、機器のコントロールパネル等にSDカード111の寿命が近いこと、SDカード111を交換する必要があること等のアナウンスを行う。なお、SDカード111の使用制限値の算出については、確保された領域に対する書き込み量、書き込み回数に基づいて常時、算出が行われる。

(もっと読む)

電子制御装置

【課題】給電の有無にかかわらずデータの保持機能を有するメモリを用いない場合であっても、所定の演算に用いられるデータである演算データをより適切に使用することのできる電子制御装置を提供する。

【解決手段】電子制御装置100では、機関始動前に取得される大気圧データがRAM114に書き込まれる。更に、この際、大気圧データの論理値を反転したデータである大気圧データの反転データもRAM114に書き込まれる。機関始動によってバッテリBの電圧が低下すると、マイクロコンピュータ110がリセットされる。このリセットからの復帰に際し、マイクロコンピュータ110では、大気圧データと大気圧データの反転データとがRAM114から読み出され、読み出された大気圧データの反転データが、読み出された大気圧データを論理反転したものに等しいか否かが判断される。

(もっと読む)

制御装置のデータ記憶装置

【課題】 本発明はメモリへの電源供給が遮断される前にメモリデータを保存することを課題とする。

【解決手段】 制御装置10は、2つの電源供給経路14,16が接続された電源回路24と、電源回路24から電源供給を受ける制御回路26と、制御データを記憶するSRAM28と、電源供給が遮断される直前にSRAM28のデータを記憶するEEPROM30とを有する。制御装置10は、バッテリ交換等によりSRAM28への電源供給が遮断される場合には、その前段階が検出された時点でEEPROM30にデータを移行しておき、SRAM28への電源供給が復旧された時点でEEPROM30のデータをSRAM28に復帰させる。これにより、バッテリ交換後も前と同じ制御データを用いた制御を行うことができるので、電源遮断時のメモリデータの復帰処理に対する信頼性がより高められている。

(もっと読む)

フラッシュメモリを使用して計量データをストアする方法

マルチセグメント化不揮発性フラッシュメモリ構造は、メータデータをストアし、更新し、保存するために少なくとも1つの関連メモリ構造と組み合わせて採用されている。初期にメータデータを関連メモリにストアすることにより、メータデータは、あらかじめ決めたデータ量が取得されるまで、あるいはメータへの電源が不能になる(124)までバッファに置かれており、その時点でストアされたメータデータはフラッシュメモリの選択されたブロックにコピーされる(126)。データを転送するための種々のロケーションは、それぞれフラッシュメモリのどのセグメントまたはブロックを利用するかを示すフラッシュポインタによって判断される。いくつかの実施形態では、関連メモリ構造のサイズは、関連メモリ構造が一杯になったときデータ転送を最大限にすると共に、フラッシュメモリに書かれる回数を少なくするためにフラッシュメモリの各セグメントのサイズに対応しており、もってフラッシュメモリの潜在的有効ライフスパンを延長している。  (もっと読む)

(もっと読む)

揮発性記憶装置をベースとする電源喪失回復機構

いくつかの実施形態によれば、アクティブ動作に関連する電源喪失回復情報が揮発性メモリに格納される。電源喪失状態が検出されると、電源喪失回復情報は不揮発性メモリにコピーされる。電源が復帰すると、電源喪失回復情報を使用して、中断された動作が完了又は補正される。 (もっと読む)

ブロックで消去可能なメモリの管理データレコードの再生方法。

本発明は、セクタで記述されかつブロックで消去可能な不揮発性メモリの管理データレコードを再生する方法であって、データレコードが、付属するメモリコントローラのアクセス可能な内部揮発性フラグメモリに保持されるものに関し、不揮発性メモリの1つ又は複数のメモリブロックにおいて、再構成表(RKT)が連続して実現され、この再構成表において、不揮発性メモリにおけるすべての書込み操作及び消去操作が、メモリコントローラの内部フラグメモリの管理データレコードが電源異常後再始動毎に完全に再構成されるような規模で、エントリとして記録される。  (もっと読む)

(もっと読む)

携帯電話の不揮発性メモリを管理するシステムおよび方法

本発明は、メモリ管理に関し、特に、携帯電話などの不揮発性メモリにアクセスし、これを管理する方法およびシステムに関する。携帯電話用メモリコントローラであって、携帯電話の不揮発性メモリに接続されるように構成された第1のインターフェース回路と、携帯電話の揮発性メモリに接続されるように構成された第2のインターフェース回路と、第1の携帯電話プロセッサに接続されるように構成され、前記携帯電話の揮発性メモリへのアクセスを前記第1のプロセッサに提供するように構成された第1のプロセッサインターフェースと、第2の携帯電話プロセッサに接続されるように構成された第2のプロセッサインターフェースと、携帯電話の不揮発性メモリのデータの少なくとも一部分を前記携帯電話の揮発性メモリにコピーするように構成されたコントローラ回路と、を備える携帯電話用メモリコントローラを開示する。  (もっと読む)

(もっと読む)

制御装置内のマイクロコントローラのメモリ領域を確実に検査する方法および保護されたマイクロコントローラを有する制御装置

本発明は,計算機コアと,少なくとも1つのリードオンリーメモリ領域と,少なくとも1つの再書込み可能なメモリ領域とを備えた,自動車内の制御装置内のマイクロコントローラを制御する方法に関するものであって,その場合に再書込み可能なメモリ領域内には,計算機コアによって処理するために設けられている,少なくとも1つの制御プログラムが記憶されている。マイクロコントローラのメモリの検査を許されない介入に対してより良好に保護する,制御装置内のマイクロコントローラを制御する方法を提供するために,検査プログラムを再書込み可能なメモリ領域の1回書込み可能なメモリ領域に記憶し,サービスプログラムをリードオンリーメモリ流域に記憶することが,提案される。検査プログラムは,規則的な間隔で制御プログラムによってサービスプログラムを用いて呼び出されて,再書込み可能なメモリ領域の少なくとも一部を検査する。サービスプログラムは,さらに,カウンタをリセットする。検査されたメモリ領域の操作が認識された場合に検査プログラムが,あるいはカウンタがオーバーフローした場合にカウンタが,制御装置のリセットを作動させる。  (もっと読む)

(もっと読む)

メモリカード

【課題】 データ書き込みの際に発生する消去テーブルの更新による不揮発性半導体メモリのメモリセルへのストレスを大幅に低減し、メモリカードの信頼性を向上させる。

【解決手段】 メモリカードのデータ書き込み時において、RAM11の消去テーブル格納部15に作成された消去テーブルから書き込み先アドレスを取得してデータを書き込んだ後、書き込みアドレスをアドレス変換テーブルに更新する。そして、消去テーブルに登録されている書き込み先アドレスを消去した後、更新前の旧データが書き込まれていたアドレスを登録する。消去テーブルをRAM11によって管理することにより、該消去テーブルの更新に伴うフラッシュメモリ3の書き換え回数を不要とし、メモリセルへのストレスを大幅に低減することができる。

(もっと読む)

データ記憶及び再生装置

データ記憶及び再生装置は、記憶媒体(通常はフラッシュメモリ回路)の性能の進化の測定値を使用して、記憶媒体のある領域からの取り出しの誤り率を予測する。予測は、データの格納に先立ちデータを符号化するECCを動的に選択するための基礎として使用される。前記情報が与えられると、所定の復号後誤り率しか生成しないと予測される最速の符号化可能なECCが選択されるように、使用可能な複数のECCからそのECCが選択される。このように、データを装置に送信する速度が最大にされ得ると同時に、復号後の予測される将来に、許容レベルを下回る誤り率を保持することができる。復号時、通常は音声データまたはビデオデータであるデータは、所定の速度で復号され、再生される。別の実施形態では、データは、複数のECCを使用して一緒に格納され、ECCは、出力データ転送速度が最大にされ、または再生時の消費電力が最低限に抑えられ得るように、復号用に動的に選択される。  (もっと読む)

(もっと読む)

バッドブロック管理部を含むフラッシュメモリシステム

【課題】 本発明はバッドブロックを管理するフラッシュメモリシステムに関する。

【解決手段】 本発明はフラッシュメモリ部100とバッドブロック管理部200とを含む。前記フラッシュメモリ部100はデータブロック130、予備ブロック110、および管理ブロック120を含む。そしてバッドブロック管理部200は前記管理ブロック120を参照して前記データブロック130の欠陥があるページアドレスを前記予備ブロック110のページアドレスに変換する。本発明によれば、バッドブロック発生時、コピーバック動作を実行しなくても良いという長所がある。

(もっと読む)

不揮発性メモリシステムにおける最低頻度消去ブロックの追跡

不揮発性メモリシステムにおいて摩耗一様化を実施する方法および装置が開示される。本発明の一態様によれば、メモリシステムの不揮発性メモリに含まれる要素を処理する1つの方法が、要素に関連付けられた消去カウントを得ることと、いくつかの要素を第1セットにグループ分けすることとを含む。各要素は、要素が消去された回数を実質的に示す関連付けられた消去カウントを有する。その数の要素を第1セットにグループ分けすることは、複数の要素に関連付けられた消去カウントの最低の関連付けられた消去カウントを有する複数の要素に含まれる要素を選択することを含む。方法は、第1セットに関連付けられた消去カウントを実質的に表内にあるメモリ構成要素に記憶することをも含む。  (もっと読む)

(もっと読む)

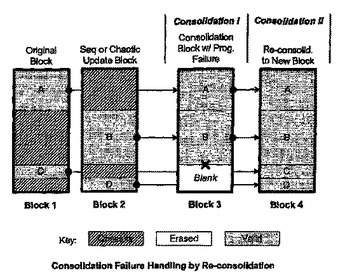

不揮発性メモリおよびフェーズ化されたプログラム障害処理を伴う方法

ブロック管理システムを伴うメモリにおいて、時間が重視されるメモリ動作中のブロック内のプログラム障害が、ブレークアウトブロック内のプログラミング動作を継続することによって処理される。後のあまり危機的でないときに、中断前に障害ブロック内に記録されたデータは他のブロックに転送され、この他のブロックもブレークアウトブロックであってもよい。その後、障害ブロックを廃棄することができる。このように、プログラミング中に不良ブロックが生じる場合に、データを失うこともなく、不良ブロック内に記憶されたデータを直ちに転送しなければならないことによって指定された時間制限を超えることもなく、不良ブロックを処理することができる。このエラー処理は、危機的な最中にすべての動作を新規のブロックに対して繰り返す必要がないようにするために、ガーベッジコレクションにとっては特に重要である。その後、都合のよいときに、不良ブロックからのデータは、他のブロックへ移転されることによって復旧される。  (もっと読む)

(もっと読む)

不揮発性メモリシステムのための内部メンテナンススケジュール要求

データ構造の更新がスケジュールされることを可能にするための方法および装置が、開示される。本発明の一態様によれば、複数の物理ブロックと、消去カウントブロックを含む複数のデータ構造とを含む不揮発性メモリを有するメモリシステムを動作させるための方法に、少なくとも1つのデータ構造の内容が、いつ更新されるべきであるかを判定することが関わる。内容が更新されるべきであると判定されると、データ構造の内容を更新する要求が、キューに入れられ、つまり、スケジュールされ、要求は、キューの先頭に事実上、達すると、実行される。  (もっと読む)

(もっと読む)

401 - 418 / 418

[ Back to top ]