Fターム[5B018MA35]の内容

記憶装置の信頼性向上技術 (13,264) | 対象 (1,668) | バス (45) | データ入出力回路 (17)

Fターム[5B018MA35]に分類される特許

1 - 17 / 17

半導体記憶装置

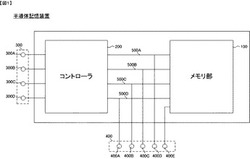

【課題】

実施形態は、解析が簡便な半導体記憶装置を提供する。

【解決手段】

本実施形態の半導体記憶装置は、メモリ部(100)と、前記メモリ部(100)に接

続されるコントローラ部(200)と、前記コントローラ部(200)に接続される第1

入出力部(300)と、前記メモリ部(100)と前記コントローラ部(200)の間の

ノードに電気的に接続され、前記第1入出力部(300)とは異なる第2入出力部(40

0)とを備える。

(もっと読む)

半導体装置、情報処理装置およびエラー検出方法

【課題】小規模な回路でデータ伝送動作の信頼性を高める。

【解決手段】(n−1)個(ただし、nは4以上の整数)の2ビット検査部210_0〜210_(n−2)のそれぞれは、1ビットの入力データを冗長化して得られたnビットの符号化データIの入力を受け、符号化データIにおけるそれぞれ異なるビット同士の比較結果に基づく2ビット検査データを出力する。全ビット検査部220は、符号化データIの全ビットの排他的論理和に基づく全ビット検査データを出力する。エラー検出部230は、(n−1)個の2ビット検査データと全ビット検査データとに基づいて符号化データIに対するエラー検出を行い、エラー検出結果に基づいて入力データを出力する。

(もっと読む)

メモリ回路及びメモリ回路制御方法

【課題】出力するデータ量を増加させることなく、チップ間のアドレスの転送誤りを検出することができるメモリ回路を提供すること

【解決手段】本発明のメモリ回路は、アドレス毎にデータが対応付けられたメモリ103を搭載するメモリチップ102と、メモリチップ102に接続されメモリ103のアドレスを指定してアドレスに対応するデータを読み出すメインチップ101と、を備える。メモリチップ102は、メインチップ101において指定され入力されたアドレスを取得するアドレス情報取得部105と、メモリ103内のデータをアドレスを用いて暗号化し、メインチップ101へ出力する暗号部104を備え、メインチップ101は、暗号部104から出力された暗号化データを、指定したアドレスを用いて復号化する復号部113と、復号化されたデータに誤りがあるか否かを判定する判定部116とを備えるものである。

(もっと読む)

記憶装置、基板、液体容器、データ記憶部に書き込むべきデータをホスト回路から受け付ける方法、ホスト回路に対し電気的に接続可能な記憶装置を含むシステム

【課題】記憶装置において、ホスト回路との通信の信頼性を向上する。

【解決手段】ホスト回路と電気的に接続される記憶装置は、不揮発性のデータ記憶部と、データ受信部と、判定部と、データ送信部とを備える。データ受信部は、ホスト回路からメモリアレイに書き込むべき第1のデータと、第1のデータに基づいて生成された第2のデータを受信する。判定部は、第1のデータと第2のデータとの整合性を判定する。データ送信部は、判定の結果をホスト回路に送信する。

(もっと読む)

半導体装置およびその試験方法

【課題】SIP型の半導体装置において、ロジックチップとメモリチップとの間の接続故障を特定して検出することができる半導体装置およびその試験方法を提供する。

【解決手段】複数のメモリ側パッドを有するメモリチップと、複数のメモリ側パッドのそれぞれに接続された、複数のコントローラ側パッドを有するメモリコントローラチップとからなる半導体装置において、コントローラチップに、コントローラ側パッドのそれぞれが入力に接続され、コントローラ側パッドから出力される信号のレベルに応じた試験信号を生成する複数の試験信号生成回路を設け、試験モードにおいて、信号を対応するコントローラ側パッドに出力した状態で、複数の試験信号生成回路のそれぞれが生成する試験信号を期待値と比較する。

(もっと読む)

メモリ制御装置及びその遅延量測定方法

【課題】 量産に適用されるような一般的なテスタでも遅延回路の遅延量の測定が可能なメモリ制御装置及びその遅延量測定方法を提供することを課題とする。

【解決手段】 本メモリ制御装置は、半導体記憶装置にデータを書き込むメモリ制御装置であって、入力信号を遅延させて出力する複数の遅延回路を有し、通常動作時に、前記複数の遅延回路は、互いに独立し、個々の遅延回路に入力される信号を個々に遅延して出力し、テスト動作時に、前記複数の遅延回路は、テスト用入力信号が全ての遅延回路を経由し、それぞれの遅延量の合計分だけ遅延するように接続され、遅延後の前記テスト用入力信号は、テスト用出力信号として、前記メモリ制御装置の外部に出力されていることを要件とする。

(もっと読む)

メモリコントローラ及び方法におけるデータ完全性

本開示は、メモリコントローラでのデータ完全性のための方法、装置、及びシステムを含む。1つのメモリコントローラの実施形態は、ホストインタフェース、及びホストインタフェースに結合される第1のエラー検出回路を含む。メモリコントローラは、メモリインタフェースと、メモリインタフェースに結合される第2のエラー検出回路を含むことができる。第1のエラー検出回路は、ホストインタフェースから受信されるデータに対してエラー検出データを計算し、ホストインタフェースに送信されるデータの完全性をチェックするように構成できる。第2のエラー検出回路は、メモリインタフェースに送信されるデータ及び第1のエラー訂正データに対してエラー訂正データを計算し、メモリインタフェースから受信されるデータ及び第1のエラー訂正データの完全性をチェックするように構成できる。 (もっと読む)

情報処理システムにおける接続装置の制御方法、制御プログラム及び情報処理装置

【課題】複数の共有記憶装置の格納情報が非対称になることを効果的に防止することを目的とする。

【解決手段】第1の接続装置に第1の共有記憶装置との接続を解除させ、第2の接続装置に第2の共有記憶装置との接続を解除させ、第1の接続装置とは異なる交換された他の第1の接続装置に第1の共有記憶装置と接続させ第2の接続装置に第2の共有記憶装置と接続させる。

(もっと読む)

DDRメモリーシステムにおいてデータの攪拌を用いる電源雑音の低減

【課題】

メモリーシステムにおいてジッターとタイミングの仕様に合致することは、ますます難しくなってきている。メモリーシステムの入出力周波数が増加し続けているからである。ジッターとタイミングのエラーの大部分は、電源雑音のせいである。

【解決手段】

本発明の実施例は一般にDDRメモリーシステムにおいてデータの攪拌を用いて電源雑音を低減するためのシステム、方法及び装置に向けられている。ある実施例では、集積回路は送信データ経路を含み、1つ以上のメモリー部品にデータを送信する。送信データ経路は攪拌論理を含んでもよい。攪拌論理は並列に互いに相関していないN個の疑似乱数出力を生成する。出力データと疑似乱数出力はXOR論理への入力となる。送信データ経路はXOR論理の出力を送信し、これは実質的に白色の周波数スペクトルを有する。他の実施例も記載し請求する。

(もっと読む)

回路間データ転送方法およびシステム

【課題】運用中にアドレス接続正常性の検証を可能とする回路間データ転送方法およびシステムを提供する。

【解決手段】回路5,6間でメモリ3を介してデータ転送を行う際に、メモリ3の転送用領域に書き込まれる転送データに所定アドレスカウント間隔で誤り訂正可能なエラービットを書き込み、メモリ3の転送用領域から読み出された転送データからエラーが検出されるアドレスカウント間隔を監視し(S504)、エラー検出間隔の異常を判別することで転送の正常性を検証する(S507、S508)。

(もっと読む)

無線通信機

【課題】安価かつ効率的にメモリデータの信頼性を向上させる技術を提供する。

【解決手段】伝送路誤り訂正処理のための符号化回路(15)及び復号化回路(14)を有する無線通信機であって、メモリ(13)にデータを書き込む際に、メモリ書き込み用の誤り訂正処理のための符号化回路(12)を用いて誤り訂正符号化処理を施してデータを書き込み、メモリ(13)からデータを読み込む際に、伝送路誤り訂正復号化処理を行う復号化回路(14)を用いて誤り訂正復号化処理を施してデータを読み込む。

(もっと読む)

エンベデッドメモリを利用したマルチチャンネルエラー訂正コーダを備えたメモリシステム及びその方法

【課題】エンベデッドメモリを利用したマルチチャンネルエラー訂正コーダ、それを備えたメモリシステム、及びその方法を提供する。

【解決手段】メモリシステムは、多数のメモリ装置と、多数のメモリ装置とデータ通信のための多数の通信チャンネルを含むメモリコントローラと、を備える。メモリコントローラは、多数の通信チャンネルを通じてメモリコントローラから伝達されるデータをエンコーディングするエラー訂正エンコーダ及び/または多数の通信チャンネルを通じてメモリコントローラに伝達されるデータでエラーを探索して訂正するエラー訂正デコーダを備える。

(もっと読む)

エラー制御コード装置およびその方法

エラー制御コード装置およびその方法を開示する。本発明の一実施形態に係るエラー制御コード装置は、MLC方式のメモリに適用されるエラー制御コード装置であって、バイパス制御信号を生成するバイパス制御信号生成部と、2つ以上のECCデコードブロックを含み、バイパス制御信号に基づいて2つ以上のECCデコードブロックのうちの一部のバイパス可否を決定してECCデコードを実行するECC実行部とを備える。また、本発明の他の一実施形態に係るエラー制御コード装置は、上記のECC実行部に加え、または上記のECC実行部の代わりに、2つ以上のECCデコードブロックを含み、バイパス制御信号に基づいて2つ以上のECCデコードブロックのうちの一部のバイパス可否を決定してECCエンコードを実行するECC実行部を備えることができる。  (もっと読む)

(もっと読む)

画像入出力装置及び画像入出力方法

【課題】電源投入時でOSが起動する前のコントローラ内部診断(自己診断)字に、もれなくDRAM−I/Fの結線チェックが出来る画像入出力装置及び画像入出力方法を提供する。

【解決手段】機能限定されたメモリマップ領域内に、すべてのCS領域のメモリ空間をアサインすることにより、電源投入時でOSが起動する前のコントローラ内部診断(自己診断)時に、もれなくDRAM−I/Fの結線チェックが出来る画像入出力装置及び画像入出力方法の提供を実現することができる。

(もっと読む)

制御情報、読み出しデータおよび/または書き込みデータにおけるエラーを検出および識別するシステム

集積回路メモリまたはバッファ装置などの集積回路、方法およびシステムが、実施形態の中でも特に、制御情報、書き込みデータおよび読み出しデータトランザクションにそれぞれ対応する、CRC符号などの複数のエラー符号を生成する。複数の別個に生成されたCRC符号は、循環バッファなどのそれぞれの記憶回路にログまたは記憶される。次に、各トランザクションに対応する、記憶された複数のCRC符号を用いて、エラーが特定のトランザクション中に発生したかどうか、ひいては、特定のトランザクションの再試行が行われるかどうかを判定する。集積回路には、集積回路によって生成されたCRC符号を、コントローラ装置によって提供されたCRC符号と比較する比較回路が含まれる。読み出しデータに対応するCRC符号は、読み出しトランザクション中に用いられていないデータマスク信号線を用いて、コントローラ装置に転送される。次に、集積回路によって生成されたCRC符号を、コントローラ装置によって生成されたCRC符号と比較して、エラーが発生したかどうかを判定してもよい。コントローラ装置は、制御情報、書き込みデータおよび読み出しデータに対応する複数のCRC符号を生成および記憶する。次に、コントローラ装置は、コントローラ装置によって生成されたCRC符号を、集積回路において生成および記憶されたCRC符号と比較して、エラーが、特定のトランザクション中に発生したかどうかを判定する。  (もっと読む)

(もっと読む)

順方向エラー訂正コードをデコードするためのシステム及び方法

デコーダの状態を更新(又は、再計算)するために遅延パケット到着に含まれる情報を使用することによって順方向エラー訂正コードのデコーダの性能を向上させることができるシステム及び方法が開示される。一般に、開示された実施例のシステム及び方法は、連続するビット又は情報フレームのデコードで状態情報を維持するデコーダに適用できる。もし遅延パケットに含まれる情報が当初は時間通りに到着し、通常の方法でデコードされていたら、再計算された状態はデコーダが正確に有していた状態であるから、本発明の方法及びシステムはデコーダの性能(即ち、ビットエラーレート)を向上させる。事実上、遅延パケット到着に続いてデコーダ状態を更新することは、デコーダの状態に遅延パケット消去が影響する時間での伝搬を終了させる。  (もっと読む)

(もっと読む)

セグメント・レベルの予備化を実現するシステム、方法、およびプログラム

【課題】 セグメント・レベルで予備化したメモリ・システムを提供する。

【解決手段】 このメモリ・システムはセグメント・レベルで予備化した、カスケード型相互接続システムを含んでいる。このカスケード型相互接続システムは少なくとも2つのメモリ・アセンブリとメモリ・バスを備えている。このメモリ・バスは複数のセグメントを備え、このメモリ・アセンブリは当該メモリ・バスを介して相互接続されている。

(もっと読む)

1 - 17 / 17

[ Back to top ]