Fターム[5B018QA13]の内容

記憶装置の信頼性向上技術 (13,264) | 時期 (2,030) | 試験、診断、検査モード時 (156)

Fターム[5B018QA13]に分類される特許

1 - 20 / 156

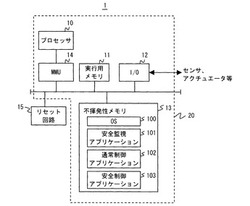

情報処理装置およびメモリ管理装置の動作確認方法

【課題】仮想アドレスを物理アドレスに変換するメモリ管理装置が正常に動作しているか否かを確認可能とする。

【解決手段】情報処理装置1は、メモリ11と、メモリ11の物理アドレス又はそれに対応する仮想アドレスを指定することで、メモリ11の物理アドレスに対してデータの読み出し又は書き込みを行うためのシステムプログラムと、システムプログラムを実行するプロセッサ10と、プロセッサ10からのメモリ11に対する仮想アドレスを指定した読み出し及び書き込みにおいて、仮想アドレスを物理アドレスに変換するメモリ管理装置14を備える。プロセッサ10は、システムプログラムによって、物理アドレスを指定してデータの書き込みを実施した後、その物理アドレスに対応する仮想アドレスを指定してデータの読み出しを実施して、書き込んだデータと、読み出したデータが一致するか否かを判定する。

(もっと読む)

半導体記憶装置

【課題】

実施形態は、解析が簡便な半導体記憶装置を提供する。

【解決手段】

本実施形態の半導体記憶装置は、メモリ部(100)と、前記メモリ部(100)に接

続されるコントローラ部(200)と、前記コントローラ部(200)に接続される第1

入出力部(300)と、前記メモリ部(100)と前記コントローラ部(200)の間の

ノードに電気的に接続され、前記第1入出力部(300)とは異なる第2入出力部(40

0)とを備える。

(もっと読む)

情報処理装置及び記憶部検査方法

【課題】CPUの運用中においても、記憶部の検査のためにCPUによるソフトウェアのデータ処理を一時停止させることがなく、記憶部の異常の有無をチェックすることができる情報処理装置及び記憶部検査方法を提供する。

【解決手段】CPU1とは独立に設置された記憶制御部2は、CPU1から書き込みようの処理データと書き込み先の記憶部3の指定アドレスを受け、検査用データを指定アドレスに書き込み、それを読み出す。記憶制御部2が備えるデータチェック部20は、検査用データと読み出されたデータとを比較し、一致するかどうかを判定する。一致しなければ指定アドレスに異常があると判定し、その旨をCPU1に通知し、一致すれば、記憶制御部は処理データを指定アドレスに書き込む。

(もっと読む)

メモリモジュール検査システム、情報処理装置及び記憶装置

【課題】情報処理装置に装着された状態のメモリモジュールを検査できるメモリモジュール検査システム、情報処理装置、及びメモリモジュールの検査に必要なデータを記憶する記憶装置を提供する。

【解決手段】記憶装置2は、情報処理装置1で使用されるメモリモジュール4の正しい仕様を示す仕様データを仕様データ記憶部5で記憶している。情報処理装置1は、仕様データ記憶部5から仕様データを読み出し、メモリモジュール4のSPDメモリ(不揮発性メモリ)41に記憶している仕様データが正しいか否かを判定し、正しくない場合はSPDメモリ41の記憶内容を書き換える。また、記憶装置2のプログラム記憶部25は、メモリモジュール4の検査に必要なプログラムを記憶しており、情報処理装置1は、プログラム記憶部25からダウンロードしたプログラムに従ってメモリモジュール4の検査の処理を実行する。

(もっと読む)

半導体装置

【課題】データの誤書換を防止することが可能な低消費電力の半導体装置を提供する。

【解決手段】マイクロコンピュータ1は、電源電圧VCCが正常範囲から外れた場合にリセット信号REを出力する電圧検出器2と、各々がデータを不揮発的に記憶する複数のメモリセルを含むメモリアレイ5と、イレーズコマンドまたはプログラムコマンドに応答して、電圧検出器2の応答時間TR以上の保留時間TSだけ経過した後にデータのイレーズまたはプログラムを実行し、リセット信号REに応答してリセットされる制御部7とを備える。したがって、電圧検出器2の応答時間TRが長い場合でも、データの誤書換を防止できる。

(もっと読む)

情報処理端末及び管理サーバ

【課題】フラッシュメモリに書き込まれたデータの信頼性を向上することができる技術を提供することを課題とする。

【解決手段】メモリカード7Aは、コンテンツデータAを記録するメモリ71と、メモリコントローラ72とを備える。メモリコントローラ72は、メモリ71のエラーブロックのアドレスを記録したエラー発生データ75Aを作成する。エラー発生データ75Aは、情報処理端末4を介して、集計サーバ1に送信される。集計サーバ1は、複数の情報処理端末から受信したエラー発生データ75Aを集計して、メモリ71において検査対象となる検査領域を設定し、検査領域が記録された個別検査領域データ16Aを作成する。情報処理端末4は、個別検査領域データ16Aを集計サーバ1から取得して、メモリコントローラ72に出力する。メモリコントローラ72は、個別検査領域データ16Aに基づいて、メモリ71で検査する領域を決定する。

(もっと読む)

メモリ制御装置、画像処理装置、メモリ制御方法、メモリ制御プログラム及び記録媒体

【課題】ダブルレート型メモリの使用領域を有効活用しつつ使用環境に適したメモリアクセスを適切に行う。

【解決手段】複合装置は、メモリコントロール機能部30によって複数のパラメータに基づいてアクセスされるダブルレート型のメモリ13の所定の記憶領域を調整対象メモリ領域として、該調整対象メモリ領域のデータをメモリデータ記憶機能部22へコピーし、所定タイミングに、メモリデータ記憶機能部22のデータを、メモリ13の該調整対象メモリ領域へ書き戻して該調整対象メモリ領域のデータと比較してパラメータを決定して、メモリコントロール機能部30へ該メモリコントロール機能部30がメモリ13へのアクセスに用いるパラメータとして設定する。

(もっと読む)

メモリシステム

【課題】

実施形態は、信頼性を向上可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムによれば、複数のワード線と、複数のビット線と、制御ゲートに前記ワード線が接続され、ドレイン端に前記ビット線が接続されたメモリセルと、複数の前記メモリセルを含むページ、複数の前記ページを含むブロックを有するメモリセルアレイと、前記ページごとに不良の前記ビットの個数が第1閾値以下である良ブロックに関するデータが保持された記憶領域とを備え、前記第1閾値は、不良ブロックか否かの判定に用いる第2閾値よりも小さいことを特徴とする。

(もっと読む)

車両用ドア駆動制御検査装置、車両用ドア駆動制御検査方法および車両用ドア駆動制御検査プログラム

【課題】簡易な装置にて異常個所をフィールドで特定することが可能な車両用ドア駆動制御検査装置を提供する。

【解決手段】書き込み指令手段202は、デュアルポートRAM101に接続されたCPU1、4に対してデュアルポートRAM101に対する書き込み指令を行い、読み出しデータ受信手段203は、CPU1、4にてデュアルポートRAM101から読み出された読み出しデータを受信し、故障診断手段204は、書き込み指令手段202にて指令された書き込みデータと、読み出しデータ受信手段203にて受信された読み出しデータとの比較結果に基づいて、デュアルポートRAM101の故障を診断する。

(もっと読む)

欠陥フラッシュメモリダイの動作不能化

【課題】複数のフラッシュメモリダイを含むデバイス内の欠陥フラッシュメモリダイを動作不能化する製品ならびに関連する方法およびシステムを提供する。

【解決手段】動作不能化されていないフラッシュメモリダイに基づくフラッシュメモリのデータ記憶容量を示すラベルを、複数のフラッシュメモリダイを含むパッケージに付すことができる。ダイレベル、パッケージレベル、および/またはボードレベルにおいて、様々な動作不能化方法を適用することができる。

(もっと読む)

メモリ装置の診断方法及びメモリ装置の診断装置並びに情報処理装置

【課題】メモリ装置を備えた情報処理装置の、処理上のスループットを低下させることなく、かつ高い信頼性を維持して該メモリ装置の故障診断を行うこと。

【解決手段】

アドレス予測部11は、情報処理装置3を構成するCPU付属のメモリ装置に対し、メモリアクセスの状況(より具体的には、キャッシュラインが保持するキャッシュライン管理情報など)から判断して、近々に書き込みアクセスが発生することになると予測されるメモリのアドレス情報の特定を行う。次に、通達部12は、アドレス予測部11が特定した前記アドレス情報を、メモリ診断部に送出する。これにより、メモリ診断部は、CPU付属のメモリ装置(図示は省略)の、該特定されたアドレス情報が示す記憶領域のみを目下の診断対象とすることができる。

(もっと読む)

試験方法,試験プログラム,及び試験装置

【課題】情報処理装置の記憶部に対する試験にかかる時間の短縮又は試験精度の向上を実現する。

【解決手段】同一の基礎パターンを隣り合わせて配設した基礎パターン対を含むテストパターン42を、記憶部4の試験領域40のうちの第1領域40Aに書き込み、書き込まれた前記テストパターン42を前記試験領域40のうちの第2領域40Bに転送し、転送されたテストパターン42を、前記第1領域40Aにおける前記書き込みが行なわれたアドレスから所定のシフト量だけシフトされたアドレスに転送するとともに、前記第1領域40Aあるいは前記第2領域40Bの一方から他方に転送されたテストパターンにおける基礎パターン対の隣り合わせて配設された基礎パターン同士が等しいか否かを比較、判定することにより前記試験領域40に対する書き込み及び読み出しを正しく行なえるか否かを検証する。

(もっと読む)

携帯可能電子装置およびICカード

【課題】プログラムコードの自己診断が特定のコマンド処理時間に影響を与えることを避けるための分散処理、および、本装置がほとんど非活性化〜(再)活性化されない利用シーンにおける、プログラムコード自己診断の定期実施を可能とする携帯可能電子装置およびICカードを提供する。

【解決手段】ROMに格納されたプログラムコードを自己診断する自己診断機能を持つICカードにおいて、プログラムコードの自己診断を1つのコマンド処理内で全て実行するのではなく、複数のコマンド処理に分けて分散実行する。

(もっと読む)

フラッシュメモリをテストするための方法、システム、および、コンピュータで読み取り可能なコード

【課題】フラッシュメモリ・ダイをテストするための方法、システムおよびデバイスを得る。

【解決手段】デバイス製造のポスト・ウェファ・ソート・ステージ中に、共通ハウジングに関連づけられたフラッシュコントローラ・ダイおよび少なくとも一つのフラッシュメモリ・ダイを各々が含む複数のフラッシュメモリ・デバイスを、例えば、バッチ・テスト・プロセスまたはマス・テスト・プロセス等のテスト・プロセスへ通す。テスト中、各フラッシュコントローラ・ダイ上に属するフラッシュコントローラが、各フラッシュ・デバイスの一つ以上のフラッシュメモリ・ダイの各々をテストするための、少なくとも一つのテスト・プログラムを実行する。少なくとも100個のフラッシュメモリ・デバイスおよびマス・テスト・ボードを含むテスト・システムを開示する。さらに、フラッシュコントローラが一つ以上のフラッシュメモリ・ダイをテストするよう作動可能なフラッシュメモリ・デバイスを開示する。模範的なテストは、不良ブロック・テストを含む。

(もっと読む)

複数のアクセスコマンドを並行して実行するメモリ装置及び同装置におけるメモリアクセス方法

【課題】ブロック単位のメモリアクセス処理を、小容量のメモリ領域を用いた管理で高速に実行できるようにする。

【解決手段】実施形態によれば、メモリ装置のメモリインタフェースは、複数のアクセスコマンドに従ってメモリに並行してアクセスする。コマンド生成手段は所定のアクセス処理において、メモリインタフェースに複数のアクセスコマンドを投機的に投入する。アクセスコマンド返却手段は、メモリインタフェースに既に投入済みの、エラー発生時点で未実行のアクセスコマンド群を、対応するパージレスポンスにより返却する。コマンド進捗管理手段は、返却された未実行のアクセスコマンド群のうちの最も古いアクセスコマンドを指すようにコマンド進捗管理情報を更新する。コマンド生成手段は、更新された情報に基づき、返却された未実行のアクセスコマンド群をメモリインタフェースに再投入する。

(もっと読む)

メモリコントローラ及び情報処理システム

【課題】メモリモジュールの故障に対して早急な処置を行うことを可能とし、情報処理システムの信頼性を向上させることを可能にするメモリコントローラ及び情報処理システムを提供する。

【解決手段】メモリコントローラ及び情報処理システムにおいて、メモリモジュールから読出されたデータのエラー検出を行うエラー検出部と、メモリコントローラを通常モードから故障検査モードに切り替え、複数の単位メモリ領域におけるそれぞれの検査対象のデータ記録済アドレスからデータを読出し、該読出しデータのエラーを前記エラー検出部により検出させて、故障検査を実行させる故障検査制御部と、故障検査制御部による検査結果における各単位メモリ領域のエラー検出状況に基づいて、メモリモジュール内部の故障に起因するメモリ故障と、メモリモジュール外部のデータ伝送路の故障に起因する伝送路故障を判定する判定部を備える。

(もっと読む)

不揮発性メモリの初期化装置および初期化方法

【課題】不揮発性メモリの初期化の手順の簡略化を図るとともに検査装置を検査に必要な最少限の構成とする。

【解決手段】予め不揮発性メモリの特定の値を書き換える信号を電子制御装置に入力し、電源投入により不揮発性メモリに対してイニシャル処理を行い、イニシャル処理で不揮発性メモリの初期化が必要と判断されたとき、前記書き換え信号により、不揮発性メモリに対して不揮発性メモリの特定の値を書き換える初期化処理を行う。

(もっと読む)

タイミング検証装置、及びタイミング検証方法

【課題】アドレスのセットアップ(Setup)違反とホールド(Hold)違反が同じクロックのイベントに対して発生した場合に、アドレスのタイミング違反が発生しても、仮想イベントを発生させることなく、対象の違反アドレスを正しく判定する。

【解決手段】イベントドリブン方式を用いた論理シミュレーションに適用される半導体装置内蔵ランダムアクセスメモリのタイミング検証装置において、クロック信号にイベントが発生した場合、当該ランダムアクセスメモリのアドレス違反処理用レジスタに現状のアドレス情報を格納する。また、アドレスのタイミング違反を確認する。また、タイミング違反を確認した結果に基づき、タイミング違反時にアドレス違反処理用レジスタの値を不定値にする。また、タイミング違反レジスタの値に基づき、違反アドレスをチェックする。

(もっと読む)

電子装置、及び、これを用いた電動パワーステアリング装置

【課題】アドレスバスおよびデータバスの故障を検出する電子装置において、故障検出に係る処理負荷を低減し処理速度を向上する。

【解決手段】電子装置は、CPUとROMとを接続しアドレスを伝送する4つ以上のバスラインからなるアドレスバス21を備える。電子装置は、アドレスバス検査用アドレスAdによって指定されるROM領域13aから値を読み出し、読み出した値から計算した判定値Vjと予め計算されたアドレスバス検査用正解値Vtとを比較し、一致しない場合、アドレスバス21が故障していると判定する。アドレスバス検査用アドレスAdは、4つ以上のバスラインに対応する4ビット以上の値であって、2ビット以上の0の値と2ビット以上の1の値とを有する値を含み、複数のバスライン間の短絡故障を同時に検出可能である。これにより、故障検出に必要な検査用アドレスAdの数を低減することができる。

(もっと読む)

擬似エラー発生装置

【課題】半導体メモリに擬似的にエラーを発生させる擬似エラー発生装置を提供する。

【解決手段】乱数によって決定されるメモリのアドレスのデータの情報ビットと冗長ビットの両方を、エラー検出やエラー訂正しないで読み取り、同じく乱数によって決定されるビット位置のビットを反転させ、同じメモリの同じアドレスにビット反転させたデータを書き込む。反転させるビット数は、どのようなエラーを擬似的に発生させたいかによって、1ビット、2ビット以上など、適切に設定する。

(もっと読む)

1 - 20 / 156

[ Back to top ]