Fターム[5B018QA16]の内容

記憶装置の信頼性向上技術 (13,264) | 時期 (2,030) | リード/ライト動作時 (307)

Fターム[5B018QA16]に分類される特許

1 - 20 / 307

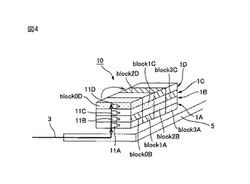

メモリモジュールおよび半導体記憶装置

【課題】電流の集中や発熱の集中を低減することができるメモリモジュールおよび半導体記憶装置の提供を図る。

【解決手段】複数のメモリチップ1A〜1Dが積層されたメモリモジュール10であって、前記各メモリチップは、複数のブロックに分割されたメモリセル部block0〜block3と、入力アドレス信号を処理して、動作させるブロックを選択するアドレススクランブル回路11A〜11Dと、を有する。

(もっと読む)

記憶制御装置、記憶装置、情報処理システム、および、それらにおける処理方法

【課題】メモリ内の一群のデータ列に対するエラー訂正コードの付与規則を柔軟に設定する。

【解決手段】記憶制御装置は、エラー訂正コード付与規則保持部とエラー訂正部とを備える。エラー訂正コード付与規則保持部は、メモリ内の一群のデータ列に対するエラー訂正コードの付与規則を一群のデータ列のアドレスごとに対応付けて保持する。エラー訂正部は、メモリに対してアクセスが発生した場合にそのアクセスアドレスに対応付けられた付与規則に従ってメモリ内の一群のデータ列についてエラー訂正を行う。

(もっと読む)

半導体メモリ装置および復号方法

【課題】復号効率がよい半導体メモリ装置1を提供する

【解決手段】半導体メモリ装置1は、半導体メモリ部3と、LDPC符号化データをサムプロダクトアルゴリズムを用い復号する復号部18と、を具備し、復号部18が、検査行列の行毎に、行処理演算と列処理演算とからなるイタレーション処理を繰り返し実行することで事後尤度比を更新するときに、列処理演算において事後尤度比の絶対値が閾値以上の場合、列要素尤度比には事後尤度比をそのまま使用し、事後尤度更新処理において、列要素尤度比の絶対値が前記閾値以上の場合、事後尤度比には列要素尤度比をそのまま使用する。

(もっと読む)

不揮発性メモリの正常性情報を取得して使用するためのシステム及び方法

【課題】不揮発性メモリ(「NVM」)の正常性情報を取得して使用するためのシステム及び方法を提供する。

【解決手段】正常性情報は、NVMの一部で検出されたエラー数、又は不揮発性メモリの一部から読み取りを行うために又はこのメモリの一部をプログラムするために必要な時間量などの、NVM装置の一部の性能及び信頼性に関連する様々な情報を含むことができる。動作中、ホスト装置上にアドレス固有の正常性情報を受動的に記憶し、コマンドの一部としてメモリコントローラに提供することができる。メモリコントローラは、このコマンドから正常性情報を抽出し、この情報を使用してアクセス要求を実行することができる。アクセス要求の完了後、メモリコントローラは正常性情報を更新し、この情報をホスト装置へ返送することができる。

(もっと読む)

メモリコントローラ、記憶装置

【課題】読み出し動作の高速化及び信頼性の向上に有利なメモリコントローラ、記憶装置を提供する。

【解決手段】実施形態によれば、メモリコントローラ2は、外部インタフェイス1と、第1のECC生成部3aと、メモリ7a〜7eに対する書き込み及び読み出しを制御するアクセス部4と、読み出しデータのエラーを訂正する第1のECC訂正部3bと、これらを制御する制御部6とを具備する。前記制御部6は、メモリからデータを読み出す際に、第1の読み出し単位でデータを読み出し、前記第1の読み出し単位で読み出したデータにエラーが発生した場合に、前記第1の読み出し単位よりも読み出しサイズが小さい第2の読み出し単位に切り替えてデータを読み出し、前記第2の読み出し単位で読み出したデータに対して、前記第1のECC訂正部により前記第1のECC符号を利用してエラー訂正を行うように制御を行う。

(もっと読む)

メモリコントローラ、半導体記憶システムおよびメモリ制御方法

【課題】パリティデータデータの増大を抑えることができるメモリコントローラを得ること。

【解決手段】各しきい値分布に対して、3ビットのデータが割り当てられ、第1のビットが第1ページのデータを表現し、第2のビットが第2ページのデータを表現し、第3のビットが第3ページのデータを表現する3ビット/セルのメモリセルを有する不揮発性半導体メモリを制御するメモリコントローラであって、不揮発性半導体メモリの第1のメモリ領域に、第1〜第3の3ページ分のデータを書き込む場合に、第1のメモリ領域の各メモリセルに書き込まれるデータの第1のビット及び第2のビットから、隣接するしきい値分布への移動によりエラーとなるビットを抽出して仮想ページを生成する制御部と、仮想ページに対する第1の誤り訂正符号を生成する符号化部と、3ページ分のデータと第1の誤り訂正符号とを不揮発性半導体メモリへ書き込むインターフェイス部とを備える。

(もっと読む)

共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置

【課題】共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置を提供する。

【解決手段】メモリ・システム100は、ホスト110とメモリ・デバイス120との間でデータを転送するためにデータ・フレームを使用する。いくつかの場合には、システムは(別個のビット・レーンを介してではなく)データ・フレーム内で一つまたは複数のデータ・マスク・ビットも転送してもよい。システムは、データ・ビットおよびデータ・マスク・ビットをカバーするエラー・ビット・チェックサム(巡回冗長符号すなわちCRCのような)を生成してもよい。いくつかの実施形態では、データ・ビット、データ・マスク・ビットおよびチェックサム・ビットは共通フレームにおいて転送される。

(もっと読む)

情報処理装置および情報処理方法

【課題】複数の半導体メモリをストレージとして用いる場合のトータル的な応答性の向上を図ることのできる情報処理装置を提供する。

【解決手段】この情報処理装置は、複数の半導体メモリそれぞれの物理的特性を評価して、評価結果に見合った用途属性を、少なくとも一部の半導体メモリに割り当てる割当部と、データのライト命令に対して当該データのライト先として最適な用途属性の前記半導体メモリを判定する判定部とを具備する。複数の半導体メモリの物理的特性に個体差がある場合に、その半導体メモリの物理的特性が活かされるようにデータのライト先が判定部にて判定される。これにより、複数の半導体メモリを1つのストレージとして用いた場合のストレージのトータル的な応答性の向上を期待できる。

(もっと読む)

情報記憶装置および情報記憶方法

【課題】記憶部に半導体メモリを利用する情報記憶装置において、情報の記憶に利用できない記憶領域の発生を抑制すること。

【解決手段】本実施形態にかかる情報記憶装置は、半導体メモリと、管理手段と、を具備して構成される。この半導体メモリは、情報を記憶するための記憶領域を有する。また、管理手段は、半導体メモリの記憶領域のうちリードエラーの発生する回数が2以上となった記憶領域を情報の記憶の利用から除外するように管理する。

(もっと読む)

メモリ電圧制御装置およびメモリ電圧制御方法

【課題】メモリを低電圧で制御して省電力制御を図ることおよびエラーの発生を防止することを改善できるメモリ電圧制御装置およびメモリ電圧制御方法を提供する。

【解決手段】メモリ電圧制御装置10およびメモリ電圧制御方法は、デバイス13,14と、デバイス13,14の異常を検出する電気機器11と、を備え、電気機器11は、デバイス13,14の異常を検出した時に、デバイス13,14に対して動的または静的に駆動電圧を昇圧する制御を行う。

(もっと読む)

情報処理装置、画像形成装置およびプログラム

【課題】プログラムの誤動作の発生を抑制する。

【解決手段】動作制御部は、プログラムを実行するCPUと、プログラムを格納するとともにプログラムの実行に伴って発生するデータを格納するメインメモリ512とを有している。メインメモリ512は、読み書き可能であって、電源を供給しなくても、記憶している情報を保持することが可能なMRAM61と、電源を供給しないと、記憶している情報を保持することができないDRAM62とを備えており、MRAM61の一部領域にはプログラム等が格納されるROM領域A1が設けられ、MRAM61の残りの領域およびDRAM62のすべての領域にはデータ等が格納されるRAM領域A2が設けられる。CPUがリセットされると、ROM領域A1の記憶内容をそのままとする一方でRAM領域A2の記憶内容を消去し、ROM領域A1から読み出したプログラムを実行する。

(もっと読む)

メモリ制御装置

【課題】H/Wの無駄が生じることがなく、高速に処理可能なメモリ制御装置を実現する。

【解決手段】メモリ制御装置1000は、ペイロードをペイロード領域に格納し、パリティデータをパリティ領域に格納する実メモリ004を制御する。ペイロード/パリティ領域アドレス計算部001は、ペイロードとパリティデータのビット数の比をペイロード/パリティ比104として入力し、実メモリ004の領域をペイロード/パリティ比に近似させてペイロード領域とパリティ領域とに分類した結果ペイロード領域に分類される領域の数を分割比103として入力し、実メモリ004のメモリアドレス長102を入力し、ペイロードのメモリアドレス101を入力し、これらを用いて、当該ペイロードに対応するパリティデータのパリティ領域でのメモリアドレスを算出する。

(もっと読む)

メモリコントローラ及び不揮発性記憶装置

【課題】不揮発性メモリにてワード線不良によるバースト誤りが発生した場合も、格納したデータを正しく読み出せる不揮発性記憶装置、及びメモリコントローラを提供する。

【解決手段】不揮発性記憶装置は、データを記憶する不揮発性メモリと、不揮発性メモリの制御を行うメモリコントローラとを備え、不揮発性メモリは、ブロックを複数含み、ブロックは、ページを複数含み、ブロック内には、一つのワード線を共有する2以上のページからなるページの組が少なくとも一つ存在し、メモリコントローラは、データを格納するページであるデータページと、データページの誤り訂正演算のための符号を格納する誤り訂正符号ページとを、夫々一つ以上含む、誤り訂正グループを複数構成し、同一の誤り訂正グループにおける、データページと誤り訂正ページの夫々に対してワード線の異なるページを割り当てる。

(もっと読む)

メモリコントローラ及び不揮発性記憶装置

【課題】不揮発性メモリにおいて第1の誤り訂正符号の訂正能力を超えるエラーが発生した場合でも、格納したデータを正しく読み出すことが可能で、かつ、小さいサイズの書き込みが効率的な不揮発性記憶装置、及びメモリコントローラを提供する。

【解決手段】不揮発性記憶装置は、データを記憶する不揮発性メモリと、不揮発性メモリの制御を行うメモリコントローラとを備え、メモリコントローラは、データと同一ページに格納する第1の誤り訂正符号とは別に、第2の誤り訂正符号をも格納する。所定のサイズよりも小さい書き込みにおいては、前記第2の誤り訂正符号を付与せず、データと同一ページに格納する第1の誤り訂正符号を、異なるページに二重化して格納する。データの読み出し時にはデータに付与された第1及び/または第2の誤り訂正符号を用いてエラー訂正を行う。同一論理アドレスに対して、いずれの論理ブロックに有効なデータが格納されているかを管理するための有効データ管理テーブルを備えている

(もっと読む)

メモリコントローラ、不揮発性記憶装置

【課題】不揮発性メモリにおいて第1の誤り訂正符号の訂正能力を超えるエラーが発生した場合でも、格納したデータを正しく読み出すことが可能で、かつ、小さいサイズの書き込みが効率的な不揮発性記憶装置、及びメモリコントローラを提供する。

【解決手段】不揮発性記憶装置1は、データを記憶する不揮発性メモリ12と、不揮発性メモリ12の制御を行うメモリコントローラ11とを備え、メモリコントローラ11は、データと同一ページに格納する第1の誤り訂正符号とは別に、第2の誤り訂正符号をも格納する。第2の誤り訂正符号の単位となるパリティグループよりもサイズの小さい書き込みにおいては、パリティグループとは別の領域に暫定的な第2の誤り訂正符号を格納する。データの読み出し時にはデータに付与された第1及び/または第2の誤り訂正符号を用いてエラー訂正を行う。

(もっと読む)

不揮発性メモリ、メモリコントローラ、不揮発性メモリのアクセス方法、およびプログラム

【課題】メモリセルとしてバイト単位のアクセスが可能であり、求められるアクセスに対して最適な単位でECC処理を行うことが可能な不揮発性メモリ、メモリコントローラ、不揮発性メモリのアクセス方法、およびプログラムを提供する。

【解決手段】ワード単位でアクセス可能で固定レイテンシでアクセス可能な第1アクセスモードと可変レイテンシでアクセス可能な第2アクセスモードによりアクセス可能な不揮発性メモリセルアレイを少なくとも含む不揮発性メモリセルデバイスと、第1アクセス経路に配置され、第1アクセスモード時にメモリセルアレイから出力されたデータに対してECCを適用した誤り検出処理および訂正処理を行う第1ECC処理部と、第2アクセス経路に配置され、第2アクセスモード時にメモリセルアレイから出力されたデータに対してECCを適用した誤り検出処理および訂正処理を行う第2ECC処理部とを有する。

(もっと読む)

ICカード及びICカードのリフレッシュ方法

【課題】リフレッシュ処理中に発生した不測の電源断により、フラッシュメモリに保持されているデータが破損することを防止できるICカードを提供する。

【解決手段】ICカード1には、ICカード1に実装されたフラッシュメモリをリフレッシュ処理できるように、フラッシュメモリに保持されているデータをページ単位で取得し、フラッシュメモリにページ単位で該データを再書き込みするリフレッシュ処理を実行するリフレッシュモジュール12が実装され、コマンド実行中にリフレッシュ処理を行えるように、外部装置からコマンドを受信すると、該コマンドを処理した後、リフレッシュモジュール12を作動させるトリガー条件が成立していると、リフレッシュモジュール12を呼び出し、リフレッシュモジュール12の処理が終了すると、該コマンドのレスポンスを外部装置へ送信するコマンド管理モジュール10が実装される。

(もっと読む)

データ記憶装置及びデータ処理装置及びコンピュータプログラム及びデータ記憶方法

【課題】実装面積を増大させることなく、ソフトエラーの発生を検出し、訂正できるようにする。

【解決手段】演算装置101(演算部)は、所定の演算により、複数の入力データ501に基づいて、誤り検出データ503を算出する。記憶装置102は、複数の入力データ501と、誤り検出データ503を記憶する。データ生成装置104(判定部・訂正部)は、記憶装置102が記憶した複数の入力データと記憶装置102が記憶した誤り検出データとの間に整合性があるか判定し、整合性がない場合、記憶装置102が記憶した複数の入力データと記憶装置102が記憶した誤り検出データとのうちから、誤っているデータを判定し、誤っていると判定したデータについて、正しいデータを算出する。

(もっと読む)

記憶装置、コンピュータ装置、コンピュータの制御方法、およびコンピュータプログラム

【課題】データの保持期間を長くする。

【解決手段】コンピュータシステムは、パーソナルコンピュータなどのホスト10と、ホスト10に接続されるUSBメモリデバイス100とを備える。USBメモリデバイス100は、ユーザ用データを格納するためのNAND型フラッシュメモリ130と、OTPメモリ140とを備える。NAND型フラッシュメモリ130には、ユーザ用データ以外に、ユーザ用データに対応した第1次のエラー訂正用符号であるECC_Aとが格納される。一方、OTPメモリ140には、ECC_Aに対応した第2次のエラー訂正用符号であるECC_Bが格納される。

(もっと読む)

半導体装置、情報処理装置およびエラー検出方法

【課題】小規模な回路でデータ伝送動作の信頼性を高める。

【解決手段】(n−1)個(ただし、nは4以上の整数)の2ビット検査部210_0〜210_(n−2)のそれぞれは、1ビットの入力データを冗長化して得られたnビットの符号化データIの入力を受け、符号化データIにおけるそれぞれ異なるビット同士の比較結果に基づく2ビット検査データを出力する。全ビット検査部220は、符号化データIの全ビットの排他的論理和に基づく全ビット検査データを出力する。エラー検出部230は、(n−1)個の2ビット検査データと全ビット検査データとに基づいて符号化データIに対するエラー検出を行い、エラー検出結果に基づいて入力データを出力する。

(もっと読む)

1 - 20 / 307

[ Back to top ]