Fターム[5B022BA02]の内容

Fターム[5B022BA02]に分類される特許

1 - 20 / 26

データ処理装置およびそのデータ処理方法

【課題】可変長データに対する演算処理と、固定長データに対する演算処理とを効率的に行なうことが可能なデータ処理装置を提供すること。

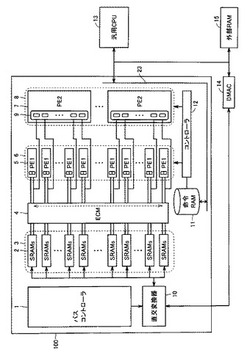

【解決手段】データ処理装置100は、SIMD方式の複数のPE1(5)と、複数のPE1(5)のそれぞれに対応して設けられる複数のSRAMs2と、複数のPE2(7)とを含む。複数のPE1(5)のそれぞれは、対応する1つのSRAMs2に格納されるデータに対して演算を行なう。また、複数のPE2(7)のそれぞれは、対応する複数個のSRAMs2に格納されるデータに対して演算を行なう。したがって、複数のSRAMs2を共有することができ、可変長データに対する演算処理と、固定長データに対する演算処理とを効率的に行なうことが可能となる。

(もっと読む)

ルートi(√i)演算の保持を特徴とする基数8固定小数点FFT論理回路

【課題】 高速フーリエ変換(FFT)演算の丸め誤差を軽減させること。

【解決手段】 バタフライ演算(8p)に含まれる複素平面上の回転因子のうちで、無理数(√、平方根)として現れるデータを意図的に計算することなく、多段にパイプライン化されているFFTの複数の段のうちの1つの段に設けられているメモリに保持(preserve)しておき、後段において再度現れたきたら、2つの回転因子を掛け合わせる演算を行う。このことによって、基数8 (radix-8)のバタフライ演算8p中の丸め誤差を無くすることができる。基数2 (radix-s)または基数4 (radix-4)のバタフライ演算によって、さらなる段を被せるように応用することもできる。

(もっと読む)

OFDM方式における演算処理装置および演算処理方法

【課題】移動端末が送信するデータの周波数帯域幅に応じて、適切な固定小数点数のフォーマットでデータを出力するFFT演算処理装置およびFFT演算処理方法を提供することである。

【解決手段】本発明に係る演算処理装置は、第1のビット数の固定小数点数で表された無線信号のデータを、前記第1のビット数よりも大きい第2のビット数の固定小数点数として演算して、前記第2のビット数の固定小数点数のデータに変換するFFT演算部10と、前記無線信号の使用周波数の程度に応じて定まるビット切り出し位置に従って、前記第2のビット数のデータから、指定ビット数のデータを切り出すビット切り出し部20と、

を備える。

(もっと読む)

演算装置及び演算方法

【課題】 浮動小数点積和演算あるいは固定小数点乗算がそれぞれ実行される場合に、無効な電力消費が発生するという問題点がある。

【解決手段】 通知された演算命令に基づいて選択した入力データを構成する複数の部分データそれぞれについて最上位ビットから連続している0の数を計数して第1のリーディングゼロカウントとし、第1のリーディングゼロカウントに基づいて入力データについて最上位ビットから連続している0の数を計数して第2のリーディングゼロカウントを出力するリーディングゼロ手段と、第1のリーディングゼロカウントを入力して演算命令に基づいた演算を行うとともに、第2のリーディングゼロカウントを入力して演算命令に基づいた演算を行う第1の演算手段と、第1の演算手段及びリーディングゼロ手段と連携して演算命令に基づいた演算を行う第2の演算手段とを有する。

(もっと読む)

情報処理装置、演算処理方法及び電子機器

【課題】同一データを用いた乗算結果を固定小数点フォーマット及び浮動小数点フォーマットで同時に出力できる情報処理装置、演算処理方法及び電子機器等を提供する。

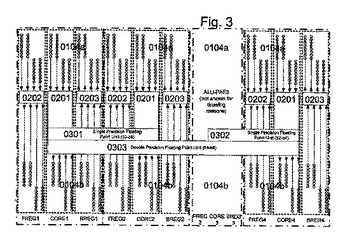

【解決手段】情報処理装置は、第1及び第2の設定データの読み出し及び書き込み可能に構成される第1及び第2の入力レジスターと、前記第1の入力レジスターに設定された前記第1の設定データと前記第2の入力レジスターに設定された前記第2の設定データとを用いた乗算処理の結果を、固定小数点フォーマットの第1の乗算データとして出力する第1の処理ユニットと、前記第1の入力レジスターに設定された前記第1の設定データと前記第2の入力レジスターに設定された前記第2の設定データとを用いた乗算処理の結果を、浮動小数点フォーマットの第2の乗算データとして出力する第2の処理ユニットと、前記第1及び第2の乗算データが格納される第1及び第2の出力レジスターとを含む。

(もっと読む)

演算器、プロセッサ、コンパイル処理装置およびコンパイル処理方法

【課題】条件データに基づいて浮動小数点型データの符号を高速に変換する。

【解決手段】信号線149には、符号が付加される対象である浮動小数点型の対象データが供給される。信号線148には、その対象データに符号を付加する条件を含む条件データが供給される。符号データ生成部200は、信号線148からの条件データに含まれている条件を抽出して、この抽出された条件に基づいて、信号線149からの対象データに符号を付加するための符号データを生成する。符号付加部300は、信号線149を介して供給される対象データを整数型のデータとして整数演算することによって、符号データ生成部200からの符号データと信号線149からの対象データとに基づいて対象データに符号を付加する。

(もっと読む)

サーボモータ制御用の浮動少数点数演算機能付き演算処理装置

【課題】整数と浮動小数点数が混在して実行される制御演算を実行する場合、フォーマット変換が必要であり、このために演算性能が低下するという課題があった。

【解決手段】命令にオペランドで指示される入力および出力データに対してフォーマット変換を指示する変換フラグを備え、パイプラインのデコード段に、変換フラグを参照し入力データに対してフォーマット変換を行い、実行段の入力データを作成するフォーマット変換部を備え、パイプラインのライトバック段に、変換フラグを参照し実行段の演算器の演算結果に対してフォーマット変換を行い、ライトバック段のデータおよびフォワーディングのため実行段に与える入力データを作成するフォーマット変換部を備えた。

(もっと読む)

組み込み制御装置

【課題】浮動小数点数形式のデータによる演算精度を確保し、且つ、記憶装置の記憶領域の不足を回避することができる組み込み制御装置を提供する。

【解決手段】本発明による組込み制御装置によると、浮動小数点数形式の離散的データを読み取り専用記憶装置に格納するとき、浮動小数点数形式の離散的データを、仮数部短縮型浮動小数点数形式のデータに変換してから格納する。ここに、仮数部短縮型浮動小数点数とは、浮動小数点数の仮数部のうち下位ビットを削除したものである。更に、離散的データから補間演算を行うとき、読み取り専用記憶装置に格納された仮数部短縮型浮動小数点数形式の離散的データを浮動小数点数形式の離散的データに戻してから、補間演算を行う。

(もっと読む)

リコンフィギュラブルな浮動小数点レベルおよびビットレベルのデータ処理ユニット

リコンフィギュラブルなデータ処理ユニットの複数の固定小数点ユニットのブロックが、該ブロック内に固定実装された共通の同じハードウェアによって、浮動小数点数を効率的に演算する機能を支援する。  (もっと読む)

(もっと読む)

マイクロコントローラ及び制御システム

【課題】浮動小数点演算を行うためのプログラムコード、特にその変数によるコード量の増加を抑制し、また、固定小数点データを浮動小数点データに変換するための処理オーバヘッドを軽減する。

【解決手段】制御システムに、固定小数点データとして整数データとそれに対する小数点位置データとを入力し、入力データから浮動小数点型の仮数部、指数部及び符号を求めて浮動小数点型データに変換する浮動小数点変換器(32)と、前記浮動小数点変換器の出力を受け浮動小数点データの演算を行う浮動小数点演算器(38)と、を有するマイクロコントローラ(1)を採用する。前記浮動小数点変換器は、前記整数データに対する仮数部のシフト量と前記小数点位置データ(EXP2)との加減算により指数部を取得する。

(もっと読む)

変換装置

【課題】マルチキャリア信号に対して、浮動小数点数から固定小数点数への変換を実行する場合に、信号の値に応じてビット幅の位置を調節したい。

【解決手段】ビット変換部34は、FFT部32から、周波数領域に変換されたマルチキャリア信号であって、かつ浮動小数点数として示されたマルチキャリア信号を入力する。ビット変換部34は、マルチキャリア信号を形成している複数のサブキャリアのそれぞれに対して、最上位のビット位置を特定し、特定した最上位のビット位置をもとに、複数のサブキャリアのそれぞれに対して共通に使用すべきビット幅の位置を決定する。また、ビット変換部34は、決定したビット幅の位置を使用しながら、浮動小数点数から固定小数点数へマルチキャリア信号を変換する。ビット変換部34は、変換したマルチキャリア信号を、固定小数点数の演算を実行する受信処理部38へ出力する。

(もっと読む)

固定小数点表示と浮動小数点表示との間で数を変換するデータ処理装置および方法

【課題】固定小数点表示と浮動小数点表示との間で数を変換するデータ処理装置および方法を提供する。

【解決手段】データ処理装置は、インストラクションを実行するよう動作可能なデータ処理ユニットを備え、そのデータ処理ユニットは、フォーマット変換インストラクションに応答し、数にフォーマット変換演算を適用してその数の固定小数点表示と浮動小数点表示との間で変換を行う。更には、その数の固定小数点表示内の小数点位置を特定するプログラム可能な値を提供する制御フィールドが配置され、データ処理ユニットは、その制御フィールドを参照し、かつプログラム可能な値に従ってフォーマット変換演算を制御する。これによって、単一インストラクションを用いて、小数点の位置がプログラム可能である固定小数点フォーマットと浮動小数点表示との間で直接変換することが可能となる。

(もっと読む)

浮動小数点演算装置とこの装置を用いたレーダ信号処理装置

【課題】 処理対象データが固定小数点フォーマットで浮動小数点フォーマットに変換する必要があってもフィルタ演算全体の処理時間を短縮可能とする。

【解決手段】 入力直後のフィルタ演算を固定小数点演算で実施し、その演算結果を浮動小数点フォーマットに変換する構成とする。ここで、浮動小数点演算を扱えるDSPでは、計算と浮動小数点変換を同時に実行することが可能であることに着目し、計算命令、メモリアクセス命令、浮動小数点変換命令を最適に組み合わせ、従来、入力直後に独立して行っていた浮動小数点変換処理をその後のフィルタ演算で同時に実行する。この構成により、浮動小数点変換処理の効率が高められ、処理時間が極小となる。

(もっと読む)

演算プログラム変換装置、演算プログラム変換プログラム、演算プログラム変換方法

【課題】演算プログラムにおける浮動小数点演算を、所望精度を確保しながら固定小数点演算に変換する演算プログラム変換装置、演算プログラム変換プログラム、演算プログラム変換方法を提供する。

【解決手段】浮動小数点演算を行う演算プログラムにおける浮動小数点型の変数を対象変数とし、演算プログラムの実行時に対象変数の値の変化が履歴として出力されるように、演算プログラムの変更を行って実行を行い、該実行により得られる履歴に基づいて対象変数の値の範囲を検出するプロファイル部と、プロファイル部により検出された対象変数の値の範囲に基づいて、対象変数を固定小数点型に変換するように、演算プログラムの変更を行って実行を行い、該実行により得られる実行結果の精度が予め設定された所望精度を満たすか否かの判断を行う変換部とを備えた。

(もっと読む)

演算処理装置,制御装置およびプログラム

【課題】浮動小数点演算プロセッサの異常を検出するための技術を提供する。

【解決手段】制御装置1において、マイコン10のCPU11は、異常検出処理にてFPU17により演算された制御パラメータ,および,CPU11自身が演算した制御パラメータにより算出された目標トルクそれぞれを、固定小数点型のデータにて比較する。ここで、FPU17に異常が発生している場合、FPU17による目標トルクは、CPU11自身による目標トルクとは異なるものとなる。そして、CPU11は、そのような目標トルクの相違をもって、FPU17に異常が発生しているか否かを判定して検出することができる。

(もっと読む)

処理装置

【課題】 回路規模の縮小化に貢献するリコンフィギュラブル回路を備えた処理

装置を提供する。

【解決手段】 本発明による処理装置10は、1つの回路を分割した複数の分割

回路をリコンフィギュラブル回路12上に順次構成し、ある分割回路の出力を次

の分割回路の入力にフィードバックして分割回路における演算処理を実行し、最

後に構成された分割回路から出力を取り出す。フィードバックパスとして、リコ

ンフィギュラブル回路12の出力をその入力に接続する経路部24を形成する。

分割回路を順次構成することによって、全体として1つの回路を実現できる。

(もっと読む)

ビット長検出器、ビット長検出方法及びビット長検出プログラム

【課題】入力データのビット数が大きく変動する場合にもビット数を高速に検出すること。

【解決手段】入力データビット長検出部120は、最初にRビットを検査対象ビットブロックとし、基準位置からRビットを二等分して上位半分のビットブロックと下位半分のビットブロックとに分けたビット分木初期位置まで前記上位半分のビットブロックを選択して右シフトし、右シフトの結果に基づいて当該上位半分のビットブロックと前記下位半分のビットブロックのいずれかを次の検査対象ビットブロックとして選択し、当該選択された次の検査対象ビットブロックの上位半分のビットブロックを選択して右シフトする動作を繰り返して、ビット分木終了位置まで右シフトして最終シフトビット数累積値を求め、当該最終シフトビット数累積値と前記動作において最後に検査対象ビットブロックとして選択されたビットのデータの値とを加算して入力データのビット長を検出する。

(もっと読む)

ブロックフローティング方法及び装置

【課題】 本発明はブロックフローティング方法及び装置に関し、1データのみの振幅が大きいデータが入力された場合、線形システムにおける演算誤差を抑えることができることを目的としている。

【解決手段】入力データを受けて平均ブロックパワーを算出する平均ブロックパワー算出処理部501と、該平均ブロックパワー算出処理部501の出力を受けて、データの正規化処理を行なう正規化シフト数算出処理部301と、正規化シフト数だけの正規化を行なうブロックデータ正規化処理部302と、該ブロックデータ正規化処理部302の出力を受けて、所定の演算を実施する線形システム303と、該線形システム303の出力と前記正規化シフト数算出処理部の出力を受けて前記正規化シフト数だけ線形システムの出力データを右シフトして本来の結果へ戻す処理を行なう後処理部304とを具備して構成される。

(もっと読む)

飽和あり、または飽和なしで、オペランドの積和を実行するプロセッサ簡約ユニット

毎回加算後に飽和するか、または毎回加算の結果をラップ・アラウンドするかを選択して、m個の入力オペランドにアキュムレータ値を加えた総和をとる簡約ユニットを備えるプロセッサを提供すること。簡約ユニットは、さらに、入力オペランドのビットを単純に反転し、複数の簡約加算器のそれぞれへのキャリーを1に設定することにより複数のm個の入力オペランドをアキュムレータ値から引くことができる。簡約ユニットをm個の並列乗算器と併用し、ドット積および他のベクトル演算を飽和算術演算またラップアラウンド算術演算とともに高速実行することができる。

(もっと読む)

(もっと読む)

事前の飽和検出を備えた加算もしくは減算用の算術演算装置

各々がそれぞれ下位部分と上位部分のような第1の部分と第2の部分に分割可能である少なくとも第1および第2の入力オペランドに算術演算を実行するための算術演算装置である。この算術演算装置は第1の演算回路、第2の演算回路、選択回路、および飽和回路を有する。桁上げ伝搬加算器を含むことが可能である第1の演算回路は、少なくとも暫定合計および桁上げ出力を発生させるために入力オペランドの第1の部分を処理する。二重加算器および事前の飽和検出器を含むことが可能である第2の演算回路は、1つまたは複数の暫定合計およびいくつかの飽和フラグを発生させるために入力オペランドの第2の部分を処理する。選択回路は、第1の演算回路の桁上げ出力に基づいて第2の演算回路の1つまたは複数の出力を選択するように構成される。飽和回路は第1の演算回路および選択回路の対応する出力部に連結された入力部を有し、算術演算の結果を発生させるように構成される。

(もっと読む)

(もっと読む)

1 - 20 / 26

[ Back to top ]