Fターム[5B047EA02]の内容

Fターム[5B047EA02]に分類される特許

1 - 20 / 148

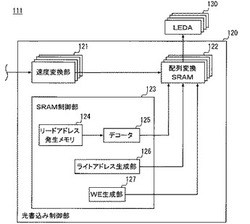

光書込み装置、画像形成装置及び光書込み装置の制御方法

【課題】アドレス変換テーブルを設けることにより異なる種類のLEDAに対応可能な光書込み装置の装置構成を効率化する。

【解決手段】形成すべき画像を構成する画素の情報である画素情報を取得する速度変換部121と、画素情報の配列を変換する配列変換SRAM122と、感光体を露光する光源に応じた画素情報の配列の変換態様を示すアドレス変換テーブルを取得して記憶するリードアドレス発生メモリ124と、画素情報の配列の変換を制御するためのライトアドレス信号を生成して出力するデコータ125とを含み、前記リードアドレス発生メモリ124は、同時にアクセス可能な複数の記憶領域に分割されており、アドレス変換テーブルを複数の記憶領域に分割して記憶する。

(もっと読む)

画像処理装置

【課題】 画像処理装置において、プロセッサーやメモリーなどのリソースに対する負荷を小さくしつつ、属性データと画像データとを仮想アドレス空間内でそれぞれ連続させる。

【解決手段】 画像形成装置1において、データ生成部22は、複数ページ画像のそれぞれについて、ページ画像内の各画素の色および/または階調を示す画像データとページ画像内の各画素の属性を示す属性データとを、順番に生成しRAM12に記憶する。そして、マッピング設定部23は、複数ページ画像についての属性データが仮想アドレス空間で連続するように、また、複数ページ画像についての画像データが仮想アドレス空間で連続するように、マッピングデータ21aを設定する。

(もっと読む)

情報絞り込み検出機能を備えたメモリ、その使用方法、このメモリを含む装置。

【課題】

パターン認識など情報検出の最大の課題は検索時間でありメモリの逐次比較処理が不要な非ノイマン型情報検出メモリを実現する。

【解決方法】

メモリアドレスごとに情報を記憶しその情報を読み出し可能なメモリで、このメモリは、外部から与えられる第1のデータは記憶されたメモリのデータを比較するためのデータ、第2のデータはアドレス同士を比較するためのデータ、の双方の入力データの入力手段と、この入力手段から与えられた上記双方の入力データにより記憶された情報のデータと、そのアドレスと、の双方を二重並列に合否判定し、その双方の合否判定結果をさらに並列に論理演算する手段と、上記論理演算に合格するこのメモリの上記アドレスを出力する手段と、を具備することを特徴とする情報絞り込み検出機能を備えたメモリであるのでインテリジェンスな情報検索はもとより人工知能等に広く利用可能である。

(もっと読む)

画像処理装置、画像処理システム及び画像処理方法

【課題】シングルポートのSRAMを用いて画像処理装置の処理効率を改善する。

【解決手段】画像処理装置10は、複数の変換前画素値を記憶するメインメモリ30と、複数のキャッシュブロックを有するキャッシュメモリ20とに接続される。カウンタと、座標決定部と、メモリコントローラと、キャッシュアクセス部と、画素値計算部と、出力部とを備える。メモリコントローラは、メインメモリ30に記憶された複数の変換前画素値をそれぞれ、変換前座標に応じたキャッシュブロックへ転送する。キャッシュアクセス部は、複数のキャッシュブロックから、変換後画素値の計算に必要な全ての変換前画素値を1回のキャッシュアクセスで読み出す。画素値計算部は、キャッシュアクセス部が読み出した変換前画素値を参照して、変換後画素値を計算する。出力部は、変換後画素値を出力する。

(もっと読む)

画像処理装置および画像処理プログラム

【課題】並列処理される画像処理の一部をハードウェア処理する複数のアクセラレータを用いて画像処理を行う際に、複数設けられたアクセラレータの利用効率を向上させる。

【解決手段】DMAバッファ50の実アドレスを連続した論理アドレス空間上の共通バッファ領域70にマッピングし、RIP処理部90は共通バッファ70にて空いたDMAバッファをDMA転送制御ライブラリ30に問い合わせて獲得し、任意のアクセラレータ80に処理を引き継ぐ中間データを書き込み続く処理をデバイス選択部20に要求する。デバイス選択部20は、RIP処理部90から通知される論理DMAバッファ33の共通バッファ領域70におけるオフセットを任意の空いているアクセラレータ80を制御するドライバ60に通知してアクセラレータ80に対する中間データのDMA転送および転送した中間データの処理を指示する。

(もっと読む)

画像回転装置及び画像形成装置

【課題】画像の回転に利用される記憶部の容量を小さく抑えることが可能な画像回転装置及び画像形成装置を提供する。

【解決手段】画像回転装置1は、画像データの書込み方向と画像データの読み出し方向が同一の方向であり、且つ、第1方向における所定のバースト長に対応する画素数と、第1方向に直交する第2方向の画素数とが同一である第1記憶部11と、第3方向の画素数が第1記憶部11における第1方向の画素数と同一であると共に、第3方向に直交する第4方向の画素数が第1記憶部11における第2方向の画素数よりも少ない第2記憶部12と、第1記憶部11に記憶される画像データを所定のバースト長に対応する画素数のデータ毎に読み出して第2記憶部12に書き込むことと、第2記憶部12に記憶されるデータを所定のバースト長に対応する画素数のデータ毎に読み出して第1記憶部11に書き込むことと、を行う読出書込部20と、を備える。

(もっと読む)

画像読取装置及び画像処理装置

【課題】原稿の画像を複数のブロックに分割し、ブロック単位で画像を読み取った場合に、再生された画像の画像品位が低下するのを抑制することができるようにする。

【解決手段】原稿の画像を読み取る読取部と、画像の読取画像データを生成する画像読取制御部21と、読取画像データを記録するための記憶部と、記憶部における使用可能記憶容量に応じて原稿の画像を複数のブロックに分割するブロック読取制御処理手段と、原稿の画像を複数のブロックに分割する際に、所定のラインがブロック分割ラインとして適しているかどうかを判断するブロック分割ライン判定処理手段とを有する。記憶部の記憶容量を小さくすることができ、画像読取装置のコストを低くすることができる。

(もっと読む)

画像処理装置、画像処理システム、及びバンク管理方法

【課題】様々な動作周期及び動作開始タイミングに適切に対応できるようにバンク管理を行なう画像処理装置、画像処理システム、及びバンク管理方法を提供する。

【解決手段】画像処理装置は、3つのバンク領域を示す3つのアドレスを格納する第1乃至第3のアドレスレジスタと、フラグと、入力画像切り替わりのタイミングで第1のアドレスレジスタと第2のアドレスレジスタとの間で格納アドレスを入れ替えるとともにフラグをセットし、第1のアドレスレジスタの格納アドレスを入力画像書き込みアドレスとして供給する画像入力バンク管理部と、フラグがセット状態の場合、処理画像切り替わりのタイミングで第2のアドレスレジスタと第3のアドレスレジスタとの間で格納アドレスを入れ替えるとともにフラグをリセットし、第3のアドレスレジスタの格納アドレスを処理画像読み出しアドレスとして供給する画像処理バンク管理部とを含むことを特徴とする。

(もっと読む)

データ処理装置およびデータ処理方法

【課題】データの転送効率を維持した状態で、データ転送に係る消費電力を低減することができるデータ処理装置およびデータ処理方法を提供する。

【解決手段】入力データを第1および第2の分離データに分離する第1のビット分離部と、n(nは1以上の自然数)回目とn+1回目の第1の分離データとを比較するビット比較部と、比較結果に基づいて第1の分離データを反転するか否かを判定した反転情報を出力するビット判定部と、反転情報に基づいて選択したデータを出力する第1のビット反転部と、選択したデータと第2の分離データとを配置し、反転情報を結合して出力する第1のビット結合部と、を具備し、順次入力された複数の入力データを転送データに変換して順次転送する際に、1つの転送データを1つの転送単位とし、予め定められた数の転送単位を1つの変換単位として、入力データを変換単位毎に配置するデータ変換部、を備える。

(もっと読む)

データ処理装置およびデータ処理方法

【課題】データの転送効率を維持した状態で、データ転送に係る消費電力を低減することができるデータ処理装置およびデータ処理方法を提供する。

【解決手段】入力データを予め定められたそれぞれの配置方法に基づいて配置した第1の変換データを生成する複数のデータ生成部と、対応するデータ生成部が出力したn(nは1以上の自然数)回目とn+1回目の第1の変換データ内の各ビットの値を比較し、該比較した結果に基づいたビットの数をビット変化数として算出する複数のビット変化数算出部と、それぞれのビット変化数の値を比較してデータ生成部を選択し、選択情報を出力するビット変化数比較部と、選択情報に基づいて選択した、いずれか1つの第1の変換データを選択データとして出力する第1のデータ選択部と、選択データを転送データとして出力する際に、予め定められた未使用ビットの位置に選択情報を結合して出力するビット結合部と、を具備する。

(もっと読む)

データ処理装置およびデータ処理方法

【課題】データの転送効率を維持した状態で、データ転送に係る消費電力を低減することができるデータ処理装置およびデータ処理方法を提供する。

【解決手段】入力データを順次データバスに配置した第1の転送データを生成するデータ生成部と、データバスのビット幅を、予め定められたビット数の複数の単位ビットに分割し、第1の転送データ内に配置されたデータの配置を、単位ビット毎に並べ替えた変更データを生成し、該生成した変更データと、並べ替えられたデータの配置を表す並べ替え情報とを、転送データとして出力する第1のデータ配置変更部と、を具備し、順次入力された複数の入力データを、予め定められたビット数のデータバスと同じビット数の転送データに変換して順次転送する際に、1つの転送データを1つの転送単位とし、予め定められた数の転送単位を1つの変換単位として、入力データを変換単位毎に配置するデータ変換部、を備える。

(もっと読む)

画像変形装置および命令付加装置

【課題】キャッシュミスのないアクセスを可能にする。

【解決手段】画像変形装置10は、画像を格納するフレームメモリ12と、フレームメモリ12に格納された画像に施す変形処理パラメータP1にプリフェッチ命令P2が付加されたプリフェッチ命令付変形処理パラメータP3を格納するパラメータメモリ13と、フレームメモリ12に格納された画像の画素データの一部を一時的に格納することで、フレームメモリ12からの画素データ読み込み効率を向上させるキャッシュメモリ14と、パラメータメモリ13に格納されたプリフェッチ命令P2に従ってフレームメモリ12からキャッシュメモリ14に画素データをロードするプリフェッチ制御部15と、パラメータメモリ13に格納された変形処理パラメータP1を使用してキャッシュメモリ14に格納された画像に変形処理を施す変形処理部16とを備える。

(もっと読む)

画像処理装置及び画像処理システム

【課題】キャッシュメモリの利用効率及び外部メモリへのアクセスレイテンシを改善する。

【解決手段】画像処理装置10は、外部メモリ30及びキャッシュメモリ20に接続される。画像処理装置10は、カウンタ11と、座標計算部12と、タグチェッカ13と、画素参照部15と、画素値計算部16と、出力部17と、を備える。カウンタ11は、所定の実行順に従って変換後座標を決定する。座標計算部12は、変換後座標に位置する変換後画素の変換後画素値を計算するための変換前座標を計算する。タグチェッカ13は、変換前画素を参照して変換後画素値を計算することを要求する変換要求を生成する。画素参照部15は、変換要求に基づいて、変換前座標に位置する変換前画素がキャッシュメモリ20に記憶されている場合に、変換前画素をキャッシュメモリ20から読み出す。画素値計算部16は、読み出された変換前画素を参照して、変換後画素値を計算する。出力部17は、変換後画素を外部メモリ30に書き込む。

(もっと読む)

画像処理装置及び画像形成装置

【課題】低消費電力化を図れる画像処理装置を提供する。

【解決手段】書込読出制御部53は第1及び第2のラインメモリ51a,51bの中から読み出し可能なラインメモリと書き込み可能なラインメモリとを交互に切り換える制御する。1ラインの画像データが上記ラインメモリに書き込まれる際に、白ライン判定部31はそのラインの画像データに対応する画像が白ラインか否か判定する。白ラインであれば、画像処理制御部23はそのラインの画像データをラインメモリから読み出す読出クロックCLK3及び画像処理部27で使用される動作クロックCLK4の生成を停止する。

(もっと読む)

画像書込み装置および画像形成装置

【課題】注目画素を取巻く主・副走査の画素を格納機能から同時に取出して、注目画素に対してデータ識別できることにより、1画素単位での線画を忠実に認識するデジタル発光素子書込み装置を提供する。

【解決手段】注目ラインの副走査3ライン目の画素を順にマトリクス判断していく。主走査5の画素101では、マトリクスより縦線と判断できる。ここで2値データから4値のコード化に変換する場合、偶数画素か奇数画素かも判断し、縦パターンの奇数と判断すると画素101は、01bコードとなる。さらに画素102では、横線の奇数と判断し、11bコードとなり、画素103は、0データの奇数で00bコード、画素104では、1dot孤立点の偶数と判断し、10bコード、画素105では、斜め線の偶数と判断し11bコードとなる。注目画素を取巻く主・副の画素を格納機能から同時に取出すことで、1画素単位で忠実に線画を表現する。

(もっと読む)

メモリ制御方法、メモリ制御装置、および画像形成装置

【課題】シリアル−パラレル変換とパラレル−シリアル変換を効率的に実行する。

【解決手段】画像処理前のラインデータを記憶するラインメモリと画像処理後のラインデータを記憶するラインメモリとを同一素子で構成し、シリアルデータ形式で入力されるラインデータをラインメモリで記憶する処理前・メモリ入力タイミング,記憶された処理前のラインデータをパラレルデータ形式で読み出す処理前・メモリ出力タイミング,処理後のパラレルデータ形式のラインデータをラインメモリで記憶する処理後・メモリ入力タイミング,記憶された処理後のラインデータをシリアルデータ形式で読み出す処理後・メモリ出力タイミング,の4タイミングで制御し、同一ライン周期内に処理前・メモリ出力タイミングの直後に処理後・メモリ入力タイミングを実行すると共に、同一ライン周期内に処理後・メモリ出力タイミングの直後に処理前・メモリ入力タイミングを実行する。

(もっと読む)

集約画像出力装置及び画像形成装置

【課題】集約画像データを記憶することなく、外部に出力することが可能な集約画像出力装置及び画像形成装置を提供する。

【解決手段】集約画像出力装置100は、複数の画像データを記憶する第1記憶部81と、画像データに基づく画像を副走査方向に配列し且つ主走査方向に沿った複数のラインに分割するように画像データを複数に分割して、分割画像データを第1記憶部81から順次読み出す読出部と、第1記憶部81に記憶される複数の画像データのうちいずれの画像データに対応する分割画像データを読出部111によって読み出すのかを設定する読出設定部114と、外部に順次出力される集約画像データのアドレスが第1先頭アドレス又は第2先頭アドレスに到達した場合に、読出部111によって読み出された分割画像データを、集約画像データを構成する一部のデータとして外部に出力する形成出力部115とを備える。

(もっと読む)

データ処理装置およびデータ処理方法

【課題】複数データの夫々に対し、2次元パラメータの夫々を配列規則を損なうことなく対応させながら、大掛かりなキャッシュメモリを用いることなく、高速処理することが可能なデータ処理方法を提供する。

【解決手段】外部メモリ406に格納された2次元テーブルに、前回読み出したM行のパラメータに連続するM行のパラメータが存在する場合は、このM行のパラメータを新たなパラメータとしてキャッシュメモリ404の内容を更新する。また、2次元テーブルに、前回読み出したM行のパラメータに連続するM行のパラメータが存在しない場合は、2次元テーブルの先頭の行に戻って連続するM行のパラメータを、新たなパラメータとしてキャッシュメモリ404の内容を更新する。このような更新の規則を、処理の単位であるバンドが切り替わる場合であっても、またバンド処理の途中であっても維持する。

(もっと読む)

画像処理装置

【課題】CCDやCIS、CMOS等の画像データの出力順の異なるラインセンサーから出力された画像データの並べ替えを自在に行うことができる画像処理装置を提供する。

【解決手段】画像処理装置は、ラインセンサーで読み込まれた画像データを1又は複数のチャネルに分割して入力する画像データ入力端子26〜29と、入力された画像データを記憶する2ポートRAM1と、入力された画像データを2ポートRAM1の特定のメモリアドレスに書き込むために該メモリアドレスを指示するルックアップテーブル8〜11と、入力された画像データを2ポートRAM1の指示されたメモリアドレスに書き込む画像データ書き込み手段と、2ポートRAM1に書き込まれた画像データをメモリアドレス順に読み出す画像データ読出し手段を具備することで、上記課題を解決する。

(もっと読む)

書込制御装置

【課題】画像データの配列変換のための回路規模を小さくすることのできる書込制御装置を提供する。

【解決手段】画像形成装置の書込光源を制御する書込制御装置であって、予め設定された規則に従い、カウント値を生成する複数のアドレスカウンタ103、104、105と、複数のアドレスカウンタ103、104,105それぞれにより生成されたカウント値を加算して、画像データをメモリに書き込むライトアドレスを生成する加算器106と、ライトアドレスにより指定される領域に画像データを書き込む書込手段と、メモリのアドレス順に、画像データをメモリから読み出すリードアドレスを生成するリードアドレス生成部107と、リードアドレスにしたがいメモリから画像データを読み出す読出手段とを備えた。

(もっと読む)

1 - 20 / 148

[ Back to top ]