Fターム[5B047EA03]の内容

Fターム[5B047EA03]に分類される特許

1 - 20 / 21

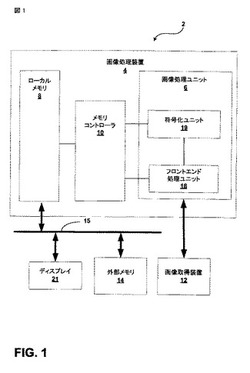

小さな画像又は大きな画像を処理する小さなラインバッファを容易に用いる技術

【課題】異なる大きさの画像の画像処理をサポートするデバイスのために役立つ画像処理技術を提供する。

【解決手段】デバイスによって取得された小さなビューファインダ画像及び大きな静止画像のフロントエンド画像処理のための方法は、デバイスを用いて第1の画像を取得することと、第1の画像の画像幅を収納できる大きさのラインバッファを用いて第1の画像を処理することと、デバイスを用いて、第1の画像の画像幅よりも大きい画像幅を有する第2の画像を取得することとを備える。この方法は、ラインバッファを用いて、ラインバッファ内に収まる幅を定める前記第2の画像の縦縞を処理することも含む。

(もっと読む)

画像読取装置

【課題】画像読取装置において、出力タイプが異なるCISのいずれが設けられたとしても、製造コストを抑えながら、CISからメモリに記憶される各画素データを画素配列順に読み出し、画像への各種処理を正確に実行する。

【解決手段】画像読取装置1は、CIS2から出力される各画素データをCIS2の出力タイプに応じたアドレスに記憶するメモリ3と、記憶制御回路4とを備える。記憶制御回路4は、CIS2の出力タイプ情報を基に、メモリ3から画素データを読み出す方法を変える。これにより、出力タイプが異なるCIS2のいずれが設けられたとしても、メモリ3から各画素データを画素配列順に読み出すことができ、画像への各種処理を正確に実行できる。しかも、画像処理を正確に行えるようにするために、製造の際、CIS2の出力タイプ毎に、CIS2に対応した記憶制御回路を用意する必要がなくなり、従って、部品の共通化を図ることができる。

(もっと読む)

ビット並べ替え回路およびそれを用いた試験装置

【課題】データビットの並べ替え回路の小型化および/または低消費電力化にある。

【解決手段】入力フリップフロップ10は、(m×n)ビットを単位とする入力データDINのうち、連続するmビットを含むワードデータDWDを順次保持する。複数のデコーダ回路DEC1〜mは、ワードデータDWDの各ビットごとに設けられ、それぞれがワードデータの対応するビットおよびその並べ替え後の位置を示す格納先データを受け、(m×n)ビットを有するデコードデータDDECを生成する。デコードデータDDECは、対応するビットが0のとき全ビットが0、対応するビットが1のとき、その並べ替え後の位置に対応するビットが1、残りのビットが0である。メモリ回路20は、(m×n)ビットの記憶領域を含み、m個のデコードデータDDEC1〜mを受け、各デコードデータの1が格納されているビットに対応する記憶領域のビットに1を書き込む。

(もっと読む)

情報処理システム

【課題】メモリ装置をアクセスする複数のマスタに対して、必要なデータを円滑に転送する。

【解決手段】情報処理システムは、メモリ装置(MEM0)と、上記メモリの動作を制御可能なメモリ制御装置(SL0)と、それぞれ上記メモリ制御装置を介して上記メモリ装置へアクセス可能な複数のバスマスタ(MS0〜MS3)とを含む。上記メモリ制御装置は、上記バスマスタからのアクセス要求を保持可能なバッファを含み、上記バッファの利用権を上記バスマスタ毎に設定可能である。

(もっと読む)

画像処理装置及びその制御方法

【課題】入力される画像データに応じて、メモリへの格納方法を変更し、画像処理全体のパフォーマンスを向上させる画像処理装置及びそれらの制御方法を提供する。

【解決手段】本画像処理装置は、当該画像処理装置を統括的に制御するシステム制御部でスキャナ画像処理を行うか、又は、システム制御部の外部でスキャナ画像処理を行うかによって、入力される画像データの格納方法を変更する。具体的には、システム制御部内でスキャナ画像処理を行う場合、入力される画像データは、CCDから直接入力されるため、面順次でメモリに格納される。一方、システム制御部の外部でスキャナ画像処理を行う場合、入力される画像データは、スキャナ画像処理ブロックからの画像データであるため、点順次でメモリに格納される。

(もっと読む)

画像データ処理装置および画像データ処理方法

【課題】メモリ部品内に冗長化分のメモリセルを配置するとメモリ部品が大きくなるという問題などを解決するとともに、ユーザが不良メモリセルによる画素値の異常を視認できない程度に、不良メモリセルによる画素値の異常を殆ど目立たないようにすることができる「画像データ処理装置および画像データ処理方法」を提供する。

【解決手段】ある画素の画素値の書き込みに割り当てられた複数のメモリセルの1つが不良メモリセルであった場合、画素値を示す複数ビットのうち最下位ビットの値を不良メモリセルに割り当てて画素値を複数のメモリセルに書き込むとともに、不良メモリセルに記憶された値を画素値の最下位ビットの値として読み出すようにしている。これにより、メモリ部品内に不良メモリセルが存在していても、不良メモリセルに記憶されるのは、常に、画素値の最下位ビットの値となるようにしている。

(もっと読む)

電子回路、電子機器およびプロジェクタ

【課題】少ない記憶容量で高速に画像データを処理することが可能なプロジェクタ等を提供すること。

【解決手段】プロジェクタ100が、2×m(mは1以上の整数)バイト単位で画像データ142を前段画像処理部120に転送する転送部130と、前段画像処理部120と、を含み、前段画像処理部120が、画像データ142の転送回数を判定する判定部と、画像データ142を記憶する記憶部と、前記転送回数と、当該記憶部に記憶された画像データ142とに基づき、3×n(nは1以上の整数)バイト単位で画像データを後段の画像処理部へ向け出力する出力部とを含んで構成される。

(もっと読む)

画像処理装置、画像処理方法およびコンピュータ読み取り可能な記録媒体

【課題】写真画像の両端領域への編集処理を行うことにより、メモリコントローラを内蔵した汎用CPUのASIC間のバスの転送を効率よく行い、かつ複雑な画像処理をハードウエアにより高速に行うこと。

【解決手段】メインメモリ116に両端画像メモリ領域116cを設け、両端画像を連なるフォーマットとし、画像処理装置112で、両端を含まない画像の処理と、バンド画像メモリ領域116dへの描画と、両端画像の画像処理と、フォーマットでの両端画像メモリ領域116cへの書き込みを行い、CPU101により、両端画像メモリ領域116cの両端画像データのバンド画像メモリ領域116dの写真画像の両端領域への編集処理を行う。

(もっと読む)

画像処理装置

【課題】eDRAM等のバス幅を大きくとることができる内蔵型メモリを利用して、反転や回転を高速に行うことができる。

【解決手段】1アドレスあたりのビット数が、Lを1以上の整数、Mを2以上の整数、Nを2以上の整数として、L×M×Nビット以上である内蔵型のメモリ部と、書き込み側または読み出し側または双方において、Lビットずつを組にして、M×N画素のデータの反転または回転を行うために、同一アドレス内でのビット並び替えを行うビット並び替え部とを備えることを特徴とする。

(もっと読む)

画像処理装置および画像処理方法、並びにプログラム

【課題】データを記憶するメモリに対するアクセス効率を維持しつつ、メモリ帯域を節約し、消費電力と製造コストを削減する。

【解決手段】アドレスキャッシュ128は、デプステスト部125から出力されたワード単位のテクスチャアドレスを含むキャッシュブロックと、テクスチャキャッシュブロック単位アドレス、および、そのキャッシュブロックを構成するワード単位のテクスチャアドレスが、そのテクスチャアドレスに対応するアドレスメモリ104に記憶されているテクスチャアドレスを修正する必要があるテクスチャアドレスであるかどうかをワード単位で表す修正フラグとを対応付けて、一時的に記憶する。本発明は、例えば、GPUに適用することができる。

(もっと読む)

画像データ処理装置およびフレームメモリ

【課題】冗長な記憶セルを使用することなく不良セルによる影響を回避する。

【解決手段】フレームメモリ12内の非周辺部用メモリ領域121に不良セル121Aが存在する場合、その不良セル121Aを含む1ワード分の記憶セルのアドレスを不良アドレスとし、その不良アドレスが外部アドレスによりアクセスされたとき、フレームメモリ12内の周辺部用メモリ領域122の良品の記憶セルである代替セルを含む1ワード分の記憶セルのアドレスを代替アドレスとして、その代替アドレスに変換する。

(もっと読む)

画像形成装置、色変換装置、及び色変換ルックアップテーブルの作成方法

【課題】ルックアップテーブルを参照して色変換処理を行うにあたり、キャッシュヒット率を高め、色変換処理を高速に実行することを目的とする。

【解決手段】色変換ルックアップテーブルを参照して色変換処理を行う色変換処理手段を含む画像形成装置であって、色変換処理手段は、入力信号の信号値を各入力色毎に取得し、各入力色毎の信号値の各下位ビットが、オフセット値計算レジスタの下位ビットに位置するように配置してオフセット値を計算し、当該オフセット値を用いて、色変換ルックアップテーブルを参照する。

(もっと読む)

画像入力装置における信号処理回路

【課題】高速に画像の回転処理を行なうことができる信号処理回路を提供する。

【解決手段】この信号処理回路は、画像入力装置内において撮像素子によって撮像された2次元的に配列された所定単位の単位画像信号と同じビット数の記憶領域を複数備える記憶手段を備え、前記単位画像信号が所定の単位色配列を形成する複数の成分のうちの1成分であり、さらに、前記記憶手段の各記憶領域に記憶された単位画像信号の配列を、前記単位色配列を保ちつつ右に90゜回転させて前記記憶手段の各記憶領域に記憶させるように、前記記憶手段の各記憶領域が互いに接続されている。

(もっと読む)

半導体集積回路及びデータ処理システム

【課題】 RGBデータの色変換に際して中央処理装置の負荷を軽減する。

【解決手段】 半導体集積回路(20)は、1個の半導体基板に中央処理装置(23)及びデータ転送制御装置(26)を有し、前記データ転送制御装置は、前記中央処理装置によって設定された転送制御情報に従って、第1アドレスによって第1外部メモリ(21)からリードしたRGB画素データを第2アドレスに変換し、この第2アドレスを用いて第2外部メモリ(22)をリードすることが可能とされる。第2外部メモリをリードするためのアドレス変換をデータ転送制御装置が行うから、RGBデータの色変換に際して中央処理装置の負荷を軽減することができる。

(もっと読む)

データ変換装置、画像形成装置およびテーブルデータ格納方法

【課題】 時間のかかる外部メモリへのアクセスを高速化し、内部キャッシュを用い、6つの4面体に対応でき、ヒット率を向上させるデータ変換を提供する。

【解決手段】 データ保存として記憶装置(メモリ等)、メモリへアクセスする為のアドレス生成手段(及び又は詳細アドレス演算手段)、メモリから出たデータを保存する為の一次記憶手段(キャッシュ)、メモリアクセス用アドレスと一次記憶手段に入っているデータのアドレスが一致するかを判定する為の判定手段を搭載する。

(もっと読む)

画像処理装置

【課題】メモリを使用して画像回転を行う際に、中間のバッファメモリ量を少なくする。

【解決手段】入力画像データを順次画像メモリ403のデータバス幅nビットのm画素単位にパッキングして前記画像メモリ403の第1の所定領域に書き込む画像入出力DMAC402と、画像入出力DMAC402により画像メモリ403の第1の所定領域に記憶された入力画像データがmライン蓄積された後に、副走査方向に連続してmワード単位で読み出す回転リードDMAC404と、nビット×mワードのバッファメモリを持ち、前記回転リードDMAC404から読み出された主走査n画素×副走査nラインの画像データに対して90°または270°の回転処理を施す回転処理部406と、回転処理部406によって回転した画像データを順次、回転アドレスを発生して画像メモリ403の第2の所定領域に書き込む回転ライトDMAC405と、画像メモリ403への書き込み及び画像メモリ403からの読み出しを時分割で並行して実行するメモリ制御部401とを備えた。

(もっと読む)

データ転置装置および方法

【課題】データ転置の際にメモリのデータ入出力速度を高めることなく、SOM素子などの走査装置の高速動作を行うことが可能なデータ処理方法および装置を提供する。

【解決手段】1フレームがK×Lバイトサイズのデータからなるイメージデータ(横方向:Kバイト、列方向:Lバイト)を横方向に読み取ってK×Nバイト(N≧2)サイズのデータアレイを交互に格納する一対のラインメモリと、前記ラインメモリから前記イメージデータをNバイト単位で交互に受信し、1フレームに相当するデータアレイを格納する一対のメモリと、前記メモリに格納されたデータアレイをNバイト単位で縦方向にアドレシングして外部へ出力する出力部とを備える。

(もっと読む)

ディジタルシグナルプロセッサ

【課題】 WorkRAMの初期化が必要な領域のみについて、周辺回路の規模を大きくせず、複雑な制御も行わず、処理時間の増加も伴わずに初期化することができるディジタルシグナルプロセッサを提供する。

【解決手段】 WorkRAM16は複数のデータを書き換え可能に記憶する。信号処理部6はWorkRAM16から順次データを読み出し、演算処理を行う。論理回路18はWorkRAM16のアドレス信号に同期してゲート回路17a、17b、17cの共通入力端に「1」を出力する。ゲート回路17aはWorkRAM16の入力端Imに強制的にデータ「0」を書き込む。ゲート回路17bはWorkRAM16の入力端WEに書込制御信号として「1」を出力する。ゲート回路17cは信号処理部6内の乗算器11の入力端Xinに出力される信号を「0」に保つ。

(もっと読む)

DRAMメモリアクセス制御手法、および手段

【課題】 複数データ形式を扱うシステムにおいて、データ形式によらずDRAMメモリアクセス時のページミスによるペナルティーを少なくし、システム全体のメモリアクセス速度を向上させる。

【解決手段】 複数のマスタデバイスからのメモリアクセスが可能なシステムで、メモリコントローラと、任意のアクセス単位ごとに規則的に離散的なメモリアクセスを行うマスタデバイスを有するシステムにおいて、マスタデバイスを識別し、規則的かつ離散的なアクセスを判定する手段を有し、アクセスに応じてページミスを予測しあらかじめページオープンを行う手段を有する。

(もっと読む)

画像処理装置

【課題】画像データのミラー処理または回転処理とライン補正とを迅速に行い得る画像処理装置を提供する。

【解決手段】

画像処置装置200は、イメージメモリ215から画像データを取得し、第一の受付部214から転送単位に含まれるライン数を取得し、前記画像データを、前記画像データの一画素に含まれるビット数からなるスワップ単位ごとにスワップし、画像データのアドレスをこのライン数からなる転送単位内でデクリメントしながら、第一のシステムメモリ212に転送する転送制御部218と、第一のシステムメモリ212に記憶されている画像データを取得し、第一の受付部214から上記ライン数を取得し、第二の受付部204からラインギャップ数を取得し、上記ライン数およびラインギャップ数に基づいて画像データをラインからなる領域内で再配列するライン補正部210とを備える。

(もっと読む)

1 - 20 / 21

[ Back to top ]