Fターム[5B047EB11]の内容

Fターム[5B047EB11]の下位に属するFターム

アドレス発生 (156)

アドレス変換 (70)

ワード(バイト)バウンダリ (6)

メモリ割付け (164)

Fターム[5B047EB11]に分類される特許

1 - 16 / 16

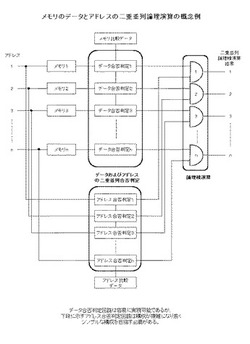

情報絞り込み検出機能を備えたメモリ、その使用方法、このメモリを含む装置。

【課題】

パターン認識など情報検出の最大の課題は検索時間でありメモリの逐次比較処理が不要な非ノイマン型情報検出メモリを実現する。

【解決方法】

メモリアドレスごとに情報を記憶しその情報を読み出し可能なメモリで、このメモリは、外部から与えられる第1のデータは記憶されたメモリのデータを比較するためのデータ、第2のデータはアドレス同士を比較するためのデータ、の双方の入力データの入力手段と、この入力手段から与えられた上記双方の入力データにより記憶された情報のデータと、そのアドレスと、の双方を二重並列に合否判定し、その双方の合否判定結果をさらに並列に論理演算する手段と、上記論理演算に合格するこのメモリの上記アドレスを出力する手段と、を具備することを特徴とする情報絞り込み検出機能を備えたメモリであるのでインテリジェンスな情報検索はもとより人工知能等に広く利用可能である。

(もっと読む)

画像読取装置

【課題】画像読取装置において、出力タイプが異なるCISのいずれが設けられたとしても、製造コストを抑えながら、CISからメモリに記憶される各画素データを画素配列順に読み出し、画像への各種処理を正確に実行する。

【解決手段】画像読取装置1は、CIS2から出力される各画素データをCIS2の出力タイプに応じたアドレスに記憶するメモリ3と、記憶制御回路4とを備える。記憶制御回路4は、CIS2の出力タイプ情報を基に、メモリ3から画素データを読み出す方法を変える。これにより、出力タイプが異なるCIS2のいずれが設けられたとしても、メモリ3から各画素データを画素配列順に読み出すことができ、画像への各種処理を正確に実行できる。しかも、画像処理を正確に行えるようにするために、製造の際、CIS2の出力タイプ毎に、CIS2に対応した記憶制御回路を用意する必要がなくなり、従って、部品の共通化を図ることができる。

(もっと読む)

多次元データを転置することで垂直フィルタと水平フィルタを切替えるためのシステム、データ構造、および方法

【課題】多次元データたとえば画像データをフィルタリングするためのシステム。

【解決手段】プロセッサは、第1データ構造の単一行に水平方向に整列された多次元データ値を結合することで、水平フィルタを実行するための命令を受取ることができる。第2データ構造は、複数の個別アドレス指定可能内部メモリユニットを含んでよい。ロードユニットは、水平方向に整列された値を転置された配列でロードでき、個別アドレス指定可能メモリユニットにおける第2データ構造に、単一列内に垂直方向に整列された値として記憶する。単一列内の転置された各値は、個別アドレス指定可能メモリユニットのそれぞれ互いに異なる一つに別個に記憶され得る。プロセッサは、別個のメモリユニットに独立にアクセスすることで、水平フィルタによって結合用に指定された転置された各値を、独立に操作および結合できる。

(もっと読む)

ビット並べ替え回路およびそれを用いた試験装置

【課題】データビットの並べ替え回路の小型化および/または低消費電力化にある。

【解決手段】入力フリップフロップ10は、(m×n)ビットを単位とする入力データDINのうち、連続するmビットを含むワードデータDWDを順次保持する。複数のデコーダ回路DEC1〜mは、ワードデータDWDの各ビットごとに設けられ、それぞれがワードデータの対応するビットおよびその並べ替え後の位置を示す格納先データを受け、(m×n)ビットを有するデコードデータDDECを生成する。デコードデータDDECは、対応するビットが0のとき全ビットが0、対応するビットが1のとき、その並べ替え後の位置に対応するビットが1、残りのビットが0である。メモリ回路20は、(m×n)ビットの記憶領域を含み、m個のデコードデータDDEC1〜mを受け、各デコードデータの1が格納されているビットに対応する記憶領域のビットに1を書き込む。

(もっと読む)

撮像装置および撮像方法

【課題】画像取り込み時間を短縮した撮像装置および撮像方法を提供することを目的とする。

【解決手段】格子状配置の複数の画素を備えた受光部20によって撮像対象物の画像を読み取る撮像装置において、画像取込エリア情報記憶部28に記憶された画像取込エリアの情報に基づいて画像出力対象となる画素を特定する画素選択情報および画像信号を画像記憶部26に記憶させる際の記憶領域を決定する記憶アドレスを生成し、画素選択情報に基づいて画像信号を出力する画素を選択し、出力される画像信号を記憶アドレスにしたがって画像記憶部26に書き込む。これにより必要な画素の画像信号だけを出力して記憶することができる。

(もっと読む)

照合装置、除去回路及び回路システム

【課題】撮像手段から出力された画像から、不要な画像、例えば汚れ及び皺の画像を除去し、撮像手段にて撮像された画像と予め登録された画像との照合を行う照合装置、撮像手段から出力された画像から不要な画像を確実に除去する除去回路、及び該除去回路を複数備える回路システム、並びに該回路システムを備える照合装置を提供する。

【解決手段】CCD1にて撮像された被写体の画像を該画像の中心を回転中心にして所定角度回転させた画像を回転処理回路34にて生成し、回転前後の両画像の中心を一致させて、回転後の画像の画素と回転前の画像の画素との論路積を論理演算回路35にて求める構成とした。

(もっと読む)

画像処理装置、および画像処理方法、並びにコンピュータ・プログラム

【課題】第1メモリに格納された画像を取得し正規化処理を実行して第2メモリに書き込む構成においてメモリの小型化、正確なメモリ書き込みを実現する。

【解決手段】顔識別処理を行なう画像処理装置において、正規化前の顔画像を蓄える第1メモリ(SRAM1)の画像を取り出して正規化を実行して第2メモリ(SRAM2)に格納する処理を行なう構成において、正規化前の顔画像を蓄える第1メモリ(SRAM1)に顔全体を格納することなく、一部のみを格納する。さらに、第1メモリ(SRAM1)に格納された顔の傾きに応じて、第2メモリに対するデータ書き込み順としてのスキャンシーケンスを変更する。本構成により、小さなメモリの小型化、および正確な正規化画像の書き込みが実現される。

(もっと読む)

画像処理装置

【課題】データ転送の際に効率良くアクセスする。

【解決手段】書き込みアドレス生成部11は、外部から入力される書き込みマクロブロック位置情報204、アドレスオフセット205及びフレームサイズ206に基づき、書き込みデータ208の所定個のマクロブロックをSDRAM2のあるバンクの同一ローアドレスに格納し、画像空間上のあるマクロブロックと斜め方向を含めた隣接するマクロブロックとが、SDRAM2の同一バンクの同一ローアドレス又は異なるバンクに格納するように配置して、SDRAM2のバンク、ロウアドレス及びカラムアドレスからなる書き込みアドレス207を生成する。

(もっと読む)

データのアクセス方法

【課題】コスト増大や処理遅延を招くことなく、不連続な複数の格納領域にデータを書込み、または複数の格納領域からデータを読出すデータのアクセス方法を提供する。

【解決手段】メモリ装置141と、データ書込み手段120、130と、データ読出し手段130、150と、これらを制御、管理するコントローラ17が、バス20、21で接続された画像処理装置1のデータのアクセス方法であって、複数の空領域の先頭アドレス等に基づき、前記データ書込み手段120、130が所定容量の画像データに次の空領域へのリンクアドレスを付加して対応する空領域の先頭アドレスから順に格納する処理を繰り返すデータ書込み処理ステップと、前記データ読出し手段130、150が画像データを読出し、付加されたリンクアドレスに基づいて次の格納領域から画像データを読出す処理を繰り返すデータ読出し処理ステップを備える。

(もっと読む)

画像処理用メモリ

【課題】複数の行、複数の列にまたがるデータを1サイクルでアクセスでき、異なるブロックをまたぐデータをアクセスする場合でも、必要なデータを1サイクルでアクセス可能な画像処理用メモリを提供する。

【解決手段】マトリクス状に配置されたメモリセル群から、行デコーダと列デコーダによりL画素データを同時アクセスするメモリにおいて、行デコーダが全ての行から任意の1〜L行を選択する、マルチワードアクセス回路を備え、メモリセル群が論理的にM×N(行数×列数)の画素データからなるブロック毎に分割され、行デコーダがブロックの異なる連続したL行を選択し、列デコーダがアクセスするブロックの異なるL列を選択して、画像フレーム上における縦方向データにアクセスする。また行デコーダが連続したM行を選択し、列デコーダがアクセスするブロックの異なるL列を選択して、画像フレーム上における横方向データにアクセスする。

(もっと読む)

小さな画像又は大きな画像を処理する小さなラインバッファを容易に用いる技術

本開示は、異なる大きさの画像の画像処理をサポートするデバイスのために役立つ画像処理技術を説明する。この技術は多くの状況において用いられることができ、特に、デバイスによって取得された小さなビューファインダ画像及び大きな静止画像のフロントエンド画像処理のために役立つ。1つの実施形態において、本開示は、デバイスを用いて第1の画像を取得することと、第1の画像の画像幅を収納できる大きさのラインバッファを用いて第1の画像を処理することと、デバイスを用いて、第1の画像の画像幅よりも大きい画像幅を有する第2の画像を取得することとを備える方法を提供する。この方法は、ラインバッファを用いて、ラインバッファ内に収まる幅を定める前記第2の画像の縦縞を処理することも含む。  (もっと読む)

(もっと読む)

バンド単位で画像処理を行う画像処理装置

【課題】 ハードウエアユニットが処理可能な最大バンド幅を超える画像データを,画像処理の効率を低下させずに処理可能な画像処理装置を提供する。

【解決手段】 第1のラスタ数をN(=2)等分した第2のラスタ数(h/2)の単位で順次読み出し,当該読み出した画像データを第1のバンド幅をN(=2)等分した第2のバンド幅(Wb/2)であって第1のラスタ数(h)の画像データとして,画像処理ユニットに順次入力して処理させ,画像処理ユニットにより処理された第2のバンド幅(Wb/2)であって第1のラスタ数(h)の処理済み画像データを,内部メモリに第1のバンド幅(Wb)で第1のラスタ数(h)の画像データとして書き込む。最大バンド幅を超えるバンド幅の画像データを,ラスタ方向にN等分して分割し,ラスタ長さをN等分した画像データとして画像処理ユニットに供給する。画像処理済みの画像データは,合成して元のサイズの画像データにする。

(もっと読む)

画像処理装置および画像処理方法

【課題】 元の画像データの配列と異なるよう画像データが配列された場合においても、画像データのアクセス先を効率よく算出する。

【解決手段】 プロセッサエレメント1は、そのMB参照エリアMEに格納される画像部分について、フレームメモリ3に格納されている画像上での画素の位置を示す座標データを座標管理エリアPEに書き込むとともに、MB参照エリアMEに保持されている画像データへのアクセス先を、座標管理エリアPEに保持されている座標データに対応してマクロブロック単位で参照テーブルTに書き込み、データエレメント8は、読み出し対象となる画素の座標が座標参照エリアDE上で指定されると、読み出し対象となる画素の座標データをメモリコントローラ4に送り、アドレス変換部7は、参照テーブルTを参照することにより、読み出し対象となる画素の座標データをMB参照エリアMEに保持されている画像データへのアクセス先に変換する。

(もっと読む)

データ書き込み装置及び方法、データ読み出し装置及び方法、プログラム、並びに記録媒体

【課題】効率よく画像データを読み出すことができるデータ書き込み装置及び方法、データ読み出し装置及び方法、プログラム、並びに記録媒体を提供する。

【解決手段】アドレス制御部5が、水平方向にN画素及び垂直方向にN画素からなる任意のN×N画素のデータが同一のロウアドレス内で連続するように画像データを画像格納部4に書き込む。

(もっと読む)

画像処理装置及び画像処理方法

【課題】 矩形領域単位の画像データに画像処理を実行する画像処理装置及び方法において、画像処理モードに応じて矩形領域を異ならせることにより、各画像処理モードに応じた適切な画像処理を実行すること。

【解決手段】 画像処理装置は、画像データを入力する入力部と、入力された画像データを記憶する第1メモリと、第1メモリに記憶された画像データを、矩形領域ごとに分割して読み出すためのアドレス情報を生成するアドレス生成部と、アドレス情報に基づいて、画像データを矩形領域単位で第1メモリから読出して第2メモリに転送する転送部と、第2メモリに記憶された矩形領域単位の画像データに対する画像処理を、複数の画像処理モードにかかるいずれかの画像処理モードにて実行する画像処理部と、画像処理部が実行する画像処理モードを設定する設定部とを有し、アドレス生成部は、複数の画像処理モード毎に異なる矩形領域となるようアドレス情報を生成することを特徴とする。

(もっと読む)

DRAMメモリアクセス制御手法、および手段

【課題】 複数データ形式を扱うシステムにおいて、データ形式によらずDRAMメモリアクセス時のページミスによるペナルティーを少なくし、システム全体のメモリアクセス速度を向上させる。

【解決手段】 複数のマスタデバイスからのメモリアクセスが可能なシステムで、メモリコントローラと、任意のアクセス単位ごとに規則的に離散的なメモリアクセスを行うマスタデバイスを有するシステムにおいて、マスタデバイスを識別し、規則的かつ離散的なアクセスを判定する手段を有し、アクセスに応じてページミスを予測しあらかじめページオープンを行う手段を有する。

(もっと読む)

1 - 16 / 16

[ Back to top ]