Fターム[5B048DD01]の内容

デジタル計算機の試験診断 (4,118) | 試験手段 (1,073) | 試験プログラム (222)

Fターム[5B048DD01]の下位に属するFターム

試験プログラムの選択 (24)

試験プログラムの作成 (75)

Fターム[5B048DD01]に分類される特許

1 - 20 / 123

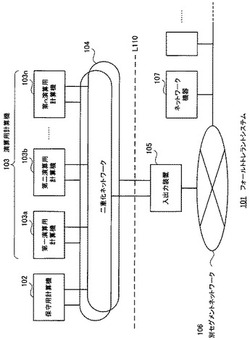

フォールトトレラントシステム

【課題】可用性と信頼性を向上させるために必要なテスト機能を備えるフォールトトレラントシステムを提供する。

【解決手段】保守用計算機102は、指定した演算用計算機103に対し、演算用計算機103に組み込まれている擬似故障処理部302を実行させる命令を、プログラム起動制御部204から送信する。入出力制御部203は、同期検出部205が演算用計算機103の同期が外れたことを確認したことを受けて、演算用計算機103の再組み込み処理部303に再組み込みを指示する。その後、入出力制御部203は、同期検出部205が演算用計算機103の再組み込み処理が失敗したことを確認したら、ログ記録部305を通じてログファイル307からエラーログを収集する。以上の一連の動作は、テスト機能制御テーブル206に記載された内容に従って、各演算用計算機103に対して繰り返し実行される。このため、効率よくエラーログを収集できる。

(もっと読む)

サポートシステム

【課題】携帯端末を介して容易にユーザ端末の障害を解消する技術を提供する。

【解決手段】通信回線を介して接続するサーバと携帯端末を有するサポートシステムにおいて、サーバが、ユーザ端末の診断処理を行う診断用アプリケーションを携帯端末に送信し、診断用アプリケーションによる診断結果を携帯端末から受信し、携帯端末から受信した診断結果と対応する修正の処理手順を修正手順記憶部から抽出し、当該修正の処理手順を実行する修正用アプリケーションを生成し、修正用アプリケーションを携帯端末に送信し、携帯端末が、サーバから診断用アプリケーションを受信し、ユーザ端末との接続制御部を介して診断用アプリケーションをユーザ端末に提供し、ユーザ端末が診断用アプリケーションを実行した結果を診断結果として取得し、サーバに送信し、サーバから修正用アプリケーションを受信し、当該修正用アプリケーションをユーザ端末に提供する。

(もっと読む)

仮想化技術を使用した情報処理装置検査の分散化方式

【課題】情報処理装置の検査において、物理サーバや外部のネットワーク環境に依存せず、分散した環境において、検査対象装置に対し、検査プログラムを組み込むシステムを提供する。

【解決手段】検査対象装置をコントロールする操作端末装置上に端末機能と、仮想化記述を用いた仮想サーバ機能の2種類の機能を構築し、端末機能からのコントロールにより、検査装置が仮想サーバ環境から検査プログラムを取得・実行し、検査端末装置、操作端末装置の2台の装置のみで検査環境を完結させることにより、物理サーバへの依存を廃し、環境に依存しないシステムを提供する。

(もっと読む)

ネットワーク端末故障対応システム、端末装置、サーバ装置、ネットワーク端末故障対応方法及びプログラム

【課題】 ネットワーク端末の様々な故障に柔軟に対応し、誰でも手軽に使いこせるネットワーク端末の故障対応技術を提供する。

【解決手段】 端末装置102は、プログラム制御方式の制御手段103、制御手段の動作異常を検出する検出手段104、制御手段103の動作異常が検出されたときにその異常の内容を示す異常情報をサーバ装置101に宛てて送信する異常情報送信手段105、サーバ装置101から返送されるプログラムを受信するプログラム受信手段106、受信されたプログラムで制御手段103のプログラムを書き換える書き換え手段107を備え、サーバ装置101は、異常情報を分析する分析手段108、分析結果に基づいて異常の内容に応じた修正用のプログラムを読み出す読み出し手段110、読み出されたプログラムを端末装置102宛てに送信するプログラム送信手段111を備える。

(もっと読む)

多コア・プロセッサによる信頼できるコンピューティング

【課題】多コア・プロセッサの寿命の間に、多コア・プロセッサ中のコアのパフォーマンスを定期的に試験し、得られた試験データを、アプリケーションのパフォーマンスを改善するするために使う。

【解決手段】多コア・プロセッサ中のコアは、最大動作周波数、電力消費、電力リーク、機能的な正しさおよびその他のパラメータについての傾向情報を含む動的プロファイルを取得するために定期的に試験される。各コアについて動的プロファイルが生成されたら、多コア・プロセッサ中のコアはその特性に従って種々のビンにグルーピングされる。動的プロファイルおよび前記グルーピング情報に基づき、オペレーティング・システム(OS)または他のソフトウェアは、タスクを、そのタスクのために最も好適なコアに割り当てる。選択された諸コアの間での高いレベルの接続性を保証するよう、多コア・プロセッサ中の相互接続ファブリックが再構成される。

(もっと読む)

マルチスレッド・プロセッサ

【課題】複数の命令実行手段を備えるマルチスレッド・プロセッサにおいて、命令実行手段の正確な機能チェックを行うこと。

【解決手段】複数のスレッドがハードウエア・マルチスレッディング処理を行うマルチスレッド・プロセッサであって、前記複数のスレッドによって使用可能な、演算器その他の複数の命令実行手段と、前記複数の命令実行手段に対して前記複数のスレッドのいずれかに属する命令を発行すると共に、所定のタイミングで前記複数の命令実行手段の機能チェック用命令と該機能チェック用命令が正しく実行されたか否かを確認する確認用命令を発行する命令発行手段と、前記命令発行手段が前記機能チェック用命令を発行する際と、前記確認用命令を発行する際とで前記複数の命令実行手段のうち異なる命令実行手段に命令を発行するように前記命令発行手段を制御する制御手段と、を備えるマルチスレッド・プロセッサ。

(もっと読む)

試験プログラムおよび試験方法

【課題】任意のハードウェア構成を有する対象装置についてハードウェア構成に応じた負荷変動試験を実施することができる試験プログラムおよび試験方法を提供する。

【解決手段】上記対象装置のハードウェア構成を確認する構成確認処理と、構成確認処理で確認されたハードウェア構成に基づいて、このハードウェア構成に含まれている各ハードウェア要素に対する負荷の変動パターンを決定する決定処理と、構成確認処理で確認されたハードウェア構成に含まれている各ハードウェア要素を、決定処理で決定された変動パターンで動作させる動作処理と、動作処理での各ハードウェア要素の動作が正常であるか否かを確認する動作確認処理とを有する。

(もっと読む)

デジタル制御装置およびその実行方法

【課題】 簡易な構成でテストモード時に用いるコードが通常モードにおける処理に影響を及ぼすことを防ぐデジタル制御装置の提供を目的とする。

【解決手段】 デジタル制御装置1は、モードスイッチ3と、基本処理コード14およびテスト処理コード15ならびにアプリ処理コード16を格納するコード格納装置4と、メインメモリ5と、コード格納装置4からメインメモリ5へ転送すべきコードを示すブート処理コード13を格納するブート処理コード格納メモリ8と、ブート処理を行う演算部2とを備え、演算部2は、モードスイッチ3において通常モードが選択されたときは、基本処理コード14およびアプリ処理コード16をメインメモリ5に転送させ、制御対象機器10の通常処理を行い、モードスイッチ3においてテストモードが選択されたときは、基本処理コード14およびテスト処理コード14をメインメモリ5に転送させ、制御対象機器10のテスト処理を行う。

(もっと読む)

プロセッサ検証プログラム

【課題】プロセッサ検証時におけるパイプラインステージの検証すべき処理状態の生成に係る制御を自動化したプロセッサ検証プログラムを提供することにある。

【解決手段】 プロセッサの検証処理をコンピューターに実行させるコンピューター読み取り可能なプロセッサ検証プログラムにおいて、検証処理は、テスト命令列内の命令がパイプラインステージそれぞれで処理中か否かを示しパイプラインステージの検証すべき処理状態を規定するパイプラインステージ組合せパターンを参照し、テスト命令列の命令を実行するとき、パイプラインステージそれぞれで命令が処理中か否かを示すステータス情報に基づいてインターロック信号をパイプラインステージに供給することにより、パイプラインステージの命令の処理状態をパイプラインステージ組合せパターンと一致させるタイミング生成工程を有する。

(もっと読む)

電源スイッチ押下装置、電源スイッチ押下方法およびプログラム

【課題】電源オン/オフ機能を実現するソフトウェアを具備しないメインボードに対して、加工を必要とせずに、起動および停止の繰り返しを行う際の検査者の負担を軽減することができるようにする。

【解決手段】USB通信部130が、被検査コンピュータ300のシャットダウンを検出し、このシャットダウン検出に基づいて、スイッチ押アーム200が電源スイッチ359を押下する。これにより、電源オン/オフ機能を実現するソフトウェアを具備しないメインボード(処理部350)に対して、加工を必要とせずに、被検査コンピュータ300の起動および停止を自動で繰り返すことができるので、検査者の負担を軽減することができる。

(もっと読む)

装置検証プログラム,性能測定方法及び性能測定装置

【課題】システム内の制御部間で負荷分散を行なうシステムにおいて、個々の制御部に負荷を容易に与えられるようにして、負荷検証の信頼性の向上を実現する。

【解決手段】記憶部のアクセス対象のアドレスを設定されるアドレス領域と当該アクセス対象へのアクセスを制御する一の制御部を複数の制御部の中から指定する指定情報を設定される指定領域とを含むアドレス情報における指定領域を推定し、推定された指定領域における指定情報に基づいて記憶部に対するアクセスを行ない、システムの負荷時の信頼性を検証する。

(もっと読む)

競合試験装置

【課題】本発明の一実施例では、擬似アクセス信号発生手段を設けることなく、確実にアクセス競合を発生させる競合試験装置を提供することを目的とする。

【解決手段】プログラムを記憶する記憶部と、該記憶部に記憶されたプログラムを読み出し、読み出した該プログラムを実行する第1および第2の演算部と、該記憶部の同一アドレス空間に同時になされた読み出し要求に対するプログラムの転送処理を調停し調停結果を出力する調停部とを有する演算装置のアクセス競合試験を行う競合試験装置は、該記憶部の奇数個のアドレス空間にそれぞれ該調停部の調停動作を試験する試験プログラムを記憶させ、該記憶部に記憶された複数の試験プログラムを所定の順序に従って該第1の演算部に読み出させ、該記憶部に記憶された複数の試験プログラムを該所定の順序と逆の順序に従って該第2の演算部に読み出させ、該調停部の調停結果を記録する。

(もっと読む)

半導体回路およびそのテスト方法

【課題】効率よくテストを行うことが可能な半導体回路およびそのテスト方法を提供する。

【解決手段】半導体回路のテスト方法は、まず、少なくとも1つの引数と、テスト対象の半導体回路のテストを行うためのテストプログラムとを含むテストパタンの基本フォーマットを生成し、テスト装置内に記憶する。次に、前記引数に所定の値を設定して、前記テストプログラムおよび前記所定の値が設定された引数を含むテストパタンを生成し、前記テスト対象の半導体回路に供給する。次に、前記テストプログラムを前記半導体回路内に設けられる記憶部の第1のアドレスに格納し、かつ、前記所定の値が設定された引数を前記記憶部の第2のアドレスに格納する。さらに、前記第2のアドレスに格納された引数を参照しつつ、前記第1のアドレスに格納された前記テストプログラムを実行する。

(もっと読む)

半導体装置および半導体装置の動作試験方法

【課題】ROMに試験用プログラムを記憶させることができない場合にも初期動作の試験が可能な半導体装置の実現。

【解決手段】CPUコア11と、ROM13と、RAM14と、アドレス信号をデコードして、ROMまたはRAMの選択信号を発生するROM/RAM選択アドレスデコーダ15と、スタンバイ制御回路19と、RAM、ROM/RAM選択アドレスデコーダおよびスタンバイ制御回路の電源を、通常電源とバックアップ電源の間で切り替えるバックアップ電源切換機構と、を備え、スタンバイ制御回路は、スタンバイモードから通常動作状態に変化すると、CPUコアがROMの替わりにRAMをアクセスするように、ROM/RAM選択アドレスデコーダを設定可能であり、CPUコアがRAMに記憶された初期動作プログラムにしたがって起動動作を実行可能である。

(もっと読む)

コンピュータシステム及び周辺装置の検証方法

【課題】外部記憶装置の容量と与えられた試験時間または最大データ転送量とにより試験を実施するプロセスの数を変動させ、周辺装置の検証を効率的に行う。

【解決手段】検証プログラム506は、例えば、選択された外部記憶装置505に対して、最初に、1プロセスによる一定の短時間、例えば、1分間だけ試験を行う。この短時間の試験の終了後、検証プログラムは、短時間の試験で試験が完了した容量と、選択された外部記憶装置の容量(指定された開始アドレス、終了アドレスにより決まる容量)とから指定された試験時間とにより、試験時間内で試験を終了することができるプロセス数を求め、次に、求められた複数のプロセスのそれぞれに試験が完了していない残りの試験対象領域を割り当てて、それらのプロセスを用いて一定の短時間、例えば、1分間だけ試験を行うことを、指定された外部記憶装置の容量の全ての試験が完了するまで繰り返す。

(もっと読む)

コンピュータ装置のシステムヘルス及びパフォーマンスのケア

コンピュータ装置のシステムケアのためのシステム及びコンピュータプログラム製品を提供する。1つの実施形態では、処理が、コンピュータ装置のシステムケアプログラムによって、コンピュータ装置の1又はそれ以上のソフトウェア及びハードウェアコンポーネントを分析するステップと、1又はそれ以上のソフトウェア及びハードウェアコンポーネントの状態及び設定の少なくとも一方に基づいて、1又はそれ以上のソフトウェア及びハードウェアコンポーネントに基づくコンピュータ装置のシステムヘルスを分析するステップと、1又はそれ以上のソフトウェア及びハードウェアコンポーネントの署名プロファイルに基づいて、1又はそれ以上のソフトウェア及びハードウェアコンポーネントに基づくコンピュータ装置のパフォーマンスを分析するステップとを含む。この処理はまた、コンピュータ装置のシステムヘルス及びパフォーマンスに基づいて、システムケアプログラムによりコンピュータ装置ための1又はそれ以上の解決策を決定するステップと、1又はそれ以上の解決策を含むレポートを表示するステップとを含むこともできる。 (もっと読む)

処理システムおよび試験装置

【課題】複数の動作部が並列に命令データを処理する処理システムにおいて、各動作部が異常状態となった場合に、他の動作部への影響を排除する。

【解決手段】複数の動作部に対する命令データを受信して格納する共通バッファと、共通バッファが格納した命令データを順次読み出して、対応する動作部に順次振り分けて伝送し、且つ、いずれかの動作部へ命令データを伝送できず、共通バッファから当該命令データを削除できない場合に、当該動作部に代わって当該命令データに応じた処理を行い、共通バッファから当該命令データを削除する振分部とを備える処理システムを提供する。

(もっと読む)

車両故障判定装置、車両故障判定装置設計プログラム

【課題】各車両の仕様に柔軟に対応することのできる車両故障判定装置、およびその車両故障判定装置を設計するプログラムを提供する。

【解決手段】本発明に係る車両故障判定装置では、各故障診断プログラム、その故障診断プログラムを実行する際に用いられる制御データ、および各故障診断プログラムの診断結果データの対応順序を、故障診断プログラムとは別に独立して定義する。また、本発明に係る車両故障判定装置設計プログラムは、故障診断項目となり得る全ての項目を記述した総診断項目リストから、必要なる故障診断項目を抽出する。

(もっと読む)

ディスプレイ上にセーフティ関連情報の表示をする方法、及びその方法を適用する装置

セーフティ関連情報の信頼度の高い表示を保障する高効率で安全な方法、特にピクセルに基づく視覚化を実現する。一以上の入力パラメータをプロセッサに入力し、入力パラメータを画像データ列に変換する計算過程を経て、ディスプレイに画像データ列を送信し、表示する。テストユニットへ画像データ列を供給し、画像データ列のためにテストコードを計算して求め、セーフティテストを行う。テストコードと現存の各参照コードとが比較される。特定参照コードを入力パラメータに対応する可能値に割り当て、肯定テスト結果または否定テスト結果をいずれかを生じさせ、セーフティフォーカス応答を開始するために、参照値と入力パラメータ値とが比較される。

(もっと読む)

半導体集積回路及び半導体集積回路の故障診断方法

【課題】CPUのパフォーマンスに影響を及ぼすことなく、故障診断を行うことを可能にする半導体集積回路を提供する。

【解決手段】通常動作において利用される第1のバスBUSA、及びそれとは異なる第2のバスBUSAに接続されたCPU1から第2のバスを介して出力される診断情報に基づいて、診断マクロ6が誤り検出情報を求め、プログラムの実行に応じて求められた最終の誤り検出情報と保持している1つの期待値との比較によりCPUが故障しているか否かを判定するようにして、通常動作に利用される第1のバスの負荷を増加させずに、故障診断を行えるようにする。

(もっと読む)

1 - 20 / 123

[ Back to top ]