Fターム[5B060CD03]の内容

メモリシステム (7,345) | アクセス要求制御 (450) | リクエストバッファ(キュー)管理 (123) | 要求のバッファ内順序管理 (64)

Fターム[5B060CD03]の下位に属するFターム

順序変更、優先制御 (31)

要求合成、要求結合 (12)

要求無効化、要求キャンセル (4)

Fターム[5B060CD03]に分類される特許

1 - 17 / 17

データ書き込み装置およびデータ書き込み方法

【課題】優先度の異なるデータの書き込み処理の処理能力の低下や処理速度の低下を防ぎつつ、優先度の高いデータをより迅速に不揮発性メモリに書き込む。

【解決手段】書き込みデータ優先度判定部6はデータに付与された優先度を判定し、高い優先度が付与されたデータをこの高い優先度に対応する第1のキュー2aに出力するとともに、低い優先度が付与されたデータをこの低い優先度に対応する第2のキュー2bに出力する。そして、書き込みデータ選択処理部11は、最初に第1のキュー2aに登録された優先度の高いすべてのデータを順に選択してEEPROM3に書き込むとともに、第1のキュー2aにデータがなくなったとき、第2のキュー2bに登録された優先度の低いすべてのデータを順に選択してEEPROM3に書き込む。

(もっと読む)

メモリシステムおよびメモリシステムの制御方法

【課題】従来に比して、ホスト装置とSSDとの間で転送されるデータを一時的に格納するバッファを削減しながら、データ転送のスループットを高めることができるメモリシステムを提供する。

【解決手段】実施形態によれば、メモリシステム20は、揮発性メモリと、NANDメモリ30と、コマンドキュー420と、アドレス情報キャッシュ461と、コントローラと、を備える。コントローラは、ホスト装置からコマンドの実行時に、コマンドの実行に使用するアドレス管理情報をNANDメモリ30からアドレス情報キャッシュ461に読み出して、NANDメモリ30に対してリード/ライトを実行する。また、コントローラは、コマンドキュー420に格納されたリードコマンドのうち、1つのリードコマンドに含まれるアクセス先のすべてが揮発性アドレス管理情報に存在するリードコマンドから優先的に実行するようにリオーダ制御する。

(もっと読む)

インターコネクト内の低減されたレイテンシのバリアトランザクション要求

データ処理装置のためのインターコネクト回路機構が開示される。このインターコネクト回路機構は、少なくとも1つのイニシエータデバイスが、少なくとも1つの受信デバイスにアクセスする際に経由することができる、データルートを提供するように構成され、このインターコネクト回路機構は、少なくとも1つのイニシエータデバイスからトランザクション要求を受信するための、少なくとも1つの入力と、少なくとも1つの受信デバイスにトランザクション要求を出力するための、少なくとも1つの出力と、少なくとも1つの入力と少なくとも1つの出力との間でトランザクション要求を送信するための、少なくとも1つの経路と、受信されたトランザクション要求を、少なくとも1つの入力から少なくとも1つの出力へルーティングするための制御回路機構とを含み、この制御回路機構が、バリアトランザクション要求に応答して、少なくとも1つの経路のうちの1つに沿って通過するトランザクション要求のストリーム内部のバリアトランザクション要求に対しての、少なくとも一部のトランザクション要求の順序付けを、トランザクション要求のストリーム内のバリアトランザクション要求の後に発生する少なくとも一部のトランザクション要求に対しての、トランザクション要求のストリーム内のバリアトランザクション要求の前に発生する少なくとも一部のトランザクション要求の順序変更を許可しないことによって、維持するように構成され、この制御回路機構が、応答信号生成器を含み、この応答信号生成器は、バリアトランザクション要求の受信に応答して、応答信号を発行し、この応答信号は、バリアトランザクション要求に応答して遅延されたいずれかのトランザクション要求が更に先へ送信され得ることを、上流のブロッキング回路機構に指示する。  (もっと読む)

(もっと読む)

メモリ制御装置およびメモリアクセス制御方法

【課題】メモリ制御装置における回路規模を抑制しつつ、データの転送効率を改善する。

【解決手段】バンク状態情報生成部310は、選択部390から出力されたアクセス要求に基づいて、メモリシステム500においてビジー状態にあるバンクのバンクアドレスおよびロウアドレスを示すバンク状態情報を生成する。リクエストマスク判定部360は、バスクライアント110乃至140からのリクエスト情報と、バンク状態情報とが同一のバンクアドレスを示し、かつ、互いに異なるロウアドレスを示す場合にはマスク信号を生成する。この場合においても、リクエストマスク判定部360は、待機時間計測部350からのリクエスト情報の待機時間が一定の閾値を超えた場合にはマスク信号を解除する。リクエストマスク処理部370は、リクエスト情報を選択部390に出力することをマスク信号に基づいて抑制する。

(もっと読む)

メモリシステムおよびそのアクセス制御方法、並びにプログラム

【課題】システム全体の最適化を図れ、他マスタからのアクセスリクエストをマスクする機関を適切に設定することができ、同一バンクでかつ同一ページのアクセスに対しての連続アクセスの効率化を図れ、しかも特定のバスへの接続時における修正が必ずしも必要としないメモリシステムおよびそのアクセス制御方法、並びにプログラムを提供する。

【解決手段】メモリシステム10は、メモリコントローラ13がメモリ11の各バンクのページオープン情報を含むバンク情報、リクエストキュー15内のリクエスト情報であるバンク、ロウ、リードライト等の情報をバス上のアービタ17に通知する。そして、アービタ17は、マスタ群14の各マスタから並列に発行されるリクエストをアービトレーションしメモリコントローラ13に送信する。

(もっと読む)

共有メモリの制御回路、制御方法及び制御プログラム

【課題】複数のプロセッサが存在する環境下での並列通信処理でも、プロセッサ間のデータ通信量を削減でき、低消費電力を達成しつつ、順序を意識した共有リソース排他制御を行うことができるようにする。

【解決手段】アクセス調停部5は、メモリアクセスのリクエスト53を受信する度に、アクセス対象の領域が期待する順序番号とアクセス対象の領域の待ち行列識別子をブロックプロパティメモリ3から読み出し、そのリクエスト53に記載された順序番号と期待する順序番号が一致していれば、そのリクエスト53を実行する。一方、一致していなければ、そのリクエスト53を待ち行列識別子が指す待ち行列メモリ4内の待ち行列に退避させる。アクセス調停部5は、待ち行列識別子が指す待ち行列に保存されたリクエスト53に記載されている順序番号と期待する順序番号とが一致し続ける限り、アクセス要求を待ち行列から連続的に取り出して実行する。

(もっと読む)

メモリコントローラ及びその制御方法

【課題】 メモリデータバス上の効率を改善する。

【解決手段】 アクセスサイクルの異なる複数のメモリデバイスにデータの読み書きを行うメモリコントローラにおいて、複数のメモリデバイスに対するメモリアクセス要求を保持する。保持されたメモリアクセス要求をメモリデバイスに発行する際に、メモリコントローラと各メモリデバイスとの間の配線遅延を示す配線遅延情報に基づき、メモリアクセス要求を発行する順序を制御する。

(もっと読む)

コマンド選択のメモリ・コントローラ読み取りキュー動的最適化

【課題】コンピュータ・システムにおけるメモリ・アクセスを改善するための方法および装置を提供する。

【解決手段】メモリ・コントローラは、プロセッサからの読み取り要求を読み取りキュー中に受信する。メモリ・コントローラは、読み取りキュー中に待ち状態の要求がいくつあるかに基づいて、要求にサービスする順序を動的に修正する。読み取りキューが比較的空いている場合、要求は、待ち時間を最小にするために最も古いものが最初にサービスされる。読み取りキューがより満たされると、要求は、または、読み取りキューが徐々に満たされると、3つ以上のメモリ・アクセス・モードを用いて、徐々に要求は、読み取りキューが満杯になりプロセッサからのさらなる要求が停止されなければならなくなる可能性を低減するためにメモリ・バス上のスループットを最大化する仕方でサービスされる。

(もっと読む)

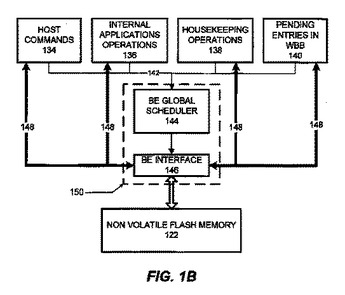

フラッシュメモリシステムにおける段階的ガーベッジコレクションおよびハウスキーピング操作

不揮発性メモリストレージシステムの一実施形態は、メモリコントローラとフラッシュメモリモジュールとを備える。メモリコントローラはフラッシュメモリモジュールの蓄積操作を管理する。メモリコントローラは、ストレージシステムへ結合されたホストから受信される1種類以上のコマンドの優先度より高い優先度を、1種類以上のハウスキーピング操作に割り当て、かつフラッシュメモリモジュールに求められる全操作を優先順位に従い処理するように構成される。  (もっと読む)

(もっと読む)

デバイスへ向けられたメモリ・バリア

共有メモリ・システムにおいて性能を高め、電力要求を低減するために、バス・トランザクションの同期を制御する効率的な技術が記載される。性能を高め電力使用を低減するために、バス・マスタと共有メモリ・デバイスとの間の効率的なデータ転送を提供する複雑な処理システムにおける相互接続構成もまた記載される。一例において、遠隔デバイスへのバス・トランザクションの同期を制御する方法が取り扱われる。デバイスへ向けられたメモリ・バリア・コマンドが受信される。デバイスへ向けられたメモリ・バリア・コマンドは、1または複数の宛先デバイスを決定するために復号される。この復号に応答して、メモリ・バリア・コマンドが、1または複数の宛先デバイスへ選択的にルーティングされる。記載された技術は、高速なデバイスへ向けられたメモリ・バリア機能、向上したバス帯域幅機能、および節電機能を組み合わせる。  (もっと読む)

(もっと読む)

データ処理装置及びデータ処理方法

【課題】多くのマスターが同時動作し、バンク割り当てによる対策だけでは性能が得られない場合にも、メモリオーバーヘッドを減らす。

【解決手段】各トランザクションはマスターIDとグループビットをもっている。グループビットは、グループ化に対応していないマスターの要求するトランザクションでは常に0であり、グループ化に対応しているマスターの要求するトランザクションではグループ化された複数のトランザクションのうちグループの末尾以外では1、グループの末尾では0の値をとる。グループビットはグループ化部104で付与され複数のトランザクションをグループ化する。メモリコントローラ105はグループビットの値によって単独キュー109とグループキュー110の2つのキューのうち一方にトランザクションをいれ、SDRAM107へアクセスする際に制御部112がグループ化された複数のトランザクションを連続して取り出すよう制御する。

(もっと読む)

マルチプロセッサシステム及び入出力制御装置並びにリクエスト発行方法

【課題】マルチプロセッサシステムにおいて、アドレス一致先行ライトリクエストが存在するか否かを判定するための判定処理によって、後続のリクエストの処理が待たされないようにする。

【解決手段】アドレス一致先行ライトリクエスト検出処理部23は、入力バッファ21の入力側において、外部から入力されるリクエストに対するアドレス一致先行ライトリクエストが存在するか否かを調べ、入力バッファ21に登録された上記リクエストに対応付けて、アドレス一致先行ライトリクエストが存在するか否かを示すアドレス一致情報22を登録する。登録処理部27は、アドレス一致情報が登録されるまで、入力バッファ21に登録されているリクエストの出力(順序保証バッファ28への登録)を待ち合わせる。

(もっと読む)

メモリ処理装置

【課題】 リフレッシュ操作の必要なメモリ処理装置において、データ転送レートを低下させることなく効率的にリフレッシュ操作を行う。

【解決手段】 CPU1、データ取り込みコントローラ2、データ表示コントローラ3、信号処理プロセッサ4はメモリコントローラ5に対してアクセスすべきメモリのアドレス情報を転送すべきデータに先立って送信する。メモリコントローラ4は、アドレス情報とリフレッシュ要求をともにアクセスキューにキューイングする。アービターはアドレス情報とリフレッシュ要求が同時に発生した場合、リフレッシュ要求を優先的にキューイングさせ、アドレス情報のみが発生した場合、すでにキューイングされているリフレッシュ要求を追い越すようにアドレス情報をキューイングする。

(もっと読む)

メモリアクセス制御方式と方法、及び共有メモリアクセス制御方式と方法

【課題】 従来のバンクチェック及び追い越し制御によるメモリアクセス方式では複数のバンクグループを同時アクセスできるメモリモジュールの性能を引き出せなかった。

【解決手段】 メモリモジュールを複数バンク構成とし、複数のバンクを偶数バンク、奇数バンクの2グループに分けて制御するメモリアクセス制御方式で、各バンクグループ毎のメモリ制御手段2−1,2−2と、バンク追い越し回路1を含み、バンク追い越し回路1は、バンク毎のバンクビジーカウンタと、アクセス先バンクがビジーか、定められた選択条件に合致しないメモリリクエストを格納するリクエストバッファと、これに格納された或いは新たに受信したメモリリクエストについて、アクセス先バンクのビジー状態を、チェックし、バンクがビジー状態でなくなったメモリリクエストの一つを、奇数/偶数のバンクグループ毎に選択しそれぞれ対応のメモリ制御手段に発行する手段とを具備する。

(もっと読む)

マルチ・ポート・メモリ・ユニットを持つSIMDプロセッサ

単一命令マルチプル・データ・プロセッサでの使用のための複数の単一ポート・メモリが提供される。これらは、複数の単一ポート・メモリへの同時アクセスを持ったマルチ・ポート・メモリとして作動可能である。本装置は、複数のメモリ位置のためのアクセス・リクエストを、既知の順序で、位置に送るために作動可能である。このリクエストは次に、単一ポート・メモリへのアプリケーションのために適したように、再オーダーされる。メモリは次に、アクセスされ、データは、アクセス・リクエスト・フォーマットに適合させるために再オーダーされる。  (もっと読む)

(もっと読む)

メモリアクセス装置及び方法

【課題】 個別にメモリ等を用意しなくとも、性能を落とさずに転送効率及び応答性の両立を図ったメモリアクセス装置を提供する。

【解決手段】 コーデック及びCPU(Central Processing Unit)等のようなマスターデバイスからのメモリに対するアクセスを制御するコマンドに基づいてDRAM(Dynamic Random Access Memory)等のようなメモリに対するアクセスを行うDRAMインターフェース部70と、コーデック等のような転送効率を重視するマスターデバイスからのメモリに対するアクセスを制御するコマンドよりも、CPU等のような応答性を重視するマスターデバイスからのメモリに対するアクセスを制御するコマンドを優先してDRAMインターフェース部70に出力するか否かを選択する選択部50とを備える。

(もっと読む)

効率的なメモリ制御装置

効率的なメモリ制御装置12である。制御装置12は1以上の入力コマンドシーケンスを1以上の対応する値に関連付けるための第1の機構18、28を含んでいる。第2の機構20、32は信号に応答して、選択的に1以上のコマンドシーケンスの1つをメモリ16へ順序付ける。第3の機構30は1以上の値のそれぞれを第2の機構20、32の状態と比較し、それに応答して信号を提供する。特定の実施形態では、1以上の対応する値は実行時間コード値であり、第2の機構20、32は第2の機構20、32の状態をシーケンサ時間コードとして提供するシーケンサ状態マシン32を含んでいる。特定の実施形態では、比較モジュール30は次に利用可能なコマンドシーケンスおよび実行時間コード対に関連する時間コードとシーケンサ時間コードとを比較し、それに応答して信号を提供する。 (もっと読む)

1 - 17 / 17

[ Back to top ]